Устройство для управления транзисторным инвертором

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистимеских

Республик »663066

К ABTOPCNOAAY СВИДВтЕЛЬСТВЮ (61) Дополнительное к авт. свид-ву (22) Заявлено 10.03.77 (21) 2460419/24-07 с присоединением заявки №вЂ” (23) Приоритет—

Опубликовано 15.05.79. Бюллетень № 18 (51) М. К.

Н 02 P 13/18

Государственный комитет

СССР по делам изобретений н открытий (53) УДК 621.314. . 14:621.382.3 (088.8) Дата опубликования описания 20.05.79 (72) Авторы изобретения

А. В. Кобзев, В. Ф. Кощевец и Б. И. Коновалов

Научно-исследовательский институт автоматики и электромеханики при Томском институте автоматизированных систем управления и радиоэлектроники (71) Заявитель (54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ТРАНЗИСТОРНЫМ

ИНВЕРТОРОМ

Изобретение относится к преобразовательной технике и может быть использовано для управления транзисторным инвертором.

Известны устройства для управления транзисторными инверторами, в которых в базовую цепь каждого транзистора включен дроссель насыщения, зашунтированный полупроводниковым диодом (1). Это позволяет получить задержку отпирающего сигнала на время рассасывания избыточных носителей базы транзистора.

Однако, эти устройства не осуществляют форсированного включения транзисторов, требуют дополнительных затрат мощности управления, а фронт сигнала управления определяется параметрами реактивных элементов, вводимых в цепи без транзисторов. !

Другие известные устройства, построенные по принципу несимметричного управления, обеспечивают задержку отпирающего сигнала на время рассасывания избыточных носителей без дополнительных затрат мощ,ности не искажая фронта сигнала управления (2).

Однако такое устройство является сложным, содержит большое количество логических схем и так же не обеспечивает форсированного запирания транзисторов при переключении.

Наиболее близким по технической сущности к предлагаемому изобретению является устройство для управления транзисторным инвертором, в котором параллельно первичной обмотке трансформатора задающего генератора через резистор подключены пер1ч вичные обмотки двух насыщающихся трансформаторов, а вторичные — введены в цепи баз транзисторов инвертора так, что напряжение на обмотках задающего генератора и насыщающихся трансформаторов направлены встречно, что позволяет обеспечить задержку включения силовых транзисторов инвертора (3).

Схема управления описанного инвертора обладает рядом недостатков. Включение силовых транзисторов инвертора происходит зо по заднему фронту блокирующего импульса насыщающегося трансформатора, но, как известно, этот фронт имеет малую крутизну.

Включение параллельно первичной обмотке трансформатора задающего генератора на663066

Э сыщающихся трансформаторов так же ухудшает фронты импульсов управления и дополнительно нагружает транзисторы задающего генератора. Форма сигнала, снимаемого с выходных обмоток насыщающихся трансформаторов, зависит только от параметров этих трансформаторов, поэтому длительности по лупериодов сигнала управления транзисторами инвертора будут не одинаковы, что приведет к несимметриии напряжения в положительный и отрицательный полупериоды на первичной обмотке силового трансформатора, а, следовательно, и к замагничиванию его сердечника. Величйна времени задержки включения силовых транзисторов инвертора регулируется только выбором параметров насыщающихся трансформаторов, что не желательно при настройке инвертора. Схе - 1 ма управления инвертором не позволяет форсировать запирание силовых транзисторов, что является существенным недостатком схемы.

Цель изобретения — повышение надежности путем уменьшения динамических потерь в транзисторах силового инвертора и устранения замагничивания сердечника силового трансформатора инвертора.

Поставленная цель достигается тем, что в устройство для управления транзисторным инвертором с силовым трансформатором, содержащее задающий генератор с выходным трансформатором с пятью выходными обмотками и блокирующий импульсный транс- зе форматор, вторичные обмотки которого включены последовательно с четырьмя-вторичными обмотками трансформатора задающего генератора и подсоединены к управляющим электродам транзисторов инвертора, введен формирователь блокирующих импульсов, симметричный блок и конденсатор, причем зз формирователь блокирующих импульсов подключен к пятой выходной обмотке трансформатора задающего генератора " через симметричный блок и конденсатор, при этом первичная обмотка блокирующего импульсного трансформатора подключена к выходу формирователя блокирующих импульсов, а его вторичные обмотки одноименными зажимами подсоединены к одноименным управляющим электродам всех транзисторов инвертора. 4$

Симметрирующий блок может быть выполнен в виде двух встречно-параллельных диодов, последовательно с которыми вклю чены переменные резисторы.

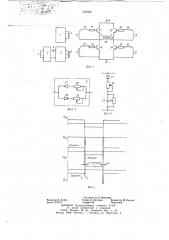

На фиг. 1 представлена блок-схема устройства управления транзисторным инвертором; на фиг. 2 и 3 показаны примеры выполнения симметрирующей цепи; на фиг. 4 изображены временные диаграммы, поясняющие работу формирователя блокирующих импульсов и процесс образования сигнала управления. "

Устройство "У1гравлеййя силовым тран- зисторным инвертором (фиг. 1) содержит

4 задающий генератор 1 с трансформатором 2, формирователь блокирующих импульсов 3, подключенный к выходной обмотке 4трансформатора 2 через симметрирующую цепь 5 и конденсатор 6. На выход формирователя блокирующих импульсов 3 подключена первичная обмотка 7 импульсного трансформатора 8, выходные обмотки 9 — 12 которого соединены последовательно с выходными обмотками 13 — 16 трансформатора 2 и через резисторы 17 — 20 подключены соответственно к управляющим электродам силовых транзисторов 2! — 24 инвертора. В диагональ инвертора включена первичная обмот- ка 25 силового трансформатора 26.

Симметрирующая цепь может быть выполнена из включенных встречно-параллельно диодов 27, 28 и переменных резисторов 29, 30 (фиг. 2) или из включенных последовательно диода 31, резистора 32 и конденсатора 33 зашунтированного резистором 34 (фиг. 3) .

Формирователь блокирующих импульсов 3 работает следующим образом.

Напряжение U 5 (фиг. 4) с обмотки 4 трансформатора 2 через симметрирующую цепь 5 дифференцируется конденсатором 6 и поступает на вход формирователя блокирующих импульсов 3. Импульсы напряжения V < вторичных обмоток 9 — 12 показаны на фиг. 4. На входе формирователя блокирующих импульсов 3 установлена симметрирующая цепь 5, которая может быть включена либо последовательно с обмоткой 4 трансформатора 2 и выполнена, например, по схеме фиг. 2, либо параллельно обмотке 4 трансформатора 2 и выполнена, например, по схеме фиг. 3.

Симметрирующая цепь (фиг. 3) может быть включена последовательно с обмоткой 4 и выполнена в виде двух встречно-параллельных диодов 27, 28 последовательно с которыми включены переменные резисторы 29, 30, что позволяет изменить фазу импульсов U e (фиг. 4) с помощью переменных резисторов 29, 30, причем по одному фронту конденсатор 6 заряжается через полупроводниковый диод 28 и переменный резистор 30, а по другому фронту — через диод 27 и переменный резистор 29. Симметрирующая цепь (фиг. 4) может быть под- ключена параллельно обмотке 4 трансформатора 2 и выполнена в виде включенных последовательно диода 31, переменного резистора 32 и конденсатора 33, зашунтированного резистором 34. Эта цепь представляет собой интегродифференцирующее звено. Диод 31 позволяет воздействовать только на один фронт напряжения, наводимого в обмотке 4, а переменный резистор позволяет изменять постоянную времени интегродифференцирующей цепочки, что обеспечивает изменение фазы одного из импульсов, запускающих формирователь 3. Таким образом, симметрирующая цепь позволяет ме663066

5 нять длительность открытого состояния силовых транзисторов путем изменения фазы блокирующих импульсов, что необходимо при выравнивании вольтсекундных площадей напряжения на первичной обмотке 25 силового трансформатора 26.

Формирование сигнала управления транзисторами инвертора происходит следующим образом.

6 шения динамических потерь формированием выключения силовых транзисторов инвертора, так как уменьшение потерь в транзисторах приводит к резкому снижению массогабаритных показателей ключей силового инвертора и улучшает КП,1 устройства в целом.

Формула изобретения

Предположим, что полярность напряжения обмоток 13 и 16 является для транзисторов 21 и 24 открывающей и они открыты, а полярность напряжения 14 и 15 для транзисторов 22 и 23 является закрывающей и они закрыты. В момент, когда во всех обмотках трансформатора 2 изменяется полярность напряжения Бзз (фиг. 4), что соответствует моменту времени t, на вход формирователя блокирующих импульсов 3 со вторичной обмотки 4 трансформатора 2 через симметрирующую цепь 5 и дифференцирующий конденсатор 6 поступает импульс запуска. На выходных обмотках 9 — 12 трансформатора 8 появляются блокирующие импульсы напряжения Uaб. Выходные обмотки 9 — 12 подключены так, что наводимое в них напряжение является запирающим для всех транзисторов (21 — 24) инвертора.

В интервале времени 6 t к управляющим электродам транзисторов 21 и 24 прикладывается сумма напряжений Uq7 (фиг. 4), наводимых в обмотках 9, 13 и 12, 16, а к управляющим электродам транзисторов 22 и 23 в это время приложена разность напряжений 1)зз (фиг. 4), наводимых в обмотках 10, 14 и 11, 15. Под действием напряжения Usб в интервале времени Л1 транзисторы 21 и 24 форсированно закрываются, а транзисторы 22 и 23 остаются в закрытом состоянии под действием напряжения UasТранзисторы 22 и 23 открываются в момент времени t задним фронтом блокирующего импульса. К этому времени транзисторы 21 и 24 полностью закрылись. При следующем переключении процессы будут протекать аналогично, а переключаемые транзисторы меняются местами.

Введение в устройство управления транзисторным инвертором формирователя блокирующих импульсов и симметрирующей цепи позволяет повысить надежность инвертора путем устранения замагничивания сердечника силового трансформатора и умень1. Устройство для управления транзис10 торным инвертором, с силовым трансформатором, содержащее задающий генератор, с выходным трансформатором с пятью выходными обмотками, блокирующий импульсный трансформатор, вторичные обмотки которого включены последовательно с четырьмя вторичными обмотками трансформатора задающего генератора и подсоединены к управляющим электродам- транзисторов инвертора, отличающееся тем, что, с целью повышения надежности путем уменьшения динамических потерь в транзисторах инвертора и устранения замагничивания сердечника силового трансформатора инвертора, оно дополнительно снабжено формирователем блокирующих импульсов, симмен трирующим блоком и конденсатором, причем формирователь блокирующих импульсов,подключен к пятой выходной обмотке трансформатора задающего генератора через симметрирующий блок и конденсатор, при этом первичная обмотка блокирующего импульсного трансформатора подключена к выходу формирователя блокирующих импульсов, а его вторичные обмотки одноименными зажимами подсоединены к одноименным управляющим электродам всех транзисторов инвертора.

2. Устройство для управления по и. 1, отличающееся тем, что симметрирующий блок выполнен в виде двух встречно-параллельных диодов, последовательно с которыми включены переменные резисторы.

40 Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР М 262251, кл. Н 03 М 7)48, 1963.

2. Арефьев и др. К вопросу уменьшения

4$ динамических потерь в транзисторных инверторах. сб. «Современные задачи преобразо, вательной техники». К., 1975. т. 5, с. 375—

381.

3. Авторское свидетельство СССР

% 282508, кл. Н 02 М 7/52. 1969.

663066

72

77

Pve. I (Ïvã. 3

Pvr. Ф

Составитель О. Наказная

Редактор Д. Зубов Техред О. Луговая Корректор М. Вигула

Заказ 2723/57 Тираж 856 Подписное

ЦH И И П И Государственного комитета СССР по делам изобретений и открытий

1|3035, Москва, Ж вЂ” 35, Раушская наб., д.

Филиал ППП «Патент», r. Ужгород, ул. Проектная, 4