Реверсивный преобразователь распределитель импульсов

Иллюстрации

Показать всеРеферат

iii663 I 08

Союз Соавтскмк

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДВТВЛЬСТВУ (61) дополнительное к авт. свид-ву (22) Заявлено 05,07.71 (21) 1676905/18 — 21

1

J вщ ;, 1«Ц, 2

{5!) М. Кл.

Н 03 К 17/62 с присоединением заявки №вЂ”

Гесударстввккык квмктвт

СССР во двлвм кзвбрвтвккй к вткрв«так (23) Приоритет

Опубликовано 15,05.79. Б«оллетень № 18 (53) УДК 621.372. .2 (088,8) Дата опубликования описания 19.05.79!

А. И. Кривоносов, В. М. Миролюбск«й, В. И. Редченко, Г. А. Кузьмин, Л. ф Сулима и О. К. Левшин (72) Авторы изобретения. (71) Заявитель (54) РЕВЕРСИВНЫЙ ПРЕОБРАЗОВАТЕЛЬ вЂ” РАСПРЕДЕЛИТЕЛЬ

ИМПУЛЬСОВ

Изобретение относится к электронике и может найти применение в системах и приборах автомати. ческого контроля и регулирования, информационно- вычислительной и вычислительной технике для согласования цифровых устройств с исполнительными органами шагового типа, для формирования сигналов, распределенных по нескольким каналам управления.

Известен реверсивный преобразователь-распределитель импульсов, содержащий элементы И, ключи, линии задержки, диодные матрицы и резисторы.

Недостатком этого преобразователя является сложность, обусловленная необходимостью разработки различных блоков специального назначения при переходе от одного закона управления к дру«5 гому.

Известен также реверсивный преобразовательраспределитель импульсов, содержащий первый и второй триггеры основного и первый и второй .

20 триггеры вспомогательного регистров, элементы

И, элементы ИЛИ, причем единичные выходы первого и второго триггеров основного регистра соединены с первыми входами первых элементов И, 2 .выходы которых соединены с нулевыми входами соответственно первого и второго триггеров вспомогательного регистра, единичные входы первого и второго триггеров основного регистра соединены с выходами соответствейно первого и второго элементов ИЛИ, входы элементов И соединены с входами третьего элемента ИЛИ.

Однако функциональные возможности такого реверсивного преобразователя-распределителя ограничены.

Цель изобретения — расширение функциональных возможностей устройства.

Для этого в реверсивный преобразователь-распределитель импульсов, содержащий первь.й и второй триггеры основного и первый и второй триггеры вспомогательного регистров, элементы

И, элементы ИЛИ, причем единичные выходы пер- вого и второго триггеров основного регистра соединены с первыми входав.и первых элементов И, выходы которых соединены с нулевыми входами соответственно первого и второго триггеров вспомогательного регистра, единичные входы первого и второго триггеров основного регистра соединены с, выходами соответственно первого и второго

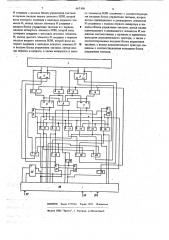

3 663108 .ф элементов ИЛИ вхо ы элеме д . нтов И соединены с первого инвертора и выходом блока управления входами третьего элемента ИЛИ, дополнительно . тактами, третьи вхо ы о р и входы одиннадцатого и двенадцадены третии, четвертый, пятый, шестой, седь- того элемент И ов соединены соответственно с н ° мои, восьмой, девятый, десятый о инн нуи двен аты д адцатыи левым и единичным выходами дополнител т льного

Э адц и элементы И, четвертыи и пятый 5 триггера а также с соответствующими входами элементы ИЛИ, два инвертора, дополнительный блока управления тактами в ами, входы дополнительноены с соответствующими выхо.тр г р, локи синхронизации и управления так- ro триггера соедин тами, причем выходы триггеров основного регист- дами блока управления тактами. ра соединены с входами блока синхронизации, На чертеже представлена блок-схема предлагаепервые входы вторых элементов.И соединены с, 1ф мого реверсивного преобразователя-рас еделителя. нулевыми выходами триггеров основного регбист- Реверсивный преобразователь-распределитель ра, нулевые входы которых соединены соответст- содержит блок I синхронизации, в но с выходами четвертого и пя:ого элементов, триггеры 2,3 основного регистра, первые элеменИсое енысвь о

И И, вторые входы первых и вторых элементов . ты 4 И вторые элемен 5 И, соединены с выходом первого инвертора, выхо- тЗ триггеры 6, 7 вспомогательного регистра, третий ды вторых элементов И соединены соответствен- . элемент 8 ИЛИ, третин, четвертый, пятый, шестой, но с единичными входами первбго и второго триг- седьмой восьмой дев

> евятыи, и десятыи элементы геров вспомогательного регистра, выход третьего . 9 10 11 12 13 14 15 16 И,, первый, второй, четэлемента ИЛИ соединен с входом блока управле- вертый и пятый элементы 17, 18, 19, 20 ИЛИ, ния тактами и входом второго инвертора, выход 20" одиннцщатый и двенадцатый элементы 21, 22 И, которого соединен с первыми входами один щ - первый и второй инверторы 23, 24, дополнительцатого и двенадцатого элементов И, единичный ный триггер 25 знака, блок 26 управления тактавыход первого триггера вспомогательного регист- ми шину 27 "Вход" шин 28 "P ", 29 ра соединен с первыми выходами четвертого, пя- "Прямой код". того, девятого и десятого элементов И, нулевой . И Устройство рабо ройство ра отает следующим образом. выход первого триггера вспомогательного регист- При отсутствии импульсов на шине 27 "Вход" ра соединен с первыми входами третьего, шесто- через первый инвертор 23 разрешается прохождего, седьмого и восьмого-элементов И, единичный ние сигналов через элементы 4, 5 И перезаписи, выход второго триггера вспомогательного регист- и информация с вых ин о мация с выходов исполнительных тригге-Ра соединен с втоРыми входами тРетьего, четвеР.. 30 pов 2 3 ров, основного регистра переписывается на . того, седьмого и десятого элементов И, нулевой промежу промежуточные триггеры 6, 7 вспомогательного выход второго триггера вспомогательного регист-. регистра. ра соединен с вторыми входами пятого, шестого, Перед поступл н еред поступлением входных импульсов на шивосьмого и девятого элементов И; третьи входы ну 27 "Вход" 25

" ход триггер знака устанавливается третьего, четвертого, пятого и шестого элементов З> в соответствующее положение ™1" или "0" микрямои вход или шисоедщены с выходом одиннадцатого элемента рокомандой на шине 29 "П

И, третьи входы седьмого, восьмого, девятого и не 28 "Реверс", подготавливая соответственно расдесятого элементов И соединены с выходом две- пределяющие элементы 21 И или 22 И прямого надцатого элемента И, выход третьего элемента " хода или реверса. Независимо от состояния тригИ соединен с первым входом первого элемента 4В гера 25 знака входные импульсы, проходя через

ИЛИ, второй вход которого соединен с выходом инвертор 23 своим передним фронтом закрывают восьмого элемента И и входом блока управления элементы 3, 4 И перезаписи, то есть отключают тактами, выход четвертого элемента И соединен входы триггеров 6, 7 вспомогательного регистра с выходом блока управления тактами и первым от выходов триггеров 2, 3 основного регистра. входом пятого элемента ИЛИ, второй вход кото- <> После полного отключения элементов 3 4 И пере7 рого соединен с выходом седьмого элемента И, записи собирательный элемент 8 ИЛИ вырабатывыход пятого элемента И соединен с входом бло- вает сигнал, соответствующий уровню "0" кото1 ко ка управления тактами и с первым входом чет-. рый управляя инвертором 24 разрешает прохождевертого элемента ИЛИ, второй вход которого сое- ние входного импульса через распределяющие динен с выходом десятого элемента И, выход шее- ® ячейки 21 И или 22 И реверса или прямого хода. того элемента И соединен с первым входом второ- При осуществлении прямого хода микрокоманго элемента ИЛИ, второй вход которого соединен дой по шине 29 "Прямой ход" триггер 25 знака с выходом девятого элемента-.И и входом блока устанавливается в положение "1". В этом случае управления тактами, третьи входы первого и вто- . входной импульс, проходя через распределяющий рого, а также четвертого и пятого элементов ИЛИ элемент 22 И прямого хода, поступает на элеменсоедйнены с Соответствующими входамй блока ты 10, 14, 15, 16 И управления прямого хода коУ управления тактами, вторые входы одиннадцатого торые в зависимости от состояния тригге 6, 7 триггеров и двенадцатого элементов И соединены с входом формируют на выходе одного из управляющих

663108

6 элементов 17, 18, 19, 20 ИЛИ сигнал, опрокиды- Формула изобретения вающий один из рабочих триггеров 2 или 3 основного регистра в состояние, соответствующее отра- Реверсивный преобразователь-распределитель битке шага в прямом ходе. импульсов содержащйй первый и второй триггеПосле окончания входного импульса элементы S ры оснбвного и первый и второй триггеры вспо3, 4 И перезаписи открываются и новое состояние могательного регистров, элементы И и элементы исполнительных триггеров 2, 3 переписывается на ИЛИ, причем единичные выходы первого н второ> промежуточные триггеры 6, 7, то есть устройство ro триггеров основного регистра соединены с перготово для отработки следующего импульса на выми входами первых элементов И, выходы которых соединены с нулевыми входами соответстшине 27 "Вход". Далее процесс повторяется.. 10 торых соединены с нулевыми вход и соо е

При осуществлении реверса триггер 25 знака венно первого и второго триггер в о нно пе в го и вто ого триггера вспомогательустанавливается микрокомандой по шине 28 ного регистра единичные входы первого н

» ЗЪ » » и

Реверс в состояние О, то есть вслед за отклю го триггеров основного регистра соединены с вы- чением входов промежуточных триггеров 6, 7 or ходами соответственно первого и второго элеменвыходов исполнительных Tprtrrepos 2, 3 и появле. И тов ИЛИ а выходы. первых и вто ния разрешающего сигнала на выходе иивертора И соединены с входами третьего элемента ИЛИ, 24, выходной импульс через -распределяннций эле- отличающийся тем, что, с целью расширения мент 21 И реверса поступает на элементы 9, 11, функциональных возможностей, в него дополни2, 13 И управления реверсом, которые форми- . тельно введены третий, четвертый, пятый, шестой, руют на выходе одного иэ управляю|цих элемен. 20 седьмой, восьмой, девятый, десятьш, одиннадцатов 17, 18, 19, 20 ИЛИ сигнал, опрокидывающий . тый и двенадцатый элементы И, четвертый и пяодин из исполнительных триггеров 2, 3 в состоя. тый элементы ИЛИ, два инвертора, дополнительние, соответствующее отработке шага в реверсе. ный триггер и блоки управления тактами и синхПосле окончания входного импульса элементы 3, ронизации, причем выходы триггеров основного

4 И парезаписи открываются и новое состоянйе 25 регистра соединены с входами блока синхрониисполнительных триггеров 2, 3 переписывается на зации, первые входы вторых элементов И соеди промежуточные триггеры 6, 7. Далее цикл повто- иены с нулевыми выходами триггеров основного ряется. регистра, нулевые вхо|1ы"которых соединены соТаким образом промежуточные триггеры 6, 7 ответственно с выходами четвертого и пятого вспомогательного РегистРа запоминают пРейыдУ- 30 элементов ИЛИ, вторые входы первых и вторых щие состояния исполнительных триггеров 2; 3 и элементов И соединены с выходом первого ннверпосле поступления на шину 27»Вход" входного тора выходы вторых эле е И импульса управляют рабочими триггерами 2, 3 в ответственно с единичными входами первого и следующем порядке:

1 второго триггеров вспомогательного регистра, выдлЯ Режима пРЯмого единичный выход первого триггера вспомога»1»»i»

1 и 1 исполнительныи триггер 2 устанавлива- 4О тельного регистра соединен с первыми выходами

» \> четвертого, пятого, девятого и десятого элементов

Янин пРомежУточных ТРиггеРов 6, 7 И нулевой выход rrepsoro триггера вспомогатель» и и и

О и 1 испо ительныи триггер 3 уставлива- ного регистра соед ен с первыми вход и треп»>»>

> его, шестого, седьмого и восьмого элементов И, при состоянии промежуточных триггеров 6, 7 4S единичный выход второго триггера вспомогатель» » и и

0 и О исполнительныи триггер 2 устанавлива-, ного регистра соединен с вторыми входами треть»>и ется в 1 . его,четвертого, седьмого и десятого элементов И, Далее цикл повторяется. нулевой выход второго триггера вспомогательноДля режима реверса. при состоянии про-1 го регистра соединен с вторыми входами пятого, межуточных триггеров 6, 7 "Г и »0» соответст- So шестого, восьмого и девятого элементов И, третьи венно исполнительный триггер 2 устанавливается входы третьего, четвертого, пятого и шестого элев состояние »0"; при состоянии триггеров 6, 7 ментов И соединены с выходом одиннадцатого

»0» и »0» триггер 3 устанавливается в состояние элемента И, третьи входы седьмого, восьмого, .»1", при состоянии промежуточных триггеров 6, девятого и десятого элементов И соединены с вы7»0» и »1» исполнительный триггер 2 устанавли- у ходом двенадцатого элемента И, выход третьего вается в состояние "1", при состоянии промежу- элемента И соединен с первым входом первого точных триггеров 6, 7»1» и »1» исполнительный элемента ИЛИ, второй вход которого соединен с григгер 3 устанавливается в состояние »0". выходом восьмого элемента И и входом блока

Далее цикл повторяется. управления тактами, выход четвертого элемента

663108

ЦКИИПИ Заказ 2727/60 Тираж 1059 Подписное

Филиал ППП "Патент", г. Ужгорса, ул.Проектная,4

И соединен с входом блока управления тактами и первым входом пятого элемента ИЛИ, второй вход которого соединен с выходом седьмого элемента И, выход пятого элемента И соединен с входом блока управления тактами и с первым 3 входом четвертого элемента ИЛИ, второй вход которого соединен с вь ходом десятого элемента

И, выход шестого элемента И соединен с первым входом второго элемента ИЛИ, второй вход которого соедине11 с выходом девятого элемента И 16 и входом блока управления тактами, третьи входь1 первого и второго, а также четвертого и пято. го элементов ИЛИ соединены с соответствующими входами блока управления тактами, вторые входы одиннадцатого и двенадцатого элементов

И соединены с входом первого инвертора и выходом блока управления тактами, третьи входы одиннадцатого и двенадцатого элементов И соединены соответственно с нулевым и единичным выходами дополнительного триггера, а также с соответствующими входами блока управления тактами, а входы дополнительного триггера соединены с соответствующими выходами блока управления тактами,