Динамический элемент

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДВТВДЬСТВУ (6l) Дополнительное к авт. свиа-ву (22) Заявлено В1.04.74 (21) 2009744/18 — 21

Союз Советскмн

Социалистических

Республик

<" 663111

t (5!) М. Кл.

Н 03 К 19/00 с присоединением заявки №вЂ”

Государственнное намнтет

СССР не делам нэебретеннй.н еткрмтнй (23) Приоритет

Опубликовано 15,05,79. Бюллетень № 18 (53) УДК 621 374 (088,8) Дата опубликования описания 19.05,79 i (72) Авторы изобретения

Э. В. Филиппов, Л, Н. Гермаш, В. А. Морозов и Л. А, Спириденко (71) Заявитель

Опытно-конструкторское бюро при Ленинградском политехническом институте им. М. И, Калинина (54) ДИНАМИЧЕСКИЙ ЭЛЕМЕНТ

; тывающее пересечение выхода элемента с выходами и входами других элементов, а также с шина-: ми фазовых напряжений.

Бель изобретения — повышение помехозащнщенности элемента путем увеличения напряжения

5 логической единицы на выходе элемента.

Для этого в динамический элемент, состоящий из параллельно включенных зарядного и логического МДП-транзисторов, стоки которых и затвор зарядного транзистора подключены к шине первой фазы, а истоки соединены с истоком ключевого МДП-транзистора, затвор которого соединен е шиной второй фазы, а сток подключен к выходу

/ элемента, введены два конденсатора . Обкладка первого и обкладка второго конденсаторов соединены с выходом элемента, другая обкладка первого конденсатора соединена с шиной третьей фазы, а другая обкладка второго конденсатора — с шиной четвертой фазы.

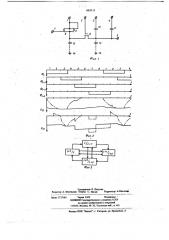

На фиг. 1 представлена электрическая принципиальная схема дйнамического элемента.

Схема содержит 1-4 — шины фаз Ф, Ф., Ф.

1 1 Н it2 и Ф.. К шине 1 подключены сток и затвор эа Ф3 рядного МДП-транзистора 5 и сток логического

Изобретение касается электронной техники и может быть использовано при построении больших интегральных схем (БИС) с многофазным питанием.

Известны динамические элементы, состоящие иэ зарядного, ключевого и логических МДП-транзисторов, позволяющие увеличить .степень интеграции устройств, снизить потребляемую мощность вследствие устранения сквозного тока (1).

Наиболее близким по технической сущности к предложенному является динамический элемент, состоящий из параллельно включенных зарядного и логического МДП-транзисторов, стоки которых и затвор зарядного транзистора подключены к шине первой фазы, а истоки соединены с истоком ключевого МДП-транзистора, затвор которого соединен с шиной второй фазы, а сток подключен к выходу элемента (2).

Недостатком его является пониженное (в сравнении с фаэовым питанием) напряжение логической единицы на выходе элемента, равное U=U — — U — U где 0 — напряжение фазы, 0 — попо р лом Ф ,0 роговое напряжение зарядного транзистора, Unoeнапряжение емкостной паразитной наводки, учи .ЙМ- Д«-4Ъу."4Ж ЭОМ! н " . . " - - «Е ъ» дующему элементу. Для увеличения напряжения логической единицы при работе элементов друг на друга без пропуска фаз согласно граф-схеме на фиг. 3 используется конденсатор 10, В случае напряжения логического нуля на входе во время приема информации послед. ющим элементом выходное напряжение будет увеличиваться пропорционально емкостному делителю, состоящему из конденсаторов 10 и 13. При напряжении логичес10 кой единицы на входе 7 элемента, вследствие того, что логический и. ключевой транзисторы 6 и

"8 открыты, происходит разряд конденсаторов 10, 11 и 13 и напряжение логического нуля на выходе элемента практически остается неизменным. о

О При работе элементов с пропуском фаз увеличение напряжения логической единицы осуществля.ется аналогичным образом, однако если передача информации между элементами без пропуска фаз, в частности с i-того элемента íà (i+1) íûé

20 элемент, происходит в моменты времени 6, 7 (см. фиг . 2), то передача информации с пропуском фаз охватывает добавочно интервалы 8, 1, поэтому для увеличения напряжения логической единицы при работе элементов с пропуском фа5 зы, например с Иого элемента íà (i+2)-ный элемент, необходимо подключить два конденсатора

10 и 11.

Введение дополнительных конденсаторов обеспечивает повышение напряжения логической едиЗО ницы, благодаря чему увелйчивается помехоэащищенйость элемента, Формула изобретения

Динамический элемент, состоящий из параллельно включенных зарядного и логического МДПтранзисторов, стоки которых и затвор зарядного транзистора подключены к шине первой фазы, а истоки соединены с истоком ключевого МДПтранзистора, затвор которого соединен с шиной второй фазы, а сток подключен к выходу элемента, отличающийся тем, что, с целью увеличения помехоэащищенности элемента, в него введены

45 два конденсатора, причем обкладка первого и обкладка второго конденсаторов соединены с выходом элемента, другая обкладка первого конденсатора соединена с шиной третьей фазы, а другая . обкладка второго конденсатора — с шиной четверзв той фазы.

Источники информации, принятые во внимание при экспертизе

1. Филиппов А. Г; "Транзисторные динамические элементы ЦВМ", М., Сов, радио, 1969.

Я 2. Патент CILIA N4 3524077, кл. 307-246, 1970.

3 . . 663111

МДП-транзистора 6, затвор которого является одновременно входом 7 элемента. Истоки транзисторов 5 и 6 подключены к истоку ключевого транзистора 8, затвор которого подключен к шине 2, а сток — к выходу элемента 9. Между выходом элемента 9 и шинами 3 и 4 включены, соответственно, конденсатор 10 и 11. Конденсаторы

12 и 13, включенные между общей шиной 14 (в

/ качестве общей шины используется подложка) и, соответственно, истоками транзисторов 5, 6 и стоком транзистора 8, представляют собой эквива. лентную емкость, образующуюся в элементе на

МЯП-транзисторах между указанными выводами..

На фиг. 2 представлены временные диаграммы, поясняющие работу элемента, Штрих-пунктирной линией показаны найряжения (U 12) н (U 13) на конденсаторах 12 и 13 для случая, когда на входе 7 — найряжение логи-,. ческой единицы. Сплошная линия соответствует напряжению логического нуля на входе 7 и работе элементов друг на друга беэ пропуска фаз.

Пунктирной линией показана добавка напряжения, вносимая дополнительным конденсатором 11 при работе 1-того элемента на (i+2) -ный элемент, т.е., с пропуском фазы.

На фиг. 3 изображена граф-схема передачи информации между элементами.

Внутри прямоугольника, изображающего элемент, приведены две фазы: в числителе указана фаза, во время которой протекает ток через зарядный транзистор 5, в знаменателе — фаза, во время которой протекает ток через ключевой транзистор 8.

Д яамический элемент работает следующим образом. .. : 35

При поступлении импульса на шину 1 через открытый зарядный транзистор 5 пройсходит заряд конденсатора 12. На фиг. 2 этот этап соответствует интервалам времени 1-3. В интервале времени

3, когда перекрываются импульсы фаз Ф„° и

Ф,„, поступающие, соответственно на шийы 1 и

2, открывается ключевой транзистор 8 и происхо- дит заряд конденсаторов 13, 10 и 11. В атедующие интервалы времени 4 и 5, когда ключевой транзистор 8 открыт, а напряжение на шине 1 равно нулю, в зависимости от информаций на входе 7 происходит (в случае напряжения логической единицы на входе) или не происходит (s случае на- пряжения логического нуля на входе) разряд указанных выше конденсаторов. После окончания действия импульса фазы Ф„, поступающего на шину 2, ключевой транзистор 8 эакрьй, а йапряжение на конденсаторе 13, соответствующее значению записанной информации, в интервалы 6, 7, 8 и 1 может быль использовано для передачи сле663111

1Ф

У г .3 4 К Ю ч г / г у т иа. 2

Составитель Л. быстрова

Редактор А. Шмелькин Техред С. Мига» Корректор А.нласейаэ

Тираж 1059 Подписное

ЦНИИПИ Государственного комитета СССР но делам изобретений и открытий113035, Москва, Ж-,35, Раушская наб., д. 4/5

Заказ 2727/б0

Филиал ППП "Патент", r. Ужгород, ул. Проектная .4