Преобразователь частоты в код

Иллюстрации

Показать всеРеферат

ПАТББ .. О- = ЕХЩ ЧР Щ бкб) и ена. А

И Е

Союз Советсккн

Соцкалисткмескмн

Реотублмк

<" 664152

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДИТЕЛЬСУВУ (61) Дополнительное к авт. свиа-ву (22) Заявлено 09.03.76 (21) 2331447/18 21 (51) М. Кл.

G 04 F 10/04

Н 03 К 13/20 с присоединением заявки № (23) Приоритет

Государственный- нюмитет

СССР па делам изобретений н ютирмтнй

Опубликовано25.05.79.Бюллетень № 19 (53) УДК 621.317 (088. 8)

Дата опубликования. описанйя 28.05.79 (72) Автор изобретения

П. B Соловов

Рязанский радиотехнический институт. (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ В KOQ

Изобретение относится к вычислительной технике и автоматике и может быть использовано в .системах управления дви жушимися обьектами в качестве преоб-разователя частотной информации в цифровой код.

Известен преобразователь частоты в код следяшего типа, содержаший реверсивный счетчик, делитель опорной частоты и двоичный умножитель, выход которого соединен с вычитаюшим входом реверсивного счетчика, а соответствуюшие входы соединены с выходами делителя частоты и реверсивного счетчика 11), Передаточная функция такого преобразователя аналогична инерционному звену

Щ- 1

РТ+ 1

2п где T= — - постоянная времени, эа- .

Fo висяшая от числа разрядов реверсивного

20 счетчика и величины опорной частоты, Йля обеспечения высокой точности тт должно выбираться достаточно большой величины, что не позволяет получить высокие динамические характеристики .преобразователя.

Из известных устройств наиболее близким по технической сушности к изобретению является преобразователь частоты в код, содержаший управляемый делитель частоты, входы которого подключены к разрядным выходам регистра памячу, группу элементов совпадения, счетчик:l.

К недостаткам такого устройства следует отнести большое время преобразования, равное

2 т т — ° о

Цель изобретения - уменьшение времени преобразования.

Ностигается это эа счет того, что в преобразователь частоты в код, содержаший управляемый делитель частоты, входы которого подключены к разрядным выходам регистра памяти, группу влементов совпадения, счетчик, дополнительно введенй регистр сдвига, триггер, коммупри этом Т „выбирается из условия

Твх мин = Т п 2твхмин

Каждый j-й шаг делении состоит из удвоения остатка, полученного на

1 з 664 1 татор опорных частот, два двухвходовых предыдушем (1--1) м шаге (+ 1-1 ) элемента совпадения, вычитаюший блок и его сравнении с периодом входной и элемент задержки, причем входные ши- частоты Т . Если 2 аТ1. „ЪТ„то ны регистра памяти соединены через 1 -му разряду частотного присваивает группу элементов совпадения с единич- 5 ся значение l" и определяется 1 -й ным выходом соответствуюших разрядов остаток ЬТ = 2ЬТ1 — Т . управляемого делителя частоты, а выход Если 2 ьТ„-«„ Т, то 1-му разряду

Ф у Il

"переполнения управляемого делителя ча- частотного, присваивается значение 0 . стоты соединен с первым входом вычитаю- Б этом случае для следуюшего 1+ 1 шего блока и сдвигаюшей шиной регистра 10 шага величина 2 аТ„„является оссдвига, у которого вход установки в татком h T„, Палее процесс повторяетединицу первого разряда соединен с вто- ся до получения последнего, р -го, рыми вХодами группы элементов совпа- разряда выходного кода. дения и выходом первого двухвходового Работает устройство следуюшим об- элемента совпадения, у которого один И р ом. вход через элемент задержки соединен, В исходном состоянии счетчик 7 и с единичным выходом триггера и первым триггер 10 обнулены, в регистр 2 и входом второго двухвходового элемента управляемый делитель 1 частоты засовпадения, а другой вход подключен писан код МТОП=Т „„Tо, в регистр 4 зак входу установки в единицу триггера, Ю писана 1" во второй разряд. Процесс му входу вычитаюшего блока и преобразования начинается с приходом к входной шине, при этом выход вычи- импульса преобразуемой частоты таюшего блока подключен к входу счет- который устанавливает триггер 10 в чика, выходы каждого разряда которого состояние "1". ри это р состояние "1". П и этом опо ная частосоединены с входами коммутатора опор- > та Fo начинает через коммутатор 8 и ных частот, выход которого подключен открывшийся элемент 5 совпадения пок второму входу второго двухвходо о ступать на управляемый делитель 1 часэлемента совпадения и через него к тоты. Таким о ра м, р д р тоты. аким образом, с приходом первовходу управляемого делителя частоты. го импульса входной астот го имп льса входной частоты начинается

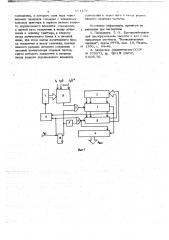

Синхронность начала периода входной фиг. 2 - временные диаграммы, поясняю- частоты Т х и периода Гоп позволяет шие его работу. легко произвести их сравнение. Если

З ты п ойдя элемент 6 совпадения, запидержит управляемый делитель 1 частоты Terü пройдЯ (уДЧ), регистр 2 памяти, группу эле- шет 1" в младший разряд регистра 4 и

3 впа ени регис р 4 сдвиг откРоет гРУппУ элементов 3 совпадениЯ. двухвходовые элементы 5 и 6 с:в аде- через которые сод ржи упр че з кото ые соде жимое управляемого ния, с ет ч чик 7 коммутатор 8 опорных делителя 1 частоты, представляюшее

4Q а кN Т-МТ частот, вычитаюший блок 9, триггер 10, собой в этот момент остаток элемент 11 задержки. -T >. F, перепишется в регистр 2 (см.

Моделируюшая зависимость М пред- Фиг, 2). Первый импульс на выходе yna la пагаемого устройства имеет вид равляемого делителя 1 частоты, соот11 ветствуюший моменту окончания интерВ3 вала Т«, произведет сдвиг содержи оп, мого регистра 4, .и вычтет "1 из вы- причем в устройстве вместо делении читакндего блока 9, ранее записанную входной частоты F на опорную Fop про- вторым импульсом входной частоты. изводится деление их периодов Т х и Кроме того, в этот момент (момент обТ,,,т.е. нуления счетчика управляемого целите2п Т ля 1 частоты), в управляемый делительl

ОП частоты переносится содержимое регистВХ ра 2, т.е. ron первого остатка М Т, который сразу же начинает преобразо вываться в интервал

"ь

ЬТ =— F

4$ = 7 6 ряпность выходного кода у прототипа и данного преобразователя равны между

\ собой и равны максимально возМожным для данных преобразователей величинам, 5 TQK KB K

Вх В х. Вакс (худший случай для данного преобразователя устройства). Время преобразования для прототипа равно

2лФ (Т

"P а

С учетом соотношения вх.макс

F !

Ю

Как спепует из фиг. 2, от момента прикола второго импульса входной частоты вто будет уже второй остаток АТ!,т.е. второй период входной частоты сравнивается с удвоенным остатком 2ЬТ!.Если

2дT Трх, то третий импульс входной частоты произведет изменения в схеме, аналогичные действию ее второго импульса, запишет "1" в млачший разряд регистра 4 и перепишет код второго ог,татка МдТ2=2М Т1-ТВх Fî в регистр 2.

След юший выходной импульс управляемого делителя 1 частоты (момент времени Т х + 2 ЬТ! ) аналогично его первому импулы:у, начнет формирование второго остатка ЬТ = ИдТ lFр. На фиг. 2 изображен случай, когда T 2дТ,при этом выходной импульс управляемого делителя 1 частоты, пройдя вычитаюший блок 9, запишет 1" в счетчик 7. Поэтому с коммутатора 8 на элемент 5 совпадения вместо частоты Fo начнет поступать частота Ро /2 . Следовательно, управляемый делитель,1 частоты начнет формировать интервал времени . (дТ а о сли Т 2 4 !.Т То импульс хода делителя 1 частоты (момент времени 2Тв Л + дТ2+ 2дТ ) снова сдвинет .

Вх содержимое регистра 4 и, пройдя вычитаюший блок 9, поступит в счетчик 7, увеличивая его содержимое на "1 . При этом коммутатор 8 переключит часто- ; ту с F /2 íà F j4, а управляемый делитель 1 частоты начнет формировать интервал имеем

tl

Т = -2 Т

ПР» Р,„.м „, ьх ии

Для предлагаемого устройства время преобразования равно !

Т

" " вх, !

25 пJn

Выигрыш в быстродействии равен 2 и, например, для десятиразрядного кода составляет 100.

Сушественно увеличенное быстродействие предлагаемое устройство позволяет

3О использовать для йреобразования быстроизменяюшихся входных частот.

Формула изобретения

35 !

Мдт

<»zИтак, предыдуший остаток удваивается до тех пор, пока не превысит период входной частоты.

Выходной код формируется в регистре

4 цифра эа цифрой, начиная со старшего разряда, путем записи влево. После И сдвигов записанная до начала работы " 1 из второго разряда регистра 4 переместится в (И + 1)-й разряд, что является сигналом окончания преобразования.

Время преобразования достигает максимума при N>b<> 11.....1 и равно !

ТпР ylTB„ йля оцейки выигрыша в быстродейст вии считаем, что входная частота и разПреобразователь частоты в код, содеркаший управляемый делитель частоты, входы которого подключены к разрядным

4 выходам регистра памяти, группу вле-, 40 ментов совпадения, счетчик, о т л ич а ю ш и и с я тем, что, с целью уменьшен!я времени преобразования, в него дополнительно введены два регистра

4 сдвига, триггер, коммутатор опорных

45 частот, два двухвходовых элемента совпадения, вычитаюший блок и влемент задержки, причем входные шины регистра памяти соединены через группу элементов совпадения с единичным выходом соответствуюших разрядов управляемого делителя частоты, а выход переполнения управляемого делителя частоты соединен с первым входом вычитаюшего блока и

55 сдвигаюшей шиной регистра сдвига, у которого вход установки в единицу первого разряда соединен с вторыми входами группы влементов совпадения и выходом первого двухвходового элемента

7 совпадения, у которого один вход через элемент задержки соедйнен с елиничным выходом триггера и первым входом второго двухвходового элемента совпадения, а другой вход подключен к входу установки в единицу триггера, к второму входу вычитаюшего блом и к входной шине, при этом выход вычитаюшего блока подключен к входу счетчика, .выходы каждого разряда которого соединены с 1о входами коммутатора опорных частот, выход которого подключен к второму входу второго двухвходового элемента

° 1г совпалс.пйя и через него к входу уирлвляемогс делителя частоты.

Источники информации, принятые во внимание при экспертизе

1. Г!аламаркк Г. О., Быстродействующий пре обра зова гель час готы в к on с не- прерывным отсчетом. Вычислительная техника", труды РРТИ, вып. 18, Рязань, 1970, с. 44-46.

2. Авторское свидетельство СССР № 37557 1е кл ЦО 1 R 23Ю21

04.05. 70.

664152

"югт

Hre

Составитель Г. Смелова

Редактор E. Гончар ТехредМ. Петко Корректор О. Билак .Заказ 2998/45 Тираж 50 1 . Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушскаи наб., д. 4/5

Филиал ППН Патент", г. Ужгород, yii. Проектнаи, 4