Устройство для отображения алфавитноцифровой информации

Иллюстрации

Показать всеРеферат

О П И С А H "И- !,.й.

И3ОБРЕТЕНИЯ ?иди)

-./ДФ

è!6641 66

Союз Советскии

Социалистнческня

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. саид-ву— (51)M. Кл.2 (22) Заявлено 29.1277(21) 2562205/18-24 с присоединением заявки Йо(23) Приоритет—

G F 3/14

Государственный комитет

СССР ио делам изобретений и открытий (53) УДК 681. 327.1 1 (088.8) Опубликовано 25.05.79. Бюллетень Но 19

Дата опубликования описания 2805.79 (72) Авторы

ИЗОбрЕтЕНИя К.К. Нахтигаль, Т.Г. Овчинников и В.В. Снегирев (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ АЛФАВИТНО-ЦИФРОВОЙ

ИНФОРМАЦИИ

Изобретение относится к автоматике и вычислительной технике и может быть использовано при разработке устройств отображения информации.

Известны устройства для отображения информации, содержащее блок rtaмяти, генератор импульсов и интеграторы (1).

Наиболее близким техническим решением к изобретению является устройство для отображения алфавитно« цифровой информации, содержащее генератор импульсов, последовательно соединенные блок интеграторов и блоки усилителей отклонения луча, другие l5 входы которых подключены к блоку памяти (2).

Основным недостатком известных, устройств является ограниченное быстродействие за счет инерционности пе- 20 реключения интеграторов.

Цель изобретения — повышение быстродействия устройства за счет уменьшения времени переключения интегра.торов.

Это достигаетсв тем, что устройство содержит сдвиговый регистр, вход которого подключен к генератору импульсов, а выход — ко входу блока ,интегратора, а также тем, что каждый ЗО блок усилителей отклонения луча содержит усилители, включенные по матричной схеме.

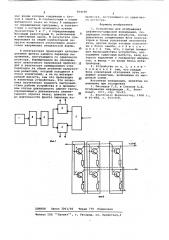

На фиг. 1 представлена структурная схема устройства; на фиг. 2 показан блок усилителей отклонения лу ча, пример выполнения.

Устройство содержит, генератор 1 импульсов,,бЛок 2 памяти, блок 3 интеграторов, блок 4, 5 усилителей отклонения луча, сдвиговый регистр б, транзисторы 7 и резисторы 8. устройство работает следующим образом.

Генератор 1 импульсов выдает равномерную по времени последовательность импульсов, которые подаются на вход сдвигового регистра б. Сдвиговый регистр имеет несколько выходов, количество которых определяется конфигурацией и.желаемым качеством воспроизведения знака. На каждом иэ выходов сдвигового регистра последовательно во времени появляется перепад напряжения с приходом очередного тактового импульса от генератора 1.

Фронт каждого перепада в блоке 3 интеграторов интегрируется до нужной степени и затем параллельно подает дя на первые входы блоков 4, 5, вто664166

Формул а и з о бр ет ен и я

ЦНИИПИ Заказ 3001/46 Тираж 779 Подписное

Филиал ItlI1 Патент, r. Ужгород, ул. Проектная,4 рые входы которых соединены с блоком 2 памяти. В соответствии с кодом выбранного знака из блока 2 выбирается определенная программа, в соответствии с которой включаются нужные

1 транзисторы 7 и 7, с определенными

BpcoBb pe3HcTopa 8, включенны 5 в эмиттерных цепях. В результате суммирования на общей коллекторной нагрузке появляется отклоняющее аналоговое напряжение специальной формы.

B интеграторах происходит интегрирование фронта каждого перепада напряжения, поступающего со сдвигового регистра. Формирование же отклоняющего аналогового напряжения происхо- 6 дит в результате суммирования этих перепадов на общем активном нагруэочном резисторе, который находится в блоке усилителей, а не на интегрирующей емкости, как это происходит в известных устройствах. Это позволяет значительно повысить быстродей:ствие работы устройства и в предельном случае длительность одного такта, определяющего длительность элементарного отрезка знака, довести его ® до длительности фронта перепада напряж ния, поступающего со сдвигового регистра.

1. Устройство для отображения алфавитно-цифровой информации, содержащее генератор импульсов, последовательно соединенные блок интеграторов и блоки усилителей отклонения луча, другие входы которых подключены к блоку памяти, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, оно содержит сдвиговый регистр, вход которого подключен к генератору импульсов, а выход — ко входу блока интеграторов.

2. Устройство по п, 1, о т л и ч а ю щ е е с я тем, что каждый блок усилителей отклонения луча содержит. усилители, включенные по матричной схеме.

Источники информации, принятые во внимание при экспертизе

1. Мясоедов Г.П. и Соколов A.Ä.

Отображение информации .. М., Воениздат, 1971, стр. 92- 93.

2. EIectronic Engineering, 1968 г., Р 40-488, с. 553-559.