Логическое запоминающее устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

pl>664222

Союз Советсиик

Социалистическим

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6!) Дополнительное к авт. свид-ву (51)М. Нл. (22) Заявлено290377 (23) 2469004/18-24 с присоединением аалвки Н9

G 11 С 15/00

Государственный комитет

СССР ио делам изобретений н открытий (23) Приоритет

Опубликовано 2505.79. Бюллетень Йо,19 (53) УДН 881. З27..6 (088.8) Дата опубликования описания 25.05,79 (72) Авторы

Е. П. Балашов, Ю. A. Суровцев, Г. А. Петров, В. С. Степанов, H3O6pSTOHNfl А. Ю. Гордонов, М. С. Куприянов и Н. Н. Варлинский (71) Заявитель (54) ЛОГИЧЕСКОЕ, ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Недостатком этого устройства является невозможность реализации на его основе кодирующего и декодирующего устройств без примене- ния специального устройства управления, что снижает область применения устройства.

Целью настоящего изобретения является расширение области применения устройства.

Изобретение относится к области запоминающих устройств.

Одно из известных логических запоминающих устройств (ЛЗУ) содержит накопитель, дешифратор, регистры (1).

Недостатком этого устройства является невысокое быстродействие.

Из известных устройств наиболее близким по техническОй сущности к данному изобретению является

ЛЗУ, содержащее накопитель, подключенный к дешифратору адреса и управляющим логическим элементам, входы которых соединены с соответствующими выходами первого регистра слова, соединенного со вторым регистром слова и блоком контроля, регистр адреса, блок управления (2).

Поставленная цеЛь достигается тем, что устройство содержит регистр микрокоманд, дешифратор микрокоманд, логический блок, элементы И и ИЛИ, причем одни входы элементов И первой и второй групп подключены к первому выходу блока управления, а другие входы — соответственно к выходам накопителя и регистра адреса, выходы одних элементов И второй группы непосредственно и других элементов И той же группы через разрядные элементы ИЛИ соединены со входами дешифратора адреса, одни

15 из входов разрядных элементов

ИЛИ подключены к выходам элементов

И третьей группы, входы регистра микрокоманд соединены с:выходами элементов И первой группы, а выходы

20 регистра микрокоманд подключены соответственно ко входам дешифратора микрокоманд и логического блока и первым входам элементов И третьей, четвертой и пятой групп, выходы де25 шифратора макрокоманд соединены соотвественно со вторыми входами элемечтов И четвертой группы, выходы которых подключены ко входам второго регистра слова, со вторыми вхо39 дами элементов И третьей группы, 664222 одними входами элементов ИЛИ, входом логического блока и первыми входами элементов И, вторые входы которых подключены к выходам блока контроля, а выходы — к другим входам элементов ИЛИ, выходы элементов ИЛИ соединены -соответственно 5 со счетным входом регистра адреса и вторыми входами элементов И пятой группы, выходы которых подключены к информационным входам регистра адреса:, второй выход блока 10 управления соединен с управляющим входом дешифратора микрокоманд.

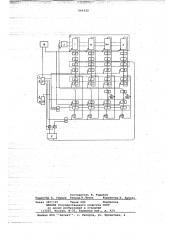

Яа чертеже изображена схема устройства. устройство содержит и-разрядный 15 накопитель 1, дешифратор адреса 2, управляющие логически элементы 3, первый регистр слова 4, второй регистр слова 5, блок контроля 6, регислр адреса 7, регистр микрокоманд 8, дешифратор микрокоманд

9, блок управления 10, элементы И первой группы 11, элементы И второй группы 12, разрядные элементы

ИЛИ 13, элементы И третьей группы

14, элементы И четвертой .группы 15, первый элемент ИЛИ 16, элементы

И пятой группы 17, первый элемент

И 18, второй элемент ИЛИ 19, логический блок 20, второй элемент И

21. Одни входы элементов И 11 и 12 подключены к первому выходу блока

10,а другие входы — соответственно к выходам накопителя l и регистра адреса 7.

Выходы одних элементов И 12 35 непосредственно и- других элементов

И 12 через разрядные элементы ИЛИ

13 соединены со входами дешифратора адреса 2, одни из входов элементов

ИЛИ 13 подключены к выходам элемен- 4() тов И 14. Входы регистра 8 соединены с выходами элементов И 11.

Первый и второй выходы регистра

8 (левые " на чертеже) подключены к соответствующим входам дешифрато- 45 ра 9, с третьего по m-ый выходы - ко входам блока 20, остальные выходы регистра соединены с первыми входами элементов И 14, предназначенных для передачи адреса операнда из регистра 8 на дешифратор 2. Выходы регистра 8 подключены также к первым входам элементов И 15 и 17. Выходы дешифратора 9 соединены соотвественно со вторыми входами элементов И 15, выходы которых подключейы к входам регистра 5, вторыми входами элементов И 14, одними входами элементов ИЛИ 16 и 19 входом блока

20, и с первыми входами элементов

И 18 и 21,вторые входы которых под- 6О ключены к Выходам блока 6,а вЫходы— к другим входам элементов ЙЛЙ 16 и 19.

Выходы элементов ИЛИ 19 и 16 соеди-. нены соответственно со счетным входом регистра 7 и вторыми входами 65 элементов И 17, выходы которых подключены к информационным входам регистра 7,.второй выход блока 10 соединен с управляющим входом дешифратора 9.

Устройство работает следующим образом.

Все ячейки накопителя 2 разделены на две группы.

Первая группа ячеек предназначена для хранения микрокоманд, вторая отведена под операционные и информационные ячейки. Микрокоманнпный . цикл при естественном порядке следования микрокоманд реализуется за два такта. Тактовые сигналы вырабатываются блоком 10, причем в первом такте сигнал появляется на его первом выходе, а во втором такте на втором.

В исходном состоянии регистр адреса 7 установлен в нулевое состояние (регистр 7 является одновременно и счетчиком).

В первом такте под действием управляющего сигнала с блока управления 10 на регистр микрокоманд

8 считывается из накопителя 1 микрокоманда по адресу, хранящему на регистре адреса 7., Микрокоманда имеет следующие форматы:

3 т rn+< и

2 3

Здесь приняты следующие обозначения:

КМΠ— код микрооперации, AO- адрес оператора, ANK - адрес следующей микрооперации, TNK - тип микрокоманды, Во втором такте управляющий сигнал с блока 10 опрашивает дешифратор микрокоманды 9 и в зависимости от кода ТМК дальнейшее функционирование предложенного устройства проис" ходит следующим образом1

ТМК 1(код II). При опросе дешиФратора 9 на его выходе появляется сигнал, который поступает на вход блока 20 и в зависимости от кода микрооперации на его выходе появляются соответствующие управляющие сигналы.

Кроме того, данный сигнал одновременно разрешает передачу адреса операнда из регистра микрокоманд

8 через элементы. И 14 и ИЛИ 13 на дешифратор адреса 2. Адрес следую66422 щей микрокоманды формируется одновременно с выполнением микрооперации, за счет установки регистра адреса 7 в следующее состояние путем подачи сигнала с выхода дешифратора 9 через элемент ИЛИ 19 на его вход. 5

ТМК-2 (код 00) . При опросе дешифратора 9 появляется сигнал на его выходе. Этот сигнал разрешает передачу содержимого, регистра микрокоманд 8 через элементы И 17 на регистр адреса 7.

ТМК-3. (код 01). При опросе дешифратора 9 на его выходе появляется сигнал, который поступает на элементы И 18, И 21. В зависимости от состояния блока 6 возможны два случая.

В первом случае при поступлении сигнала на элементы И 18, И 21 он разрешает передачу сигнала с одного выхода блока 6 через элемен20 ты И 21 и ИЛИ 16 на вход элементов И 17, разрешая передачу содержимого регистра микрокоманды 8 че. рез элементы И 17 на регистр адреса 7, Во втором случае, на другом выходе блока 6 присутствует сигнал, который через элементы И 18 и ИЛИ

19 поступает на вход регистра адреса 7, увеличивая его содержимое на единицу.

ТМК-4 (код 10). При опросе дешифратора 9 на выходе появляется сигнал, который разрешает передачу содержимого регистра микрокоманд 8, через элементы И 15 на регистр 5.,Одновременно через элемент

ИЛИ 19 данный сигнал поступает на вхоф"регистра адреса 7, увеличивая его содержимое на единицу.

Таким образом, реализация процесса кодирования и декодирования информации сводится к последовательному выполнению микрокоманд, которые реализуются эа два приведенных выще такта.

Особенностью рассмотренного устройства является совмещение функции управляющего и логического запоминающего устройств, что позволяет: сократить аппаратурные затраты по сравнению с организацией аналогичных устройств на основе двух раздельных блоков: устройства управления и логического запоминающего устройства; сократить число типов модулей (а при реализации на БИС- их числа и типов), что .приводит к повышению регулярности устройства и создает возможность для компановки устройства требуемой разрядности; за счет совмещения функции минимизиру- ются связи между устройством

2

6 управления и ЛЗУ, что приводит к повышению надежности устройства.

Формула изобретения

Логическое запоминающее устройство, содержащее накопитель, подключенный к дешифратору адреса и управляющим логическим элементам, входы которых соединены с соотвествующими выходами первого регистра слова, соединенного со вторым регистром слова и блоком контроля, регистр адреса, блок управления, о т л и ч а ю щ е е с я тем, что, с целью расширения области применения устройства, оно содержит регистр микрокоманд, дешифратор микрокоманд, логический блок, элементы И и ИЛИ, причем одни входы элементов И первой и второй групп подключены к первому выходу блока управления, а другие входы — соответственно к выходам накопителя и регистра адреса, выходы одних элементов И второй группы непосредственно и других элементов И той же группы через разрядные элементы ИЛИ соединены со входами дешифратора адреса, одни из входов разрядных элементов ИЛИ подключены к выходам элементов И третьей группы, входы регистра микрокоманд соединены с выходами. элементов И первой группы, а выходы регистра микрокоманд подключены соответственно ко входам дешифратора микрокоманд и логического блока и первым входам элементов.И третьей, четвертой и пятой групп, выходы дешифратора микрокоманд соединены соответственно со вторыми входами элементов И четвертой группы, выходы которых подключены ко входам второго регистра слова, со вторыми входами элементов И третьей группы, одними входами элементов ИЛИ, входом логического блока и первыми входами элементов И, вторые входы которых подключены к выходам блока контроля, а выходы — к другим входам элементов ИЛИ, выходы элементов ИЛИ соединены соответственно со счетным входом регистра адреса и вторыми входами элементов И пятой группы, выходы которых подключены к информационным входам регистра адреса, второй выход блока управления соединен с управляющим входом дешифратора микрокоманд.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

У 477464, кл. 6 1.1 С 15/00, 1974.

2 ° Авторское свидетельство СССР

9 5536/2, кл. Ц 11 С 15/00, ).976; (прототип б64222

Составитель В. Рудаков

Закаэ 3007/49 Тираж б80 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035 Москва Ж-35 Ра ская наб. д. 4 5

Филиал ППП Патент, г. Ужгород, ул. Проектная,. 4