Интегрирующее устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советсник

Социалистических

Республик

""666550 4r

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (2?) Завалено 19.1277(21) 2556822/18-24 с присоединением заявки Ио-(23) Приоритет— (51)М, Кл.2

G 06 G 7/18

Государственный комитет

СССР по делам изобретений и открытий

Опубликовано 050679. Бюллетень М 21

Дата опубликования описания 09.06.79 (53) УДК 681.335 (088.8) (72) Авторы

ИЗОбрЕтЕИИВ A. И. Фесенко, Е. И. Глинкин и В. С. Борисюк (7f ) ЗЮЯВИт@ЛЬ Тамбовский институт химического машиностроения (54) ИНТЕГРИРУЮЩЕЕ УСТРОЙСТВО

Изобретение относится к области аналоговой вычислительной техники и может быть использовано н счетно-решающих устройствах аналогового действия °

Известно устройство для интегрирования, содержащее блок интегрирования, вход которого соединен с первым входом суММатора, и блок дифференцирования (1). Однако зто устройство имеет большую погрешность.

Наиболее близким техническим решением к изобретению янляется устройство, содержащее сумматор, выход которого является выходом устройства, и последовательно включенные первый блок интегрирования, блок дифференцирования, блок вычитания, соединенный другим входом со входом первого блока интегрирования и со входом устройства, и второй блок интегрирования (2). Однако зто устройство имеет малый диапазон работы.

Целью изобретения является расширение динамического диапазона работы устройства.

Эта цель достигается тем, что предложенное устройство содержит два буферных блока памяти и последова тельно включенные компаратор, гене ратор пачек импульсов н блок управления, один из выходов которого подсоединен к управляющим входам буферных блоков памяти, а другой — к уста» новочным входам первого и второго блоков интегрирования, ныходы которьж соединены с информационными входами соответствующих буферных блоков памяти, подключенных выходами к соответствующим входам сумматора. Выход второго блока интегриронания подсоединен к одному из нходон компаратора, другой вход которого подключен ко входу постоянного напряжения устройства. Каждый буферный блок памяти содержит переключатель, информационный и управляющий входы которого являются одноименными входами блока, а выходы подсоединены ко входам соответствующих элементов

IIBMRTH выходы KQTopbIx являются выходами блока.

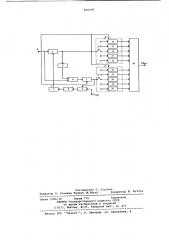

Схема интегрирующего устройства принедена на чертеже.

Устройство содержит первый 1 и второй 2 блоки интегрирования, блок

3 дифференцирования, блок 4 вь|читания, компаратор 5, генератор 6 па666550 чек импульсов, блок 7 управления, буферные блоки 8 и 9 памяти и сумматор 10.

Буферные блоки 8 и 9 памяти содержат переключатели 11 и 12 и элементы памяти 13 и 14 соответственно, Устройство работает следующим образом.

На вход устройства подается напряжение Е, С выхода блока интегрирования 1 через переключатель 11, замкнутый на вход первого элемента памяти 13 блока 8, поступает через сумматор 10 сигнал на выход устройства. Коэффициент передачи блока дифференцирования З.выбран равным 1 °

С его выхода корректирующий сигнал через блок вычитания 4, блок интегрирования 2, замкнутый переключатель 12 на вход первого элемента памяти 14 блока 8 и сумматор 10 поступает на выход устройства, компенсируя динамическую ошибку блока интегрирования 1. При достижении максимально возможного напряжения Ц на выходе блока интегрирования 1 входной сигнал Е начинает через блок вычитания 4 интегрироваться блоком 2.

При достижении напряжения на выходе блока 2, равного 0огр, компаратор 5 формирует на выходе импульс, который запускает генератор 6 пачек импульсов высокой частоты (в пачке три импульса) . Блок 7 управления под действием первого импульса с генератора 6 по первому выходу отключает переключатели 11 и 12 от входов элементов памяти 13 и 14. Под действием второго входного импульса блок 7 управления по второму выходу устанавливает блоки интегрирования

1 и 2 в и"ходное положение, обнуляя последние. Под действием третьего входного импульса блок 7 управления по первому выходу замыкает переключатели 11 и 12 на вторые элементы памяти 13, 14. При этом на выходе первых элементов памяти

13 и 14, ранее подключенных через переключатели 11, 12 к выходам блоков 1 и 2, остается запомненное напряжение, которое пддается на соответствующий вход сумматора 10. Затем цикл работы устройства повторяется.

Примен ние новых элементов: компаратора 5, генератора 6 пачек импульсов, блока 7 управления и двух блзков 8 и 9 буферных элементов памяти- позволило значительно расширить линейный диапазон работы устройства.

Формула изобретения

1, Интегрирующее устройство, со10 держащее сумматор, выход которого является выходом устройства, и последовательно включенные первый блок интегрирования, блок дифференцированич, блок вычитания, соединенный

15 другим входом с входом первого блока интегрирования и с входом устройства, и второй блок интегрирования, о т л и ч а ю щ е е с я тем, что, с целью расширения динамического диапазона работы устройства, оно содержит два буферных -блока памяти и последовательно включенные компаратор, генератор пачек импульсов и блок управления, один из выходов которого подсоединен к управляющим входам буферных блоков памяти, а другой — к установочным входам первого и второго блоков интегрирования, выходы которых соедийены с информационными входами соответствующих буферных блоков памяти, подключенных выходами к соответствующим входам сумматора, выход второго блока интегрирования подсоединен к одному из входов компаратора, другой вход

35 которого подключен ко входу постоянного напряжения устройства.

2. Устройство по п.l, о т л и ч а ю щ е е с ятем, что в нем каждый буферный блок памяти содержит

4Q переключатель, информационный и управляющий входы которого являются одноименными входами блока, а выходы подсоединены ко входам соответствующих элементов памяти, выходы

4 которых являются выходами блока.

Источники информацжи, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 224916, кл. G 06 G 7/18, 1967, 2. Авторское свидетельство СССР

Р 542199, кл." G 06 G 7/18, 05ЙИ7.

Сосгавитель Г. Сорокин

Редактор Л. Утехина Техред М.Петко Корректор В. Бутяга

Эакаэ 3186/39 Тирах 779 Подписное

ЦИИИПИ Государственного комитета СССР по делам иэобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная,. 4