Способ считывания выходного кода аналого-кодового преобразователя комбинированного уравновешивания

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик ()668086

К АВТОРСКОМУ СВИДВТВЛЬСТВУ

>,ô%1 ôô (61) Дополнительное к авт. свнд-ву— (22) ЗаЯвлено 03,08.76 (21) 2398345/18-21 с присоединением заявки №вЂ”

2 (51) М. Кл.

Н 03 К 13/03

Гасударатавиний каиктат

CtCP па делам кзабретанхй к аткрыткй (23) Приоритет

Опубликовано 15.06.79. Бюллетень № 22

Дата опубликования описания 15.06.79 (53) УДК

681.325 (088.8) (72) Авторы изобретения

В, А. Погрибной и И. В. Рожанковский (71) Заявитель

Физико-механический институт АН Украинской ССР (54) СПОСОБ СЧИТЫВАНИЯ ВЫХОДНОГО, КОДА АНАЛОГΠ— КОДОВОГО

ПРЕОБРАЗОВАТЕЛЯ КОМБИНИРОВАННОГО УРАВНОВЕШИВАНИЯ

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в быстродействующих системах с промежуточным аналого-кодовым преобразованием, в частности в бортовых системах.

Известен способ считывания кода с выхода следящих аналого-кодовых преобразователей, содержащих один компаратор (нуль. орган). В таких преобразователях считывание выходного кода производится непосредственно после отработки входного аналогового сигнала с помощью блока считывания, управляемого импульсами, генерируемыми компаратором в момент равенства входного и уравновешивающего напряжений. Подобным же образом осуществляют и съем кода с выхода тех аналого-кодовых преобразователей, в которых входная величина преобразуется в пропорциональный интервал времени. заполняемый импульсами образцовой частоты, количество которых затем подсчитывают с помощью счетчика. Съем показаний со счетчика осуществляют также после прихода управляющего импульса, который генерируется схемой сравнения в момент равенства соответствующих величин.

Недостаток такого способа — возможность

его использования только для преобразователей, построенных по способу последовательного счета, которые характеризуются малым быстродействием. В более быстродействующих аналогокодовых преобразователях рассмотренный способ съема кода не может найти применения, что ограничивает область его практического ислоль10 зования (1).

Наиболее близким техническим решением к изобретению является способ считывания выходного кода аналого-кодовых преобразователей поразрядного кодирования, обладающих высоким

15 быстродействием. Максимальное количество тактов отработки у и-разрядного преобразователя поразрядного кодирования равно h. Известнь|й способ обеспечивает считывание кода на протяжении n + 1 такта при поступлении на компаЗ1 ратор и + 1 импульса с генератора тактовых импульсов (2) .

Недостатком такого способа является неполное использование высокого быстродействия

66808

3 аналого- кодовых преобразователей поразрядного кодирования с индивидуальнымИ компараторами в каждом разряде (комбинированного уравновешивания) .

Целью изобретения является повышение быстродействия.

Поставленная цель достигается тем, что по способу считывания выходного кода аналогокодового преобразователя комбинированного уравновешивания, основанному на съеме кода i p путем стробированного считывания, съем кода осуществляют непосредственно вслед за окончанием последнего изменения состояния самого младшего разряда, для чего каждое изменение состояния младшего разряда преобразуют в импульс, который на время своей длительности запрещает считывание кода, причем длительность этого импульса выбирают равной длительности одного такта отработки процесса аналого-кодового преобразования. 2р

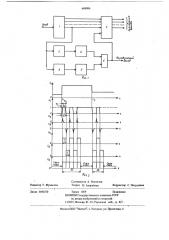

На фиг. 1 приведена блок-схема устройства, реализующего предлагаемый способ; на фиг,2 показаны временные зависимости сигналов основных блоков устройства, Устройство содержит и-разрядный аналого- 25 кодовый преобразователь комбинированного уравновешивания 1, определитель 2 положительного. знака производной и определитель 3 отрицательного знака производной, два одновибратора 4, 5, двухвходовой элемент ИЛИ 6 и элементзр

ЗАПРЕТ 7 с и сигнальными входами и одним запрещающим. Каждый из выходов всех разрядов аналого-кодового преобразователя соединен с соответствующим сигнальным входом элемента ЗАПРЕТ 7, кроме того, выход самого младшего (n-го) разряда соединен с входами определителей 2 и 3 знаков производной. Выходы последних соединены через соответствующие одновибраторы 4, 5 и двухвходовой логический элемент ИЛИ 6 с запрещающим входом элемен- 4р та ЗАПРЕТ.

Работает устройство следующим образом.

Если на входе аналого-кодового преобразователя 1 происходит изменение преобразуемого сигнала (0с в моменты t u gq на фиг. 2), которое отрабатывается за Х тактов, то соответственно Х ра3 изменяется амплитуда сигнала на выходе млашпсго разряда (U, на фиг.2).

С помощью определителей 2 и 3 знаков производной, в качестве которых могут быть ис- 5р пользованы, например, дифференцирующие це6

4 пи, выделяются положительные и отрицательные фронты напряжения U>, причем на выходе определителей появляются импульсы U и U3, соответствующие положительным и отрицательным фронтам. Импульсы Uz и 0з запускают соответствующие одновибраторы 4, 5, которые формируют управляющие импульсы длительности т — 04, U5. В этом случае на выходе элемента ИЛИ 6 появляются импульсы U, длительность которых равна Х т. Эти импульсы на время своей длительности запрещают съем выходного кода с выхода аналого-кодового преобразователя и одновременно сигнализируют об отсутствии достоверной информации на выходе устройства. Съем кода осуществляется непосредственно после окончания запрещающего импульса длительности Х т.

Таким образом, предложенный способ позволяет осуществлять съем выходного кода аналогокодового преобразователя комбинированного уравновешивания после окончания аналого-кодо. вого преобразования через интервал времени, не превышающий длительности одного такта отработки. входного сигнала указанным аналогокодовым преобразователем.

Формула изобретения

Способ считывания выходного кода аналогокодового преобразователя комбинированного уравновешивания, основанный на съеме кода путем стробированного считывания, о т л и ч аю шийся тем, что, с целью повышения быстродействия, съем кода осуществляют непосредственно вслед за окончанием последнего изменения состояния самого младшего разряда, для чего каждое изменение состояния младшего разряда преобразуют в импульс, который на время своей длительности запрещает считывание кода, причем длительность этого импульса выбирают равной длительности одного такта отработки процесса аналого-кодового преобразования.

Источники информации, принятые во внимание при экспертизе

1. Гитис Э. И. Преобразователи информации для электронных цифровых вычислительных устройств, М„"Энергия", 1975, с. 297.

2. Там же, с. 302.

668086 ующий

Ь лИ

О

1 5

Составитель А. Воителев

Техред Н. Андрейчук

Редактор Т, Юрчикова

Корректор С. Патрушева

Заказ 3483/50

0»

Тираж 1059 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб„д. 4/5,.

Филиал ППП "Патент", г, Ужгород, ул, Проектная, 4