Делитель частоты с переменным коэффициентом деления

Иллюстрации

Показать всеРеферат

Союз Советских

Соцмалмстических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт, свид-ву (22)Заявлено 16. 12.76 (21) 24294„-.7 18„21 с присоединением заявки М (23) Приоритет

Опубликовано 15. 06. 79.Бюллетень М 22

Дата опубликования описания 20, 06,79 (51)М. Кл.

Н 03 K 23/00

Госудвратаенннй комитет

СССР но делом изобретений н открввтнй (53) УДК 621.374, . 44 (088. 8) (72) Авторы изобретения

В. В. Фоменко П. Д. Андриенко и Т. И, Рогалева (71) Заявитель (54) ДЕЛИТЕЛЬ ЧАСТОТЫ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ

ДЕЛЕНИЯ

Изобретение относится к радиоэлектронике и может быть использовано в рациотехни чес ких ус гройс тввх, цифровой измерительной технике, а также как задаюший генератор для систем управления автоном- ными инверторами.

Известен целитепь частоты с переменным коэффициентом деления, содержаший задаюшее устройство, связанное через управляемую вентипьную схему со счетными .10 декадами единиц, десятков, сотен, поп» ключенных к генератору эталонных сигналов, устройство опознавания, вентильные и формируюшие схемы (1).

В данном устройстве повышение быст«

f5 родействия трех счетных декад достигается за счет гого, что повторные "загрузки счетных декад заданным кодом осушествляются самим вхоцным сигналом, а не дополнительным импульсом, выработанным в уст ройстве между двумя смежными входными сигналами. Однако в таких делителях имеют место поразрядное накопление задержки при переносе, что при большом диапазоне изменения управляемого коэффициента деления ипи большой разрядности самого пепитепя резко ограничивает его быстродейс твие и вызывает сбои в работе. Кроме того, при построении многодекадного

ДЛКД с организацией повторной "загрузки каждой пекады по такому принципу резко увеличивается минимальный коэффипиен т пе лен н я.

Известно также лногопекапное пересчетное устройство, сопержашее младшую и старшие счетные декады, элементы совпапения и блоки занесения кода(2), Принцип действия данного устройства заключается в том, что в счетные декады перед началом счета записывается число и в дополнительном десятичном коде 10 - N в результате чего сигнал переполнения счетных декад формируется после прихода

Я входных сигналов, I

В известном устройстве данная структура пересчетного устройства не позволяет реализовать максимальное быстродействие выбранных логических схем, в, сле668094

3 довательно, и обеспечить максимальную разрешаюшую способность пересчетного устройства по следующим причинам: при повышении входной частоты из-за задержки входных сигналов в тракте счета и опоэ. нввания второй декады невозможно осуществлять малые коэффициенты пересчета пекады младших разрядов; в младшую счетную декаду запись осуществляется в промежутке между входными импульсами, для чего необходимо дополнительное уст- фф ройство синхронизации в блоке занесения кода (иначе появляются сбои в работе этой декады); усложнена запись кода во вторую и последующие декады, что вызывает пропуски входных импульсов. $$

С це лью п о вы щения разрешающей сп особности устройства и повышения надежности его работы в делитель частоты с переменным коэффициентом деления, содержвший счетные декады> блоки занесения 26 кода и элементы совпадения, введены вентили, элементы ИЛИ в формирователь, вход которого соединен с выходом второго элемента совпадения, а выход - с первым входом первого элемента ИЛИ, выход 2$ которого подключен к входу блока занесения кода младшей счетной декады, при этом первый вход первого вентиля соединен с входной шиной, второй вход — с вы36 ходом первого элемента совпадения, первый выход через младшую счетную декадус первым входом второго элемента ИЛИ, второй выхоп - со вторыми входами первого и второго элементов ИЛИ, а выход. второго элемента ИЛИ подключен к перво-2$ му входу второго вентипя, второй вход которого соединен с выходом в >орого элемента совпапения, первый выход - со входом старшей счетной декады, а второй выход — со входами блоков занесения кода старших счетных декад.

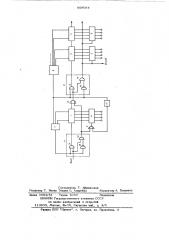

На чертеже представлена структурная электрическая схема предлагаемого целителя частоты с переменным коаффициентом деления.

Устройство содержит младшую декаду

1 и старшие декады 2,3, блоки 4-6 занесения кола, элементы совпапения 7, 8 (опознавание заполнения разрядов младшей и старших декад), элементы ИЛИ 9, 10, $O вентиди 11, 12 сигналов счета и установки начального состояния младшей и старших декап, формирователь 13, при атом веьтиaи 11, 12 состоят из элементов

И 14 - 17 и инверторов 18, 19.

Устройство работает следующим образом.

Перед начапом счета в счетные декады

1-3 записываются числа, соответствующие дополнительному коду. При коэффициенте пересчета от 1 до 9, если запись в декады произведена, разрешающий сигнал на выходе элемента совпадения 8 подготавливает элемент совпадения 7 к работе, так как счетные декады 2 и 3 находятся в состоянии 100 1. Входные импульсы проходят через вентиль 11 на младшую пекалу 1, так как на выходе элемента совпадения 7 присутствует разрешающий сигнал. Когда в процессе счета в младшей декаде 1 устанавливается состояние 1 00 1, на выходе элемента совпадения 7 появляется разрешающий сигнал для элемента

И 15, следующий входной импульс через элемент И, 15 и элемент ИЛИ 9 записывает код в следующую декаду, Этот же сигнал, пройдя через эпемент ИЛИ 10 и элемент И 17, является выходным. После записи кода младшая счетная декада 1 опять считает входные импульсы с заданным коэффициентом пересчета.

Повторная "загрузка" счетной декапы заданным кодом здесь осуществляется самим входным сигналом. При коэффициенте пересчета от 10 до 99 в счете входных сигналов участвуют декады 1 и 2, а в декаде 3 сохраняется состояние 100 1.

После записи кода в декады 1 и 2 происходит счет импульсов. Входы элементов

И 15, 17 для записи кода в декады 1 и

2 блокированы запрешающими сигналами с инверторов 18, 19. Сигнал переноса при насыщении младшей декады 1, снимаемый с ее выхода несет частоту в десять

1 раз меньше входной и проходит через элемент ИЛИ 10 и вентиль 12 на вход декады 2.. При насыщении декады 2 выходной сигнал элемента совпадения 8 блокирует дальнейшее прохождение импупьсов на вход декады 2, повторной записью дополнительного кода через формирователь 13 и элемент ИЛИ 9 восстанавливает исходное состояние декады 1, а также подготавливает элемент совпадения 7 и элемент

И 17 к работе. При заполнении декады 1 элементом совпадения 7 формируется разрешающий уровень для записи кода в декаду 1 через алемент И 15 и эпемент

ИЛИ 9 следующим входным импульсом.

Этот же импульс, являясь выходным для декады 1, в этом случае, пройдя через элемент И 16 и 17, производит запись кода в декадьr 2 и 3 через блоки 5 и 6.

Одновременно ои проходит и на выход устройства. При такой структуре коаффи668094

S d циент деления двух декад равен 10K* +4 „

* Аз где Кд - коэффициент деления декады 2 *

2 коэффициент деления декады 1. Такой коэффициент деления реализуется посредством использования элемечта ИЛИ 10.

Так как запись кода в декаду 2 производится входным сигналом, то вентиль

12 не пропускает импульсы на вход декады 2 до окончания процесса записи в ней при малых коэффициентах пересчета в декаде 1. При повышении входной частоты в тракте счета и опознавания декады 2 происходит задержка входных сигналов, что вызывает ложные заполнения входными импульсами декады 1 до прихода раз- . решаюшего сигнала на элемент совпадения, 7 с элемента совпадения 8 и младшей счетной декады 1, причем разрешаюшая способность декады 1 понижается. Для устранения этого сформированный формирователем 13 импульс через элемент ИЛИ 9 очишает" декаду 1 от лишних импульсов, появляющихся в реальных схемах. Это позволяет получить максимальную разрешающую способность при реализации макl5 симального быстродействия выбранных логических схем доступным способом. Лишние импульсы в декаде 1 могут быть учтены при необходимости установкой дополнительного счетчика в цепи записи кода

30 в декаду 1.

Р.:." )та устройства при коэффициентах

r.,.. «та от 100 до 10, где щ- кол чество счетных декад, происходит с тем лишь различием, что выполнение старших

35 декад происходит дольше и определяется ,их числом.

Формула изобретения

Делитель частоты с переменным коэффициентом деления, содержаший счетные 4р декады, входы которых соединены с выходами соответствующих блоков занесения ко11G, выходы младшей счетной декады подключены к двум входампервого элемента совпапения, третий вход которого подключен к выходу второго элемента совпадения, входы которого соединены с выходами старших счетных декад, соединенных последовательно, отличающийся тем, что, с пелью повышения разрешающей способности устройства и повышения надежности его работы, в него введены вентили, эле- менты ИЛИ и формирователь, вход которого соединен с выходом второго элемента совпадения, а выход - с первым входом первого элемента ИЛИ, выход которого подключен к входу блока занесения кода младшей счетной декады, при этом, первыЙ вход первого вентиля соединен с входной шиной, второй вход - с выходом первого эле лента совпадения, первый выход через младшую счетную декаду - c первым вхо- дом второго элемента ИЛИ, второй выходсо вторыми входамй первого и второго элементов ИЛИ, а выход второго элемента

ИЛИ подключен к первому входу второго вентиля, второй вход которого соединен с выходом второго элемента совпадения, первый выход - со входом старшей счетной декады, а второй выход - со входами блоков занесения кода старших счетных декад.

Источники информации, йринятые во внимание при экспертизе

1. Авторское свидетельство СССР

Мо 311268, кл. Я 06 Р 7/52, 1971;

2. Авторское свидетельство СССР

М 446951, кл; Н 03 К 23/02, 1974.

668094

Составитель Т. Афанасьева

Редактор Т. Янова Техред О. Андрейко . Корректор А. Филенко

Заказ 3484/51 Тираж 1059 Подписное

БНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж 35, Раушская наб„д. 4/5

Филиал ППП Патент, г. Мкгород, ул. Проектная, 4