Логарифмический преобразователь

Иллюстрации

Показать всеРеферат

(i 1) 67094I

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 25.01.78 (21) 2573094/18-24 с присоединением заявки № (23) Приоритет (51) М. Кл.е

С 06G 7/24

Гасударственный комитет (43) Опубликовано 30.06.79. Бюллетень ¹ 24 (53) УДК 681.335.8 (088.8) по делам изобретений н открытий (45) Дата опубликования описания 30.06.79 (72) Авторы изобретения

P. В. Бегота и Л. А. Лукащук

Львовский ордена Ленина политехнический институт (71) Заявитель (54) ЛОГАРИФМИЧ ЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к аналоговой вычислительной технике.

Известен логарифмический преобразователь (1), содержащий операционный усилитель, вход которого через масштабный ре- 5 зистор соединен с входом преобразователя и с коллектором биполярного транзистора, а эмиттер и база биполярного транзистора — соответственно с выходом операционного усилителя и шиной нулевого потенциала.

Недостаток такого преобразователя заключается в сравнительно сильном влиянии дрейфа нуля операционного усилителя на выходное напряжение устройства, которое 15 имеет небольшую величину.

Наиболее близким техническим решением к изобретению является логарифмический преобразователь (2), содержащий операционный усилитель, вход которого соединен с коллектором основного логарифмирующего транзистора и через входной масштабный резистор с входом преобразователя, а база основного логарифмирующего транзистора подключена к шине нулевого потенциала, и дополнительных логарифмирующих транзисторов и и дифференциальных операционных усилителей. Эмиттер каждого i-го (i=1, 2, ..., n — 1) дополнительного логарифмирующего транзистора соеди 30

2 нен с коллектором Ii+1)-го дополнительного логарифмирующего транзистора и с неинвертиру ющим входом соответствующего дифференциального операционного усилителя, инвертирующий вход которого соединен с базой соответствующего дополнительного логарифмирующего транзистора и с выходом того же дифференциального операционного усилителя. 1»оллектор первого дополнительного логарифмирующсго транзистора подключен и эмиттеру основного логарифмирующего транзистора, а эмиттер и-го дополнительного логарифмирующего транзистора — к выходу операционного усилителя.

его недостаток заключается в необходимости применения большого количества транзисторов и операционных усилителей.

Цель изобретения — упрощение преобразователя путем уменьшения количества транзисторов и операционных усилителей при сохранении точности работы устройства.

Поставленная цель достигается тем, что в известный логарифмический преобразователь, содержащип операционныи усилитель, вход ко — îðîãî соединен с коллектором основного логарифмирующего транзистора и через входной масштабный резистор с входом преобразователя, база основного лога670941 рифмир ющего транзистора подключена к шине нулевого потенциала, и дополнительных логарифмирующих транзисторов и и дифференциальных операционных усилителей, эмиттер каждого i-го (i = l, 2, ..., n — 1) дополнительного логарифмирующего транзистора соединен с коллектором (i+)-го дополнительного логарифмирующего транзистора и с неинвертирующим входом соответствующего дифференциального операци онного усилителя, инвертирующий вход которого соединен с базой соответствующего дополнительного логарифмирующего транзистора и с выходом того же дифференциального операционного усилителя, коллектор первого дополнительного логарифмирующего транзистора подключен к эмиттеру основного логарифмирующего транзистора, а эмиттер n-ro дополнительного логарифмирующего транзистора соединен с выходом операционного усилителя, дополнительно введен сумматор, один вход которого соединен с выходом операционного усилителя, а другие входы — с выходами соответствующих дифференциальных операционных усилителей.

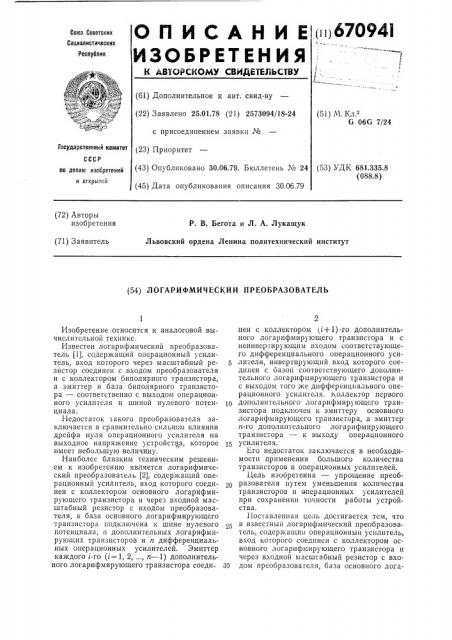

На чертеже представлена схема логарифмического преобразователя.

Логарифмический преобразователь содержит операционный усилитель 1, основной логарифмирующий транзистор 2, и дополнительных логарифмирующих транзисторов 3ь ..., 3 и дифференциальных операционных усилителей 4ь ..., 4„, входной масштабный резистор 5, сумматор 6.

Преобразователь работает следующим образом.

Изменение входного напряжения U» приводит к изменению коллекторного тока

I„, который вызывает соответствующее падение напряжения на эмиттерных переходах последовательно соединенных логарифмирующих транзисторов 2, 3ь ..., 3„. Дифференциальные операционные усилители

4ь ..., 4„обеспечивают необходимый режим работы логарифмирующих транзисторов.

Сумматор 6 осуществляет суммирование входных напряжений дифференциальных операционных усилителей 4ь ..., 4„с выходным напряжением операционного усилителя 1.

Напряжение U< на выходе операционного усилителя 1 равно сумме падений напряжений на эмиттерных переходах транзисторов 2, 3ь ..., 3„, т. е. U> — — (п+1) У „где и— количество дополнительных транзисторов.

Напряжения на выходах дифференциальных операционных усилителей 4ь ..., 4„ равны падениям напряжений на транзисторах Зь ..., 3, и сумма этих напряжений составляет n Ua>. В этом случае на выходе сумматоров 6 появляется напряжение

U„,x= (п+1)Иц,+nUq,= Ug,(2n+1), а это значит, что для достижения необходимого

4 значения U, òðåáóåòñÿ в данном преобразователе по сравнению с прототипом меньше транзисторов и дифференциальных

2и операционных усилителей в =2 раза. и

Таким образом, введение в преобразователь сумматора позволяет уменьшить количество транзисторов и дифференциальных операционных усилителей в два раза по сравнению с прототипом при этом же значении выходного напряжения преобразователя, а следовательно, и точности преобразователя. Так как стоимость преобразователя определяется главным образом стоимостью операционных усилителей и транзисторов, то можно считать, что предлагаемое устройство дешевле в два раза известного устройства (2).

Формула изобретения

Логарифмический преобразователь, содержащий операционный усилитель, вход которого соединен с коллектором основного логарифмирующего транзистора и через входной масштабный резистор с входом преобразователя, база основного логарифмирующего транзистора подключена к шине нулевого потенциала, и дополнительных логарифмирующих транзисторов и и дифференциальных операционных усилителей, эмиттер каждого i-го (i= l, 2, ..., n — 1) дополнительного логарифмирующего транзистора соединен с коллектором (i+1) -ro дополнительного логарифмирующего транзистора и с неинвертирующим входом соответствующего дифференциального операционного усилителя, инвертирующий вход которого соединен с базой соответствующего дополнительного логарифмирующего транзистора и с выходом того же дифференциального операционного усилителя, коллектор первого дополнительного логарифмирующего транзистора подключен к эмиттеру основного логарифмирующего транзистора, а эмиттер и-I o дополнительного логарифмирующего транзистора соединен с выходом операционного усилителя, отличающийся тем, что, с целью упрощения преобразователя, в преобразователь введен сумматор, один вход которого соединен с выходом операционного усилителя, а другие входы соединены с выходами соответствующих дифференциальных операционных усилителей.

Источники информации, принятые во внимание при экспертизе

1. Справочник по нелинейным схемам.

Под ред. Д. Шейнголда. М., «Мир», 1977, с. 189.

2. Заявка Мо 2467049 18-24, кл. G 06G

7/24, 23.03.77, по которой принято решение о выдаче авторского свидетельства.

670941

Редактор И. Грузова

Заказ 1310/15 Изд. Ке 388 Тираж 779 Подписное

ЦНИИПИ НПО «Поиск» Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2

Составитель Н. Балабошко

Техред А. Камышникова

Корректоры: В. Дод и Л. Брахннна