Регистр для аналого-цифрового преобразователя поразрядного уравновешивания

Иллюстрации

Показать всеРеферат

ОП ИСАЙИИ

ИЗОБРЕТЕНИЯ

И АВТОРСКОМУ СВИДИТВЛЬСТВУ

Союз Советских

Социалистииесиих

Республик

<1ц, 674103 (61) Дополнительное к авт. свид-ву (22) Заявлено 16.08.76 (2>) 2398459/18-24 с присоединением заявки № (23) Приоритет

Опубликовано 15.07.79.Бюллетень И 26 (5l) М. К,Z (л 11 С 19/00

Н 03 К 5/156

Гоеударстееииый камитет

СССР пе делам изоеретеиий и еткрытий (53) УДК 681.327.

° 66 (088.8) Дата опубликования описания 18.07.79 (72) Автор. изобретения

А. A. Кузнецов (71) Заявитель (54) РЕГИСТР ДЛЯ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАТРЛЯ

ПОРАЗРЯДНОГО УРАВНОВЕШИВАНИЯ

Изобретение относится к области вычислительной техники и предназначено для использования в аналого-цифровых преобразователях.

Известен регистр для аналого-цифрового преобразователя пора-.рядного уравновешивания (1 ), Однако это устройство имеет недостаточное быстродействие и большое количество компонентов {семь элементов И-HE на один разряд регист-ра) .

Наиболее близким техническим решением к предлагаемому изобретению является регистр для аналого-цифрового преобразователя поразрядного уравновешивания, который содержит разряды, первый вход

Каткдого из которых, кроме первого разряда соединен с первым выходом предыдущего разряда второй вход — со вторым выходом последующего разряда, третий вход - C первой щиной, четвертый входь соответствующей тактовой шиной, причем регистр содержит в старшем разряде троичный триггер, состоящий из элемен«

2 тов ИЛИ-НЕ, элементы ИЛИ-НЕ и триггеры, состоящие из элементов ИЛИ-HE в остальных разрядах, элементы И для связи прямого и инверсного выходов компаратора со вторым и третьим элемента5 ми ИЛИ-HE троичного триггера старшего разряда и с элементами ИЛИ-HE триг геров второго и последующих разрядов; выходы второго и третьего элементов

ИЛИ-HE троичного триггера старшего раз1а ряда соединены со входами элемента ИЛИНЕ второго разряда, выход этого элемента и выходы элементов ИЛИ-HE последующих разрядов соединены со входами триггеров тех же разрядов, состоящих иэ элементов ИЛИ-НЕ, выходы триггера младшего разряда соединены со входами оконечного элемента ИЛИ-НЕ, выход которого соединен через элементы И со входами троичного триггера младшего разряда и со входом первого элемента

ИЛИ-НЕ троичного триггера старшего разряда, выходы первого и второго элементов ИЛИ-НЕ троичного триггера соеди674103

3 иены через элемент И с выходом старшего разряда, а выходы элементов ИЛИНЕ каждого последующего разряда и первых элементов ИЛИ-HE триггеров тех же разрядов соединены через элементы

И с выходными шинами регистра для аналого-цифрового преобразователя поразрядного уравновешивания (2).

Недостатком устройства является малое быстродействие и неустойчивость в Работе, вызванное ограничениями, накладываемыми на цифроаналоговые преобразователи (время срабатывания цифроаналогового преобразователя должно быть значительно меньше времени рассасывания неосновных носителей транзисторов регистра).

Непью изобретения является повышение быстродействия и упрощение схемы.

Указанная цель достигается тем, что уС регистр для аналого-цифрового преобразователя поразрядного уравновешивания, cодержащий разряды, первый вход каждого из которых, кроме первого разряда, соединен с первым выходом предыдущего раэ-25 ряда, второй вход - со вторым выходом последующего разряда, третий вход — с первой шиной, четвертый вход — с соотЬетствующей тактовой шиной, содержит

l1-триггер и элемент 2И, первый вход ко- 30 торого соединен с инверсным выходом

l1-триггера, второй вход — со второй шиной, выход — со вторым входом последнего разряда регистра, первый выход ко1 торого соединен со входом Д-триггера, причем первый вход первого разряда соединен с его вторым выходом. Каждый разряд регистра содержит й- 5 триггер на элементах 2ИЛИ-НЕ, прямой выход которого соединен с первым входом эле- 4р мента ЗИ, инверсный выход — с первым; входом первого элемента 2И, вход сбро-. са — с выходом второго элемента 2И, вход установки — с первым входом разряда, второй вход разряда соединен со 45 вторыми входами элемента ЗИ и первого элемента 2И, третий вход разряда соединен с первым входом второго элемента

2И, второй вход которого соединен с первым выходом разряда и с выходом элемен- go та ЗИ, третий вход которого соединен с четвертым входом разряда, второй выход разряда соединен с выходом первого элемента 2И.

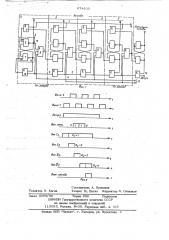

На фиг. 1 представлена схема.регистр» у ра; на фиг. 2 — временная диаграмма работы регистра.

Регистр содержит разряды, каждый иэ которых имеет четыре входа 1, 2, 3 и 4.

Каждый разряд 5 регистра состоит из двух элементов 2ИЛИ вЂ” HE 6 и 7, образующих R-Sтриггер 8,,элемента ЗИ 9 и двух элементов 2И 10 и 11. Прямой выход 12 триггера 8 соединен с первым

Входом элемента ЗИ 9, а инверсный выход 13 — с первым входом первого элемента 2И 10. Выход второго элемента

2И 11 соединен со входом сброса 14, т. е. с поступлением логической «1 на этот вход на прямом выходе триггера буяет логический "0". Первый вход 1 разряда соединен со входом установки 1 5, т, е. с поступлением логической «1 " на хтот вход на прямом выходе будет логическая "1 ". Второй вход разряда 2 сое динен со вторыми входами элемента ЗИ

9 и первого элемента 2И 10. Третий вход разряда 3 соединен с первой шиной

16 и первым .входом второго элемента

2И 11, второй вход которого соединен с первым выходом разряда и с выходом элемента ЗИ 9. Третий вход элемента

ЗИ 9 соединен с четвертым входом 4 разряда, соединенным с соответствующей тактовой шиной 17. Второй выход разряда соединен с выходом первого элемента

2И 10.

Устройство работает следующим образом.

В исходном положении триггеры всех разрядов установлены в состояние «О", т. е. на прямых выходах логическое "0", а на инверсных выходах - логические «1 ".

Независимо от сигнала компаратора (на чертеже не показан) вторые элементы

2И 11 закрыты, (т. е. на выходах логические «О«), так как один из входов соединен с выходом элементов ЗИ 9, которые закрыты из-за наличия сигнала 0" с прямых выходов 12 триггеров 8. Пер вые элементы 2И 10 закрыты, так как логическая «1 " установлена на одном входе. Это устойчивое положение, в ко-тором регистр может находиться длительное время. Процесс преобразования начинается с сигнала "Запуск" по второй шине 1 8 (логическая «1 ", которая поступает на вход первого элемента 2И 10 с приходом инверсного тактового импульса) .

B этом случае логическая «1 " устанавливается на выходах всех первых элементов 2И 10. Логическая «1 с выхода первого элемента 2И 10 старшего разряда устанавливает триггер этого разряда в единичное состояние, остальные триггеры находятся в 0«состоянии, Напря- жение, соответствующее логической «1 старшего разряда регистра U<>, сравни674103 вается с измеряемым напряжением U .

Полагаем, что если U +Uцо, гдето цпнапряжение, поступаемое на компаратор с цифроаналогового преобразователя, то на выходе компаратора логический "0", если Р„ (U на выходе логическая "1 ".

l1oBycTHM, ToUx>a и„, =u „, rAe а, — код первого разряда регистра, тогда на выходе компаратора будет сигнал логического 0", который должен оста- 10 вить триггер в "1 " состоянии, что соотг» ветствует коду а = 1.

Поступивший прямой тактовый импульс открывает элемент ЗИ 9 старшего разряда и на его выходе устанавливается ло- 5 гическая "1 », так как на всех входах элемента логическая "1". Элементы ЗИ 9 остальных разрядов регистра закрыты, так как триггеры этих разрядов регистра находятся в состоянии "0". Логическая "1 с элемента ЗИ 9 старшего разряда речист» ра подается на вход второго элемента 2И

11 этого разряда, тем самым разрешая сигналу с компаратора поступить иа вход сброса три-.гера старшего разряда и на вход установки триггера следующего разряда регистра, Так кака У щ, то с компаратора поступает логический "0 и триггер сохраняет прежнее "1 состояние, что соответствует нужному коду а = 1.

Логическая "1" с выхода элемента ЗИ

9 устанавливает триггер след;,ю.цего разряда регистра 1 состояние, тем самьщ закрывая элемент ЗИ 9 старшего разряда регистра, так как инверсный выход триггера второго разряда регистра соединен со входом первого элемента 2И 10, выход которого соединен со входом элемента ЗИ 9 старшего разряда регистра.

Остальные разряды регистра остаются в

40 прежнем состоянии, так как они управля- ются через элементы ЗИ 9, которые находятся в закрытом состоянии из-за иаличня на входе логического "0", либо с одной иэ 18 шин тактового импульса, ли45 бо с прямых выходов триггеров регистра.

liame происходит, процесс установки кода во втором разряде и установка в 1 состояние следующего разряда. Этот процесс продолжается до тех пор, пока ие будут опрошены все разряды регистра и на выходах регистра установится код.

Одновременно с установкой кода в последнем младшем разряде регистра происхо-дит установка логической «1."- на выходе оконечного триггера, который фиксирует окончание преобразования и блокирует подачу сигнала "запуск".

Повышение быстродействия регистра осуществляется за счет уменьшения общего времени преобразования, так как в течение одного такта происходит опрос двух разрядов регистра. Общее время преобразования 10 — разрядного аналогоцифрового преобразователя может составлять 1 мкс.

Упрощение схемы регистра достигается за счет использования на один разряд регистра R-S триггера, выполненного на элементах 2ИЛИ-НЕ, элемента ЗИ и двух элементов 2И.

Формула изобретения

1. Регистр для аналоге-цифрового преобразователя поразрядного уравновешивания, содержащий разряды, первый вход каждого иэ которых, кроме первого, соединен с первым выходом предыдущего разряда, второй вход — со вторым выходом йоследующего разряда, третий вход— с первой шиной, четвертый вход — с соответствующей тактовой шиной, о т л ич а ю шийся тем, что, с целью повышения быстродействия и упрощения регистра, ои содержит Д-триггер и элемент

2И, первый вход которого соединен с инверсным выходом El-триггера, второй вход — со Ьторой шиной выход — со вторым входом последнего разряда регистра, первый выход которого соединен со входом Q-триггера, причем первый вход первого разряда соединен с его вторым выходом.

2. Регистр по п. 1, о т л и ч и юшийся тем, что каждый разряд регистра содержит R-S триггер на элементах 2ИЛИ-НЕ, прямой выход которого соединен с первым входом элемента ЗИ, инверсный выход - с первым входом первого элемента 2И, вход сброса — с выходом второго элемента 2И, вход установки — с первым входом разряда, второй вход разряда соединен со вторыми входами элемента ЗИ и первого элемента 2И, третий вход разряда соединен с первым входом второго элемента 2И, второй вход которого соединен с первым выходом разряда и с выходом элемента ЗИ, третий вход которого соединен с четвертым входом разряда, второй выход разряда соединен с выходом первого элемента 2И.

Источники информации, принятые во внимание при экспертизе

1, Авторское свидетельство СССР

М 444319, кл. Н 03 К, 13/258, 1972.

2. Авторское свидетельство СССР

% 443483, кл. Н 03 К 13/258, 1971.

674103

Шин

Шина

Запу

Выл Ip

Вых

birr

Оком. npeobp, /

Составитель A. Кузнецов

Техред N. Петко Корректор В. Сининкая

Редактор Н. Коган

Филиал ППП Патент",. г. Ужгород, ул. Проектная, 4

Заказ 409 5/50 Тираж 680 Подписное

LIHHHIM Государственного комитета СССР ио делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5