Реле сопротивления

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ р«675515

Союз Советскнк

Соцналистическик

Республик (61) Дополнительное к авт. саид-ву

4 (22) Заявлено 060577 (21) 2482918/24-07 (51) М. Кл.

Н 02 Н 3/40

Н 01 Н 83/16 с присоединением заявки HP

Государствеииый комитет

СССР по делам изобретеиий и открытий (23) Приоритет

Опубликовано 2507,79. Бюллетень т4о 27 .

Дата опубликования описания 260779 (53) УДК 621. 316. . 925 (088. 8) (72) Авторы изобретения

Я. С. Гельфанд и В.Ш. Перельман

Всесоюзный научно-исследовательский институт электроэнергетики (71) Заявитель (54) РЕЛЕ СОПРОТИВЛЕНИЯ

Изобретение относится к области электротехники и касается релейной з ащиты линий, электропередачи, Известны многозонные дистанционные защиты, измерительными органами кото- 5 рых являются реле сопротивления.

Известны электромеханические реле сопротивления, выполненные по электромагнитному йли индукционному принципам; а также полупроводниковые реле сопротивления (1), (2) и (3).

Принцип действия перечисленных реле основан на сравнении двух величин, разность которых равна нулю при к,э., соответствующем срабатывании, т. е. 15 фактическое измерение сопротивления до места к.з. не производится. Поэтому настройка, проверка и непрерывный контроль таких реле достаточно сложны» 20

Наиболее близким по технической сущности к предложенному является ре- ре сопротивления, основанное на принципе измерения величины сопротивления на зажимах реле (4). Такое выполнение феле обеспечивает возможность постоянной проверки исправности цепей переменного и выпрямленного тока с помощью контроля сопротивления на входе реле в нормальном нагрузочном режиме. Формы напряжений на выходах ин-. теграторов в цепях тока и напряжения одинаковы и представляют собой пилообразные напряжения. Причем время возврата интеграторов в исходное положение (при помощи электронных ключей) должно быть как можно меньше времени нарастания напряжения на выходе интегратора, так как только в этом случае среднее действунхцее или амплитудное значение напряжения на выходе схемы пропорционально сопротивлению на входе реле. Время нарастания напряжения на выходе интеграторов до максимального значения обратно пропорционально величине входного тока, а время возврата в нулевые начальные условие ограничено параметрами интеграторов и ключей, в частности предельной величиной тока и частоты, и практически постоянно. 1Ьэтому при больших величинах токов время нарастания становится соизмеримым с временем возврата, и пропорциональность между выходным напряжением и сопротивлением . на входе нарушается. Изменение напряжения возврата происходит по экспоненте с постояиной времени, определяемой параметрами цепи разряда.

675515,цля уменьшения погрешности реле необходимо параметры этой схемы выбирать так, чтобы время нарастания было достаточно большим по сравнению с временем возврата. Увеличение времени нарастания напряжения снижает

1быстродействие реле, особенно при ма- 5 лых токах.. Таким образом, такое реле имеет повышенные погрешности замера при больших токах и малое быстродействие при малых токах.

Целью изобретения является повышение точности и быстродействия реле сопротивления.

Это достигается тем, что в предложенное реле сопротивления, содержащеЕ промежуточные трансформаторы тока и 15 напряжения, к которым подключены выпрямительные мосты, выходы которых соединены с первыми входами соответствующих интеграторов, соединенным со входами пороговых блоков и электрон- 2О ные ключи, дополнительно введены два. инвертирующих усилителя, элемент временной памяти и нуль-индикатор. При этом выходы выпрямительных мостов че.рез инвертируюцие усилители и электронные ключи подключены ко вторым входам интеграторов, выход порогового блока в цепи тока соединен через элемент временной памяти с управляющими входами обоих электронных ключей, а выход интегратора в цепи напряжения подключен через нуль-индикатор к управляющему входу элемента временной памяти.

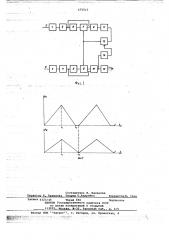

На фиг. 1 показана структурная схема предложенного реле; на фиг, 2формы кривой напряжения на выходе ин-. теграторов.

Реле содержит промежуточные трансформаторы тока и напряжения 1 и 2, выпрямительные мосты 3 и 4 в цепях то-40 ка и напряжения, инвертирующие усилители 5 и б, электронные ключи 7 и 8, интеграторы 9 и 10, пороговые блоки

11 и 12, элемент 13 временной памяти и нуль-индикатор 14. 45

Инвертируюцие усилители 5, б, под" ключенные к выходам выпрямительйых мостов 3, 4, должны иметь стабильный коэффициент усиления, и поворот фазы входного напряжения на 180 . Этим 5О требснаниям удовлетворяют, например, операционные усилители с использованием интегральных микросхем.

Интеграторы 9, 10 имеют по меньшей мере по два входа, один иэ которых 55 соединен с выходом соответствующего . выпрямительного моста, а другой через электронный ключ подключен к выходу иннертируюцего усилителя. Кроме того, интегратор 9 н цепи тока должен иметь. ограничение величины выходного напряжения при одной из полярностей. Напряжение на выходе интегратора 9 может быть только однополярным. ЭлеМент Временной памяти 13, включенный между пороговым блоком 11 и управляющими электродами ключей 7, 8, имеет управляюций вход, при подаче напряжения на который, происходит мгновенный возврат элемента 1 3 в исходное состояние.

Нуль-индикатор 14, подключенный ко в ходу пора го ного блок а 1 2, с раб атыв ает н момент изменения знака входного

1напряжения или в момент перехода этого напряжения через нулевое значение.

Выход нуль-индикатора соединен с управляюцим входом элемента временной памяти.

Схема реле работает следующим образом. От измерительных трансформаторов тока и напряжения к промежуточным трансфорМаторам 1 и 2 подводятся токи и напряжения защищаемого присоединения. Эти неличины выпрямляются мостами 3 и 4, сглаживаются и подаются на первые входы интеграторов 9 и 10. При нулевых начальных условиях электронные ключи 7, 8 закрыты, полярность напряжения на выходах выпрямительных мостов такова, что выходные напряжения интеграторов 9, 10 положительны и линейно нарастают (см. фиг. 2).

В момент времени линейно нарастающие во времени напряжениеД достигает уронняБсп н,при котором порого- . вый блок 11 срабатывает, При этом на выходе элемента временной памяти 13 появляется сигнал, открывающий оба электронных ключа 7 и 8. От инвертируюцих усилителей 5, б -через эти ключи начинают протекать токи ко вторым входам интеграторов 9, 10. Благодаря иннертирующим усилителям 5, б эти токи имеют протиноположное направление по сравйению с токами первых входон интеграторов 9,- 10. Поэтому напряжения Us u Цю начинают снижаться по линейному закону. Пороговый блок 11 возВращается в исходное состояние, а электронные ключи остаются включенными в течение времени, определяемого уставкой элемента 13 временной иамяти. Снижение напряжения U>a происходит примерно с той же скоростью, что и нарастание, а снижение напряжения Цд — . иесколько быстрее, чем нарастание. Необходимо, чтобы при любых погрешностях элементов схемы напряжение Ug достигало нулевого уровня раньше, чем напряжение Гк °

Напряжение на интеграторе 9 не может иметь отрицательного знака, В свяэи с этим, когда в момент времени tp напряжение ддостигнет примерно нулеsoro уровня, дальнейшее его изменение приостанавлйнается. Напряжение U, При этом срабатывает нуль-индикатор 14, что вызывает сброс фременной памяти и запирание электронных ключей 7 и 8. Процесс нарастания напряжений Ug и Р>о на выходах интеграторов начинается снова.

При таком выполнении схемы и соответсгнующем выборе параметров каждый

5 675 период работы интеграторов начинается обязательно с нулевых начальных условий, что исключает накопление зарядов на конденсаторах интеграторов

9 и 10, Амплитуда периодического напряже нияя U о в момент времени 1 определяет- 5 ся следующим образом:

u,. = k. È = ы фу = » у,„„ = и, Как нарастание, так и спад напряжения на выходе интегратора 10 происходят по линейному закону, причем соотношение между скоростяья .нарастания и спад всегда одно и тоже Лоэтому сред-,15 нее значение напряжения Цю,ограничен« нсе прямой нарастания, пропорционально среднему значению этого напряжения, ограниченному прямой спада.По скольку оба средних значения пропорциональны амплитуде U o среднее результирующее выходное напряжение пропорционально сопротивлению на входе реле, как и в прототипе, однако в отличие от последнего отсутствует требование мгновенного возврата интегратора к начальным условиям, В нормальном нагрузочном режиме к реле подводятся номинальное напряжение и ток нагрузки, на интеграторе 10 появляется напряжение, пропорциональ- ЗО ное сопротивлению нагрузки, что можно риэуально проконтролировать, например вольтметром. Пороговый блок 12 не работает °

При к.з. на защищаемом присоедине- 35 нии сопротивление на зажимах реле падает, напряжение на интеграторе 10 снижается, пороговый блок 12,срабатывает и выдает сигнал на отключение электроустановки. 40

Если допустимое по условиям применения операционного усилителя время возврата интегратора к нулевым начальным условкям составляет t минималь» ное время нарастания напряжения в ре- 4ле-прототипе равно около 201, что дает погрешность в замере в зависимости от величины тока около 5%. В предложенном реле .времени, нарастания и спад одинаковы, поэтому при прочих равных условиях допустимая частота напряжения на интеграторе примерно в

515 6

10 раз выше, чем B прототипе.. Поскольку быстродействие реле определяется минимально допустимой частотой выходного напряжения (время нарастания до максимума или заданное время интегрирования), при одинаковом диапазоне токов время действия предложенного реле может быть в 10 раз меньше (беэ учета сглаживающих фильтров), чем в прототипе. Возможно некоторое уменьшение быстродействия за счет повышения точности реле.

Предложенное реле отличается повышенной надежностью и улучшенными основными характеристиками высокой точностью и быстродействием.

Формула изобретения

Реле сопротивления, содержащее промежуточные трансформаторы тока и напряжения с выпрямительными мостами, (выходы последних соединены с первыми входами сбответствующих интеграторов, выходы которых соединены со входами пороговых блоков, и электронные ключи, о т л и ч а ю щ е е с я тем,что, с целью повышения точности и быстродействия, дополнительно введены два инвертирующие усилителя, элемент временной памяти и нуль-индикатор, при этом выходы выцрямительных мостов через инвертирующие усилители и электронные ключи подключены ко вторым входам интеграторов, выход порогового блока в цепи тока соединен через элемент временной памяти с управляющими входами обоих электронных ключей, а выход интегратора в цепи напряжения подключен через нуль-индикатор к управляющему входу элемента временной памяти.

Источники информации, принятые во внимание при экспертизе

1, Чернобровов Н.В. Релейная защита. М., " Энергия, 1974, с. 317.

2. Чернобровов Н.В. Релейная защита, М., Энергия, 1974, с. 319.

3. Чернобровов Н.В. Релейная защита, М., Энергия, 1974, с. 316.

4. Заявка 9 2365721/07, кл, Н 02 Н 3/40р 1976р по которой принято решение о выдаче авторского свидетельства.

675515

t3

Фиг.2

23/45 Тираж 856 Под пи сно е

QHHHIIH Государственного комитета СССР по делам иэобретений и открытий

113035 Москва Ж-35 Ра ская наб

Заявка 43

ППП Патент, г, Ужгород, Ул. Проектная, 4

Филиал

Составитель Л .. Васькова

Редактор Е К ав ова Те О.Андрейко Ко екто Н, Сте