Делитель частоты импульсов

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ (61} Лодоляительиое к авт. свил-sy

Союз Советских

Сойм®лмстнмеовк республик

«i>675603,t и

1 ф)Ц, " " Qc4fj„: у Q(g

3 (51} М. Кл.

Н 03 К 23/02 (22) Задвдаио 14.01.77 (ЯЦ 2442684/18-21 е ирисовдииеэием эвяеки №Реаударатвввньй кащпат.СССР аа делам лзабратщща и бтхращй (23) Приоритет

Оиубликоваио 25.07.79.бюллетень № 27 (53) УДК 621.374,, .3(088.8) йети оиубаиковаиий описания 28.07.79

А. В. Шенин, В. И. Горин и Б. Я. Бурдаев (72) Автори изобретении (7lj Заявитель (54) ДЕЛИТЕЛЬ, ЧАСТОТЫ ИМПУЛЬСОВ

Изобретенйе относится к импульсной . технике.

Известен делитель частоты импуль» сов, содержащий генератор ймпульсов, подключенный на вход счетчика импуль-" сов с общей шйной обнуления, выполнен- я ного, на триггерах, выходы каждого из которых соединены с триггерами разрядными входами дешифратора скважности, другие разрядные входы управления которого соединены с выходами блока управ-16 ления, дополнительный триггер с раздельными входами и дешифратор, входы ко», торого подключены к точкам соединения входов дешифратора скважности с триггер ными разрядными входами и разрядными ъходами управления, при этом выходы" дешифратора скважности подипочены к одному из раздельных входов Дополни тельного дешифратора, а выходы дополнительного дешифратора к другому раз- 6 дельному входу дополнительного тригге ра и . обшей шине обнуления счетчйка .1„.:).

Однако этот делитель обладает недостаточным быстродействием., Наиболее близким по технической сущности к изобретению является дели тель частоты, содержащий логический элемент И НЕ, один вход когорого соединен с входной шийой, второй вход которсго через логический элемент НЕ сое динен с единичным выходом триггера, а выход соединен с входом счетчика импульсов, выходы разрядов которого сое динены с ссихгветствующими входами де . шифратора, другие входы которого соеди нены с шинами управляющих сигналов, а нулевой выход триггера соединен с вхо-! дом сброса счетчика и выходной шиной .денвтели ф).

Недостатком делителя является его сложность

Целью изобретения - упрощение делителя.

Это достигается тем, чго и делите ле частоты, содержащем логический элемент И-НЕ, один вход которого сое675603!

5 входной частоты.

55

3 динен с входной шиной, второй вход которого через логический элемент HE соединей" с едйничнйм выходом трйггера, а выход соединен с входом счетчика импульсов, выходы разрядов которого соединены с соответствующими входами дешифратора, другие входы которого соединены с шинами управляю- . щих сигналов, а нулевой выход триггера соединен с входом сброса счетчика и выходной шиной делителя, выход дешифратора соединен с единичным входом триггера, нулевой вход которого подклю чен к входной шине.

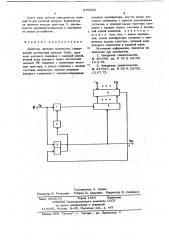

На чертеже дана структурная электрическая схема делителя.

Он содержит логический элемент И-НЕ 1, логический элемент HE 2, счетчик импульсов 3, дешифратор" 4, триггер

5. Входной сигнал подан на входную шину 6, на шийы 7, 8 подан сйгйал уйравления, выходной сигнал снимается с выходной шины 9.

Принцип работы делителя заключается в следующем.

Рассмотрим работу: делителя для коэф фициента деления К равного 15 в деся-Х: тичной системе счисления (К - 15 0 ), при этом разрядность счетчика"импуль-" сов 3 равна четырем.

В исходном состоянии на счетчик 3 записывается код (1000), а триггер 5 устанавливается в нулевое состояние нулевым потенциалом входного сигнала, при этом на шине сброса счетчика импульсов 3 будет присутствовать бездействующий единичный потенциал, а на входе,логического элемента И-НЕ 1 с помощью логического элемента НЕ 2единичный потенциал, разрешающий прохождение положительных (единичного уровня) импульсов входной частоты (8 ) на счетный вход счетчика импульсов 3. На шины управления 7, 8 подает-. ся прямой код управления коэффициентом деления (К - 15 0 - 1 1 1 I g) . дешифратор 4 осуществляет сравнение кода управления коэффициента деления с кодом счетчика. При равенстве ко1 дов на выходе дешифратора 4 возникает нулевой потенциал, а в случае неравен ства кодов на выходе дешифратора 4 присутствует единичный потенциал.

Каждый импульс входной частоты (),. прошедший логический элемент

И-НЕ 1, по заднему фронту увеличивает код, счетчика импульсов 3 на единицу.

По заднему фронту импульса подтверж4 дается нулевое состояние триггера 5

1 нулевым потенциалом паузы между по-ложительными импульсами входной частоты.

После прихода (К -1)-ro импульса по его заднему фронту код счетчика импульсов 3 станет равным коду управления коэффициента деления К, так как исходноа состояние счетчика импульсов задается равным 1000. При этом на выходе дешифратора 4 формируется нулевой потенциал, передний фронт которого устанавливает на единичном выходе триггера 5 единичный потенциал. На выходе логического элемента И-HE 1 возникает нулевой потенциал, запрещающий прохождение импульсов входной частоты на счетный вход счетчика импульсов 3. На нулевом выходе триггера 5 будет присут20 ствовать единичный потенциал, поддерживаемый нулевым потенциалом паузы между (К - 1):ым и К-ым импульсами

Следующий К-й импульс не проходит на счетный вход счетчика импульсов 3, потому, что логический элемент И-НЕ 1 заблокирован. По переднему фронту К-ro импульса триггер 5 установится в еди яичное состояние, так как на его нулевом входе возникает бездействующий единичный потенциал тела импульса, а на единичном входе присутствует нулевой потенциал с выхода дешифратора 4.

Сигнал нулевого потенциала с нулевого выхода триггера 5 по шине сброса записывает в счетчике импульсов 3 код

1000. При этом возникает неравенство кода управления коэффициента деления и кода счетчика 3 и на выходе дешифратора 4 формируется единичный потен» циал.

По заднему фронту К-го импульса триггер 5 устанавливается в нулевое состояние, так как на его нулевом входе возникает нулевой потенциал паузы между К-ыми (К + 1)-ым импуль» сами входной частоты, а на единичном входе присущ ствует бездействующий единичный потенциал с выхода дешифратора 4, При этом логический элемент

И-HE 1 деблокируется.

Таким образом трчггер 5 находится в б в единичном состоянии в течении времени действия К-го импульса и на его нулевом входе формируется отрицательный (нулевого уровня) импульс, длиl тельность которого равна длительности импульсов входной частоты.

675603

Составитель А. Артюх

Редактор Н. Разумова Техред О, Андрейко Корректор В. Синицкая

Заказ, 4343/50 Тираж 1 059 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгоро, ул. Проектная, 4

Далее цикл работы повторяется, каждый К-ый входной импульс выделяется на нулевом выходе триггера 5, оказывается проинвертированным и поступает на выход устройства.

Формула нзобретення

Делитель частоты импульсов, содержащий логический злемент И-НЕ, один вход которого соединен с входной шиной, второй вход которого через логический элемент HE соединен с единичным выходом триггера, а выход соединен с входом счетчика импульсов, выходы разрядов ц йорого соединены с соответствующими <

6 входами дешифратора, другне входы которого соединены с шинами управляющих сигналов, а нулевой выход триггера соединен с входом сброса счетчика и выходной шиной делителя, о т л и ч а юшийся тем, что, с целью упрощения, выход дешифратора соединен с еди;ничным входом триггера, пулевой вход . которого подключен к входной шине.

Источники информации, принятые во внимание при экспертизе.

1. Авгорское свидетельство

No 401005, кл. Н 03 К 23/02, 15.3.72.

2. Авторское свндетельство

% 347927, кл. Н 03 К 23/02, 1 2.07. 72.