Преобразователь кода числа в частоту следования импульсов

Иллюстрации

Показать всеРеферат

Оп ИСАН И Е

ЙЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (i i) 677095

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 11.02.77 (21) 2451681/18-21 с присоединением заявки № (51) М. Кл.з

Н ОЗК 13/02 по делам изобретений (43) Опубликовано 30.07.79. Бюллетень № 28 н открытий (45) Дата опубликования описания 30.07.79 (53) УДК 681.323 (088.8) (72) Автор изобретения

В. Г. Зебрев (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ КОДА ЧИСЛА В ЧАСТОТУ

СЛЕДОВАНИЯ ИМПУЛЬСОВ

ГосУдаРственный комитет (23) Приоритет

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в частотно-цифровых приборах и в качестве магазина частот в измерительной технике.

Известен преобразователь кода числа в частоту следования импульсов, содержащий генератор импульсов, делитель частоты, счетчики, интегратор (1).

Однако это устройство обладает недостаточной точностью преобразования.

Известен преобразователь кода числа в частоту следования импульсов, содержащий счетчики, блок сравнения, генераторы импульсов (2).

Цель изобретения — повышение точности преобразования.

Поставленная цель достигается тем, что в преобразователь кода числа в частоту следования импульсов, содержащий последовательно соединенные генератор импульсов, делитель частоты, первый элемент И и счетчик импульсов, а также триггер управления, выход которого соединен с вторым входом первого элемента И, а входом подключен к выходу управляемого делителя частоты, счетчик обратных значений, вход которого через второй элемент И подключен к выходу генератора импульсов, и блок сравнсния, входы которого подключены соответственно к выходам счетчика обратных значений и счетчика импульсов, выход бло- ка сравнения соединен с вторым входом счетчика импульсов непосредственно, а че5 рез инвертор подключен к выходной шине, дополнительно введены суммирующий счетчик, второй блок сравнения, регистр кода числа, числовой регистр и триггер управления, а также блок считывания. Числовой регистр через блок считывания соединен с входом суммирующего счетчика, второй блок сравнения подключен соответственно к выходам регистра кода числа и выходам старших разрядов суммирующего счетчика.

15 Выход блока сравнения соединен с вторым входом второго элемента И и первым входом дополнительного триггера управления.

Выход дополнительного триггера управления соединен с третьим входом второго элемента И. Второй вход дополнительного триггера управления соединен с входом числового регистра, а второй вход блока считывания соединен с выходом второго элемента И.

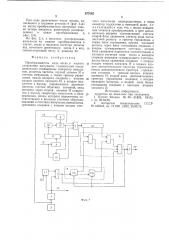

На фиг. 1 изображена структурная электрическая схема преобразователя кода числа в частоту следования импульсов; на фиг.

2, а — и даны временные диаграммы.

Преобразователь кода числа в частоту

30 следования импульсов содержит элементы

677095

И 1, 2, инвертор 3, блок 4 сравнения, генератор 5 импульсов, счетчик 6 импульсов, управляемый делитель 7 частоты, регистр 8 кода числа, числовой регистр 9, дополнительный триггер 10 управления, триггер 11 управления и входные шины 12, 13, 14 из которых первая подключена к входу регистра 8 кода числа, вторая — к входу числового регистра 9 и первому входу дополнительного триггера 10, третья — к одному из входов триггера 11 управления и шиной 15 местного сброса, счетчик 16 обратных значений, блок 17 считывания, суммирующий счетчик 18, второй блок 18 сравнения и выходную шину 20.

На фиг. 2, а показаны импульсы обращения к преобразователю, поступающие через время (ь С поступлением импульса обращения все элементы памяти преобразователя за время 4 обнуляются, при этом на прямых плечах триггеров счетчика 16 обратных значений устанавливаются единичные уровни напряжения.

По шине 12 в регистр 8 кода числа по условию задачи заносится код числа N (N— максимальное число импульсов, которое необходимо получить на выходе преобразователя за цикл преобразования 4). Число разрядов регистра 8 кода числа выбирается на некоторое число порядков больше, чем число N, определяемое требуемой точностью, предъявляемой к равномерности распределения импульсов в цикле преобразования (фиг. 2д, tq).

По шине 13 в числовой регистр записывается текущий код параметра, например приращение скорости, ускорение и т. д.

Код может принимать последовательные значения от 000... 0 до 111... 1, т. е. до максимального кода числа Ж (фиг. 2, б).

Код в числовой регистр заносится по признаку в виде поступающего стробирующего импульса (фиг. 2, в), который поступает на первый вход дополнительного триггера 10 управления, последний изменяет свое состояние, а его выходной сигнал разрешает прохождение импульсов с генератора 5 импульсов на вход счетчика 16 обратных значений через элемент И 2 и одновременно на один из входов блока 17 считывания.

С каждым импульсом информация числового регистра 9 параллельным кодом считывается в младшие разряды суммирующего счетчика 18. Блок 19 сравнения кодов сравнивает число в старших разрядах суммирующего счетчика 18 с числом в регистре 8 кода числа. В момент равенства чисел, записанных в суммирующем счетчике 18 и регистре 8 кода числа блок 19 сравнения кодов формирует сигнал, который одновременно поступает на вход элемента И 2 и второй вход дополнительного триггера 10 управления, который изменяет свое состояние, а сигнал с его выхода запрещает по5

З5

50 ступленпс импульсов в счетчик 16 и на блок 17 считывания.

Число, записанное в счетчик обратных значений, определяет коэффициент пересчета счетчика 6 импульсов на единицу меньше, так как исходное состояние счетчика обратных значений принято единичным.

Признаком начала цикла преобразования является импульс, поступающий по шине 14 на вход триггера 10 управления (фиг. 2, г), который изменяет свое состояние, а сигнал с его выхода (фиг. 2, д) разрешает поступление импульсов с управляемого делителя

7 истоты на вход счетчика 6 импульсов и одновременно на вход блока 4 сравнения.

В тот момент, когда логическое произведение на входах блока 4 сравнения становится равным единице и поступает очередной входной сигнал с управляемого делителя 7 частоты, с его выхода поступает импульс на установочные входы триггеров

21, — 21„ счетчика 6 импульсов и производит его сброс в исходное состояние. Одновременно этот импульс через инвертор 3 поступает по шине 20 на выход преобразователя.

Так как импульсы па вход счетчика поступают непрерывно в течение цикла преобразования (фиг. 2, е), то каждый раз после сброса счетчика 6 импульсов, он вновь начинает отсчитывать импульсы, и процесс повторяется.

После того как управляемый делитель 7 частоты отсчитывает количество импульсов, равное числу Л, записанному в регистр

8 кода числа, на его выходе формируется сигнал, по которому триггер 11 управления возвращается в исходное состояние, а по шине 15 местного сброса происходит обнулcí1c все < остальных элементов памяти преобразователя.

Таким образом, на выход 20 преобразователя поступает количество импульсов, равное числ,, записанному в числовом рсгпстрс 9. Появление первого выходного импульса и промежутки между импульсами на выходе определяются кодом числа, записанного в счстчике обратных значений и частотой управляемого делителя 7.

Частота управляемого делителя определяется где Г,,е„— частота следования импульсов с управляемого делителя частоты;

То — период формирования одного импульса в цикле прсобразования;

/ — время цикла преобразования;

Л вЂ” максимальное число импульсов на выходе преобразователя, которос известно из условия задачи.

677095

При коде десятичного числа четыре, записанного в числовом регистре 9 (фиг. 2,ж) на выход преобразователя поступают только четыре импульса, равномерно распределенных в цикле преобразования t; 5 (фиг. 2,д).

На фиг. 2, з, и показано распределение импульсов на выходе преобразователя в случае, когда в числовом регистре записан код нечетного десятичного числа 5 и код, lo соответствующий числу 1V, равному 24.

Формула изобретения

Преобразователь кода числа в частоту следования импульсов, содержащий последовательно соединенные генератор импульсов, делитель частоты, первый элемент И и счетчик импульсов, а также триггер управления, выход которого соединен с вторым 2р входом первого элемента И, а входом подключен к выходу управляемого делителя частоты, счетчик обратных значений, вход которого через второй элемент И подключен к выходу генератора импульсов, и блок 25 сравнения, входы которого подключены соответственно к выходам счетчика обратных значений и счетчика импульсов, выход блока сравнения соединен с вторым входом счетчика импульсов непосредственно, а через инвертор подключен к выходной шине, отличающийся тем, что, с целью повышения точности преобразования, в него дополнительно введены суммирующий счетчик, второй блок сравнения, регистр кода числа, числовой регистр и триггер управления, а также блок считывания, причем числовой регистр через блок считывания соединен с входом суммирующего счетчика, второй блок сравнения подключен соответственно к выходам регистра кода числа и выходам старших разрядов суммирующего счетчика, выход блока сравнения соединен с вторым входом второго элемента И и первым входом дополнительного триггера управления, выход дополнительного триггера управления соединен с третьим входом второго элемента И, второй вход дополнительного триггера управления соединен с входом числового регистра, а второй вход блока считывания соединен с выходом второго элемента И.

Источники информации, принятые во внимание при экспертизе

1. Патент Японии Хо 49 — 21824, 98(5) с. 31, 09.04.69.

2. Авторское свидетельство СССР

¹ å 444499444444, кл. Н 03 13/02, 25.09.72.

677095 фиг.2

Редактор Е. Караулова Составитель А. Филипов Корректор Л. Брахнина

Заказ 1685/16 Изд. № 475 Тираж 1060 Подписное

НПО «Поиск» Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2