Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

О П И С А Н И Е 1111677098

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

Б АВТОРСКОМУ СВЙДЕТЕДЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 27.О4.77 (21) 2481457/18-21 с присоединением заявки №вЂ”

{51) М Клз

Н ОЗК 13/17

Государственный комитет (23) Приоритет

Опубликовано ЗО.О7.79. Бюллетень № 28

Дата опубликования описания 30.07,79 (53) УДК 681.325 (088.8) ло делам изобретений и открытий (72) Авторы изобретения

1О. Н. Бесов и В. Н. Махов (71) Заявитель Уральский ордена Трудового Красного Знамени политехнический институт им. С. М. Кирова (54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛ

Изобретение относится к радиотехнике.

Известен аналого-цифровой преобразователь, содержащий входное устройство, входной коммутатор, две ячейки памяти, усилитель, управляемый фильтр, генератор эталонов, дискриминатор нуля, блок стабилизации коэффициента, блок стабилизации нулевого уровня, блок управления, блок регистрации и выдачи кода (1).

Однако устройство имеет недостаточную точность, стабильность и ограниченные фупкционà "IE ые возможности.

Известен аналого-цифровой преобразователь, содержащий блок управления, управляющие выходы которого соединены с управляющими входами базовых ячеек памяти, усилителя, генератора эталонов, блока стабилизации нулевого уровня, блока стабилизации коэффициента, управляемого фильтра, блока регистрации и выдачи кода, входного коммутатора и входного устройства, аналоговый выход которого соединен через входной коммутатор с первым аналоговым входом первой базовой ячейки памяти; второй аналоговый вход которой соединен с выходом управляемого фильтра и аналоговым входом блоков стабилизации коэффициента усиления и нулевого уровня; .третий аналоговый вход которой соединен с выходом генератора эталонов; четвертый аналоговый вход соединен с выходом блока стабилизации нулевого уровня, а выход соединен с входом усилителя, первый вход которого соединен с выходом блока стабилизации коэффициента; выход усилителя соединен с входом дискриминатора нуля и входом второй базовой ячейки памяти, выход которого соединен с первыми входами блока управления и блока реги10 страции и выдачи кода, выход второй базовой ячейки памяти соединен с входом управляейого фильтра, логический выход блока регистрации и выдачи кода соединен с логическим входом блока управле15 ния, а второй выход входного устройства соединен с вторым входом блока управления (2).

Однако устройство имеет низкую точность преобразования, плохую стабиль20 ность и ограниченные функциональные возможности.

Целью предлагаемого изобретения является повышение точности, стабильности и расширение функциональных возможностей

25 устройства.

Указанная цель достигается тем, что в аналого-цифровой преобразователь, содержащий входное устройство, входной коммутатор, две базовые ячейки памяти, усили30 тель, управляемый фильтр, генератор эта677098

)О

З0

5»

3 лонов, дискриминатор нуля, блок стабилизации коэффициента, блок стабилизации нулевого уровня, блок управления, блок регистрации и выдачи кода, введены перестраиваемый генератор тока разряда, блок стабилизации тока разряда, блок перестройки коэффициента усиления усилителя, одновибратор, блок выравнивания эталонов, причем выходы блока управления соединены с управляющими входами перестраиваемого генератора тока разряда, выход которого соединен с аналоговым входом первой базовой ячейки памяти, регулирующий вход соединен с выходом блока стабилизации тока разряда, а второй управляющий вход соединен с выходом одновибратора; блока перестройки коэффициента усиления усилителя, выход которого соединен с входом перестройки усилителя; блока выравнивания эталонов, вход и выход которого соединены соответственно с выходом и входом генератора эталонов; блока стабилизации тока разряда; одновибратора; а вторые управляющие входы одновибратора, блока стабилизации тока разряда соединены с выходом дискриминатора нуля.

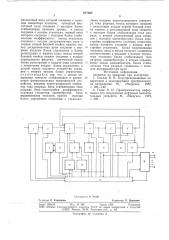

Структурная электрическая схема устройства приведена на чертеже.

Устройство содержит входное устройство 1, входной коммутатор 2, базовую ячейку 3 памяти, усилитель 4, базовую ячейку

5 памяти, управляемый фильтр 6, блок 7 выравнивания эталонов, генератор 8 эталонов, перестраиваемый генератор 9 тока разряда, блок 10 перестройки коэффициента усиления усилителя, дискриминатор 11 нуля, блок 12. стабилизации коэффициента передачи, блок 13 стабилизации нулевого уровня, блок 14 стабилизации тока разряда, одновибратор 15, блок 16 регистрации и выдачи кода, блок 17 управления.

Устройство работает следующим образом.

В исходном состоянии входное устройство 1 разблокировано, входной коммутатор

2 разомкнут. Базовые ячейки 3 и 5 открыты по входу. Управляемый фильтр 6 работает с большой постоянной времени и снимает возбуждение в кодирующем тракте.

3а счет отрицательной обратной связи с коэффициентом К весь тракт приводит себя к стабильному нулевому уровню. Более точно этот уровень подстраивается блоком

13 работающим в промежутках между рабочими состояниями схемы. Блок 16 обнулен.

С приходом исследуемого сигнала У„на вход входного устройства 1 последнее фиксирует его максимальное значение и выдает логический сигнал в блок 17, который выдает подготовительные сигналы и блокирует блок 13, управляемый фильтр 6 переключается в режим с малой постоянной времени, закрывает по входу базовую ячей4 ку 5 и открывает входной коммутатор 2.

Сигнал U через входной коммутатор 2, базовую ячейку 3, усилитель 4 поступает на вход дискриминатора 11, который определяет его знак. Если U„>0 — на вход базовой ячейки 3 подается отрицательный эталон (E,„,), если U,(Π— положительный эталон (+E,„). По знаку остатка определяется старшая разрядная цифра. При (U ) — (Е,„) > О, т. е. (U„) > (Е„), старшая разрядная цифма равна 1, а полученный остаток запоминается первой базовой ячейкой 3. При (U„) — (Е„) (О, т. е. (U„) ( ((Е„), старшая разрядная цифра равна

О. Эталон со входа снимается, и величина

U запоминается. Разрядная цифра записывается в старший разряд блока 16. Блок

16 включается на сложение. Следующей операцией является линейный разряд емкости базовой ячейки 3 путем подключения к ней перестраиваемого генератора 9 с одновременным подсчетом числа единичных приращений на блоке 16. Разряд емкости памяти продолжается целое количество квантов времени, причем время t; после напряжения перехода на емкости через нуль отвечает требованию.

2То> t,) TÄ где t; — текущее время, которому соответствует напряжение остатка U„;

T, — квант времени между импульсами стабильной частоты, которому соответствует изменение напряжения, равное U, (единичное приращение — квант), причем U<, —— (э г)

1V где N=К=2" — полное число единичных приращений, составляющих (Е„);

К вЂ” коэффициент усиления усилителя 4, включенного между ячейками памяти; и — количество двоичных разрядов, причем и может принимать значение О, 1, 2, 3 ... т, Квант времени Т,=

Ф где Т, — время разряда эталона.

В течение времени t; = At„+ T„на емкости выдсляется остаток напряжения U;=

=(ЛУ,, +U,), где ЛУ,, — неизвестный остаток напряжения на емкости, выделяющийся за неизвестную М„, часть кванта времени, причем И. и ЛУ. отвечают условиям

T,)At 0, У,)Ы,, > О.

С переходом напряжения через нуль дискриминатор 11 нуля подготавливает блок

16 для переключения в режим вычитания, создает условия для запуска одновибратора 15, который запускается с началом кванта, и отключает перестраиваемый генератор одновременно с его окончанием, 677098 что позволяет уменьшить погрешность, вносимую инерционностью элементов, коммутирующих ток разряда. Самый последний квант счетчиком не фиксируется. На этом заканчивается первый цикл формирования старших разрядных цифр. Полученный остаток Ug, = — (ЛУ,, + U,) инвсртирустся, усиливается в К раз, запоминается базовой ячейкой 5 памяти и передается на вход базовой ячейки 3. Одновременно с этим сигналом на вход базовой ячейки 3 подается отрицательный эталон — E„„. Их разность — (ЛУ,, + U,) (— К) — Е„=

=+ЛУ,. К запоминается. К емкости памяти подключается перестраиваемый генератор 9, начинается второй цикл работы.

При этом блок 16 работает в режиме вычитания, а вес поступающих единичных приращений в К= V=2" раз меньший, чем в предыдущем цикле. Работа устройства проходит аналогично описанному выше и заканчивается с формированием остатка второго цикла U, = — (ЛУ+У,). Этот остаток инвертируется, усиливается в К раз, а запоминается базовой ячейкой 5 и подается вместе с эталоном — Е„на вход базовой ячейки 3. Разность AU,„К запоминается. На 3-ем цикле работы блок 16 работает в режиме суммирования, вес единичных приращений в N=2" раз меньше веса единичных приращений предыдущего цикла и т. д.

Таким образом, цикл за циклом на блоке

16 формируется цифровой код исследуемого сигнала, причем на первом цикле определяются старшие разряды цифр измеряемого сигнала, а в последующих циклах полученный цифровой код уточняется путем более точного измерения остатка от предыдущего цикла измерения. Точность преобразования увеличивается за счет того, что остаток усиливается и снова измеряется, а разряд емкости осуществляется одним и тем же током на всех циклах.

При этом веса младших разрядов в предыдущем и последующем циклах отличаются в N=2" раз. Цифровой код снимается с т выходов блока 16.

По команде с внешнего устройства или по программе. Устройство изменяет N, т.е. изменяет укрупненное основание, в пределах которого (пределах цикла) осуществляется подсчет единичных приращений.

Для этого блок 17 перестраиваемый генератор 9, блок 10, блок 16 перестраиваются в соответствии с тем основанием, в котором необходимо производить измерение.

Наиболее употребительными значениями укрепленного основания является основания, кратные двум. Другим наиболее употребительным значением укрупненного основания является основание, равное 10.

При этом выходной код будет двоично-десятичным.

При переходе устройства в режим кор50 выходы которого соединены с управляющими входами базовых ячеек памяти, усилителя, генератора эталонов, блока стабили55 зации нулевого уровня, блока стабилиза60

5

10 !

45 рекции корректируется ток разряда, а затем коэффициент передачи тракта. При этом входное устройство 1 заблокировано, входной коммутатор 2 разомкнут, базовая ячейка 5 по входу закрыта, а на вход базовой ячейки 5 подается E„„, запоминается, затем подключается перестраиваемый генератор 9, в блоке 16 осуществляется подсчет единичных приращений. С поступлением Л вЂ” 1-го сигнала блок 16 через блок

17 запускает одновибратор 15, который отключает перестраиваемый генератор 9 одновременно с поступлением N-го импульса на вход блока 16. По знаку остаточного напряжения, определяемого дискриминатором 11, величина тока разряда корректируется с помощью блока 14. После коррекции тока разряда корректируется коэффициент передачи тракта. При этом базовая ячейка 3 закрыта. На емкости хранится нулевое напряжение. По команде блока 17 к емкости памяти подключается переключаемый генератор 9, одновременно запускается одновибратор 15. По истечении одного кванта времени одновибратор 15 отключает перестраиваемый генератор 9. На емкости памяти выделяется единичное приращение напряжения U„. Это напряжение инвертируется, усиливается в К раз, запоминается базовой ячейкой 5 и подается на вход базовой ячейки 3 одновременно с эталоном Е„. Результат сложения Up К вЂ” Е„ через базовую ячейку 3 усилитель 4 поступает на вход дискриминатора 11, где определяется его знак. По знаку разности (Up% — Е,„) блок 12 выдает сигнал для коррекции коэффициента усиления усилителя 4.

Блок 7 как и блок 13 работает в промежутках между рабочими состояниями устройства, при этом результат суммы эталонов подается на вход блока 7. Поскольку один из эталонов берется за основной, то второй по знаку суммы корректируется подгоняется под первый, что позволяет уменьшить дифференциальную нелинейность характеристики преобразования.

Формула изобретения

Аналого-цифровой преобразователь, содержащий блок управления, управляющие ции коэффициента, управляемого фильтра, блока регистрации и выдачи кода, входного коммутатора и входного устройства, аналоговый выход которого соединен через входной коммутатор с первым аналоговым входом первой базовой ячейки памяти; второй аналоговый вход которой соединен с выходом управляемого фильтра и аналоговым входом блоков стабилизации коэффициента усиления и нулевого уровня; третий

677098

Составитель А. Титов

Редактор Е. Караулова

Корректор Л. Брахнина

3аказ 1693/15 Изд. M 463 Тираж 1060 Подписное

НПО «Поиск» Государственного комитета СССР по делам изобретений п открытий

113035, Москва, )К-35, Раушская íào., д. 4/5

Типография, пр. Сапунова, 2 аналоговый вход которой соединен с выходом генератора эталонов; четвертый аналоговый вход соединен с выходом блока стабилизации нулевого уровня, а выход соединен с входом усилителя, первый вход которого соединен с выходом блока стабилизации коэффициента; выход усилителя соединен с входом дискриминатора нуля и входом второй базовой ячейки памяти, выход дискриминатора нуля соединен с первыми входами блока управления и блока регистрации и выдачи кода; выход второй базовой ячейки памяти соединен с входом управляемого фильтра, логический выход блока регистрации и выдачи кода соединен 15 с логическим входом блока управления, а второй выход входного устройства соединен с вторым входом блока управления, отличающийся тем, что, с целью повышения точности стабилизации и расши- 20 рения функциональных возможностей устройства, введены перестраиваемый генератор тока разряда, блок стабилизации тока разряда, блок перестройки коэффициента усиления усилителя, одновибратор, блок 25 выравнивания эталонов, причем выходы блока управления соединены с управляюшими входами перестраиваемого генератора тока разряда, выход которого соединен с аналоговым входом первой базовой ячейки памяти, а регулирующий вход соединен с выходом блока стабилизации тока разряда, а второй управляющий вход соединен с выходом одновибратора; блока перестройки коэффициента усиления усилителя, выход которого соединен с входом перестройки усилителя; блока выравнивания эталонов, вход и выход которого соединены соответственно с выходом и входом генератора эталонов; блока стабилизации тока разряда; одновибратора, а вторые управляющие входы одновибратора, блока стабилизации тока разряда соединены с выходом дискриминатора нуля.

Источники информации, принятые во внимание при экспертизе

1. Смолов Б. В. Полупроводниковые кодирующие и декодирующие преобразователи напряжения. М., «Энергия», 1967, с. 140 — 142, 2. Гитис Э. И. Преобразователи информации для электронных цифровых вычислительных устройств. М., «Энергия», 1975, с. 308.