Цифровая электронная вычислительная машина последовательного действия

Иллюстрации

Показать всеРеферат

ОЙИСАНИЕ

ИЗОБГЕтЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Еаюз Cosovacwx

Ссщиалистических

Республик

<п1678485 (61) Дополнительное к авт. сеид-ву 9 532295 (22) Заявлено 150376 (21) 2327006/18-24

{53)М. Кл.

G F 15/00 с присоединением заявки Но(23) Приоритет

Государственный комитет

СССР но делам изобретений н открытий (53) УДК681 325 (088. 8) Опубликовано 05,08.79. Бюллетень Но 29

Дата опубликования описания 080879 (72) АатарЫ Ю.И. Польский, В П. Захаров, Н.Т. Голец, Ю.В. Таякин, ИЗО6РЕТЕНИЯ Г.П. Липовецкий, В.В. Проценко и A.Ä. Хом (71) ЗаявителЬг (54) ЦИФРОВАЯ ЭЛЕКТРОННАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА

ПОСЛЕДОВАТЕЛЬНОГО ДЕЙСТВИЯ

Работает вычислительная машина следующим образом.

Изобретение относится к области вычислительной техники.

По основному авт .св . Р 532295 из,вестна цифровая электронная вычислительная машина последоватепьнбго действия, содержащая сумматор, четыре регистра сдвига, элементы Й, триггер, блок памяти команд, блок памяти. адресов микрокоманд, память микрокоманд, две группы коммутаторов-, ге-. нератор, три делителя частоты, блок формирования управляющих сигналов, счетчик адреса команд, блок управления счетчиком адреса и дешифраторы кода адреса, адресов микрокоманд и 15 адресов команд.

Недостатком такой машины является низкое быстродействие.

Целью изобретения является повышение быстродействия.

Поставленная цель достигается тем, что предложенная машина содер-. жит дополнительные элементы И, причем первые входы первого и второго дополнительных элементов И подключены соответственно к прямому и инверсному выходам третьего регистра сдвига, а выходы — соответственно ко второму и первому входам сумматора. Первый вход третьего дополни2 тельного элемента И соединен с инверсным выходом четвертого регистра сдвига, а выход — со вторым входом сумматора. Вторые входы первого, второго и третьего дополнительных элементов И соединены с дополнитель.ными выходами памяти микрокоманд.

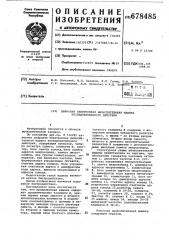

Структурная схема вычислительной машины представлена на чертеже, где обозначены генератор тактовых сигналов 1, делителя частоты 2-4, устройство управления синхросигналами

5, память мнкрокоманд 6, дешифратор адресов микрокоманд 7, коммутаторы

8, блок памяти адресов микрокоманд

9, дешифратор кода адреса синхропрограммы 10, коммутаторы 11, блок памяти команд 12, дешифратор адресов команд 13, счетчик адреса команд 14, устройство управления счетчиком адреса команд 15,регистры сдвига

16 — 18 элементы И 19-26, сумматор 27, регистр сдвига 28, элемент И 29, трнггер 30, элемент И 31, входы 32, 33 машины, выход 34, выходы 35-38 делителей частоты, дополнительные элементы И 39-41.

На вход элемента И 39 поступают сй гнали с прямого выхода третье1р регистра сдвига 18, и при наличии разрешающего сигнала на вторОм входе элемента И 39 с памяти б микрокомайд сигналы с регистра 18 поступают на второй вход сумматора 27.

Сиги алы с ия версн ого выхода регистра сдвига 18 постуйают на вход элемента И 40 и при наличии разрешающего сигнала с памяти микрокоманд 6на первый вход сумматора 27. Сигнал с йнверсного выхода четвертого регистра сдвига 28 поступает на второй вход сумматора 27 при наличии разрешающего сигнала на управляющем входе элемента И 41.

При одновременной подаче разрешающих сигналов на входы элементов

И 26 и 40 на первом входе сумматора организуется дйзьюнкция сигйабж " прямого и инверсного выходов регист ра сдвига 18, а фи подаче сигналов

"на -управляющие входы элемейтов И

39, 24 или 24 и 41 — дизъюнкция сигйалов прямых выходов регистров сдвига 18 и 28 соответственно.

Комбинация уйравляющих сигналов . на элементах И 24-26 и 31-41 позволяют брганизовать микрокоманды выФйтания единицы младшего разряда из соДержимого регистров сдвига 16-18 фпРавляющие сигналы на элементах И

26, 24 и 41), едйницы младшего раз ряда из содержимого регистра сдвига

Предложенное техническое решение при минимальных аппаратурных затратах позволяет резко увеличить число возможных комбинаций. i0

Фсрмула изобретения

Цифровая электронная вычислительная машина последовательного действия до авт.свид. 9532295, о т л и- ч а ю щ а я с я тем, что,, с целью повышения быстродействия, она со."держит"дополнительные элементы И, причем первые входы первого и второго дополнительных элементов И подключены coîòíåòñòâåííî к прямому и инверсному выходам третьего регистра

-Сдвига, а вйходы — соответственно ко второму и=первому входам сумматора, первый вход третьего дополнительного элемента И соединен с инверсным выходом четвертого регистра сдвига, а выход - со вторым входом сумматора, вторые входи первого,. второго и:третьего дополнительных элементов И соединены с дополнительными выходами: памяти микрокоманд.

30

678485 4

28 (управляющйе сигналы на элементах

И 24, 26 и 40), вычитание из содержимого регистров сдвига 16, 18 содержимого регистра 28 сдвига (управляющие сигналы на элементах И 26 и

4l) и др.

Составитель И. Хазова

Редактор Л. Утехина Техред р. Андрейко Корректор И. Муска

Заказ 4561/38 Тираж 780 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4