Усилитель считывания

Иллюстрации

Показать всеРеферат

Союз Советскик

Социалнсти есиии

Республик

< 678656

%" а:

@ Ц

2 (51) М. KJt.

Н 03 К 5/02

В11С 7Ю6 (6)) дополнительное к авт. свил-ву (22) Заявлеио10.12.76 (21)2428442./18-09 с присоединением заявки №

Государотееинвй комитет

СССР оо делом изобретений и открытий (23) Приоритет

Опубликоваио05.08.79,Бюллетень ¹29

Дата опубликования описания06.08 79 (53) УЖ< 681.327, .6{088,8) (72) Авторы изобретения

О. М. Егоров, А. П. Шибулкин, С. Н. виго н Г. Я. Когп (71) Заявитель (54) УСИЛИТЕЛЬ СЧИТЫ ВАНИ Я

Изобретение относится к вычислителт ной технике и может использоваться в запоминающих устройствах на МДП-структурах.

Известен усилитель считывания, содержащий два последовательно соединенных 5 каскада на транзисторах, включенных соответственно по схеме с общим коллектором и общим эмиттером, и источники стробирующих и разрядных импульсов (1).

Однако известный усилитель считыва- та ния имеет низкое быстродействие и низкую помехозащищенность.

Пель изобретения - повышение быстродействия и помехозащищенности.

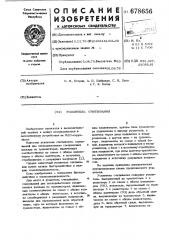

Зля этого в усилитель считывания, содержащий два последовательно соединенных каскада на транзисторах, включенных соответственно по схеме с общим коллектором и общим эмиттером, и источники стробирующих и разрядных импульсов, введены две параллельных цепи обратной связи, одна иэ которых выполнена на транзисторе, включенном по схеме с об2 щим коллектором, причем база транзистора подключена к выходу усилителя, а эмиттер через диод подключен к входу усилители, в другая цепь - на транзисторе, включенном по схеме с общей базой, коллектор которого подключен к входу усилителя, а база - к источнику стробирующих импульсов, при этом эмиттер транзистора, включенного по схеме с общим эмиттером, подключен к источнику разрядных импулт сов.

На чертеже приведена электрическая принципиальная схема предложенного усилителя.

Усилитель считывания содержит усиптт тель, выполненный на транзисторе 1 и резисторе 2 по схеме с общим коллектором (ОК), усилитель, выполненный на транзисторе 3 с резистором 4 по схеме с общим эмиттером (ОЭ),цепь обратной связи, выполненную на транзисторе 5, вклю ченном цо схеме с общим коллектором, диод 6, цепь обратной связи, выполненную на транзисторе 7, включенном по

3 678(), схеме с обшей базой (ОБ), источник разрядных импульсов 8, источник стробирующих импульсов 9, кроме того, клемма 10" вход усилителя, клемма 11 — выход, клемма 12 соединена с шиной питания.

Устройство работает следующим образом.

В исходном состоянии транзистор 7 открыт, и вход усилителя считывания оказывается соединенным с его выходом 10 через небольшое сопротивление транзистора 7. При этом коэффициент усилении равен 1, и усилитель не воспринимает никаких сигналов, поступающих с разрядной шины и попадающих на вход усилителя (клемма 10).

При подаче разрядного импульса положительной полярности (логическая "1 ) иа клемму 10 происходит эапирание транзисторов 1 и 3, вследствие инерционности 0 процесса переразряда разрядной шины запоминающего устройства. В результате этого напряжение на выходе усилителя считывания (клемма 11 )начинает нарастать, стремясь к значению напряжения

25 источника питани я.

При некотором возросшем на выходе усилителя напряжении транзистор 7 запирается, и емкость разрядной шины залозо мииающего устройства быстро переэаряжается через небольшое выходное сопротивление открытого усилителя на транзисторе 5, В режиме считывания информации транзистор 7 заперт. В отсутствие входного

35 сигнала рабочая точка транзисторов 1 и 3 задается током цепи обратной связи через транзистор 5 и диод 6 .

Вследствие действия обратной связи

40 усилитель оказывается нечувствительным к входным импульсам отрицательной полярности, напряжение на выходе усилителя понижается, что приводит к уменьшению отрицательной обратной связи и, следо45 вательно, к резкому увеличению коэффициента усиления усилителя.

Предложенный усилитель считывания позволяет улучшить технические характеристики устройств, в которых он исполу

>6 4 зуется, например, запоминающих устройствах ня М. 1П-структурах, что обусловлено следующим. Во-первых, усилитель быстро восстанавливается после окончания разрядного импульса, убыстряется перезяряд емкости разрядной шины во время действия разрядного импульса. Оба эти фактора повышают быстродействие усилителя.

Во вторых, усилитель нечувствителен к помехам отрицательной полярности, что повышает его помехоустойчивость, В-третьих, напряжение на выходе усилителя при подаче строба не меняется в отсутствие входного сигнала, что исключает образование помех на выходе усилителя.

Формула изобретения

Усилитель считывания, содержащий два последовательно соединенных каскада на транзисторах, включенных соответственно по схеме с общим коллектором и общим эмиттером, и источники стробируюших и разрядных импульсов, о т л и— ч а ю ш и и с я тем, что, с целью п вышения быстродействия и помехозащишенности, введены две параллельных цепи обратной связи, одна из которых выполнена ня транзисторе, включенном по схеме с общим коллектором, причем база транзистора подключена к выходу усилителя, а эмиттер через диод подключен к входу усилителя, а другая цепь - на транзисторе, включенном по схеме с обшей базой, коллектор которого подключен к входу усилителя, а база — к источнику стробируюших импульсов, при этом эмиттер транзистора, включенного по схеме с общим эмиттером, подключен к источнику разрядных импульсов.

Источники информации1 приня;гые во внимание при экспертизе

1. Белов В. М. и др. Быстродействующее оперативное запоминающее устройство на интегральных микросхемах, - Автометрия, 1973, М 3, с. 89, Новосибирс- кое отделение, "Наука".

679656

12

Составитель A. Меньшикова

Редактор Л, Гельфман ТехредН. Бабурка Корректор Н. Горват

Заказ 4581/48 Тираас 1060 Подписное

БНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, ?K-35, Раушская наб., д. 4/5

Филиал ППП Патент", г. Ужгород, ул. Проектная, 4