Устройство для сложения

Иллюстрации

Показать всеРеферат

Союз Советским

СещнизистичФсийх

Респубики (61) Дополнительное к нет. сеид-е (22) Заявлено 140377 (2 ) 2462386/18-?4 (51)М. Кл.2

G 06 Г 7/50 с присовдиивииви Заявки Ио

Государственный комитет ссср оо делам нзобретеии Й и открытий (23) Приоритет

1 (53) УДН681:,32= (088,8) Опубликовано 150879, Б.-оллвтвнь р(о 30

Дата опубликования описания 15,0879

Р.C. Алумя > и С. А. (.!агинян (54 ) УС"."РОЯ2Т эГ1 и 5 СЛОУЯИИЯ

Изобретение относится к области цифровой вычислительной техники и предназначено для вычисления алгвбр:=;.ической суммы двух чисел, предста-.;."ленных в прямом двоичном коде.

Известны устройства, реализующие операции сложения и вычитания двух чисел, содержащие генератор импульсов счета, несколько счетчиков-р"=гистров, а также логические схемы, управляющие процессом вычислений (1), Устройства эти имеют недостатки,. заключающиеся в тси, что в них используется сравнительна большой объем 5 оборудования, а в некоторых слу .аях требуется предварительное преобразование прямых кодов слагаемых н обратный код.

26

Иэ известных устройств наиболее близким по технической сущности является устройство для сложения (2),, Данное устройство содержит два регистра, один из которых счетный, соеди- gg нвнные своими выходами через схему сравнения с входом вентиля, втор:":=. вход которого подключен к ныходу генератора импульсов, а выход -..к выходам счетного регистра, а также третьего, дополнительного счетчика-регистра а

Недостатком данного устройства является то, что оно может опврироватт= только положительными числами, а при вычислении разности необходима предварительная селекция большего нэ чисел, Целью предлагаемого изобретения является расширение функциональных возможностей устройства в смысле обеспечения выполнения действий сложения и вычитания над числами с любыми знаками, то есть воэможность алгебраического сложения.

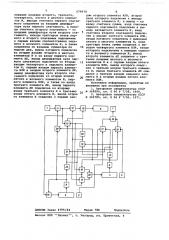

Для достижения поставленной цели, устройство для сложения дополнительно содержит сумматор по модулю дна, триггеры знаков слагаемых и суммы, дешифраторы нуля первого и второго слагаемых, элементы И, ИЛИ и ЯЕ, причем второй вход первого элемента И соединен с выходом первого элемента

ИЛИ, а выход — с первыми входами второго, третьего, четнертсго, пятого и шестого элементов И, ныходы счетчика первого слагаемого соединены со входами дешифратора нуля пвр" ного слагаемого, а ныхсды счетчика меньшим модулями слагаемых, а знак суммы совпадает са знаком слагаемого с большим модулем. Покажем, как данное положение реализуется н предлага" емам устройстве.

Пусть н счетчики 2 и 4 записаны слагаемые с несовпадаюгцими знаками, а счетчик 6 принеден в нулевое состояние. Тогда на выходах дешифраторав 8 и 9 образуется разрешающий уровень напряжения, а на выходе сумматора 10 по мадугпо два образуется запрещающий уровень. Разрешающий уровень с выхода дешифратора 8 подается на элементы И 14 и 17, а также на элементы ИЛИ 20 и НЕ 24. Разрешающий уровень с выхода деы фратора

9 подается на элементы И 15 и 18, а также на элемент ИЛИ 20 и НЕ 26. Запрещающий уровень с выхода сумматора 10 по модулю дна подается на элементы И 12 и 16, а также на элемент

НЕ 25.При этом на выходе элемента ИЛИ

20 образуется разрешающий уровень, а на выходе элемента ИЛИ 21 запрешаю|ций уровень, который падается на вход элемента И 13, на другой вход катараro с выхода элемента HE 25 подается разрешающий уровень. С ныхода элемента HE 25 разрешающий уровень паступает также на вход элемента И 15, Запрегцающий уровень с выхода элемента HE 24подается также на входы элементов И 16 и 18, а запрешающий уровень с выхода элемента HE 26 подается на элемент И 17. Заметим, что на неупомянутые ныше входы элементов И

17 и 18 годаны уровни напряжений единичных выходов триггеров 3 и 5 соответственна. Разрешающим уровнем, снимаемым с выхода элемента ИЛИ 20, элемент И 11 отпирается, обеспечивая поступление испульсов счета на нходы элементов И 12 и 13, заперных уровнями напряжений с выходов суияатара 10 по моцулю два, и элемента ИЛИ

21 соответственно. Импульсы счета поступают также на аткрытыв элементы И 14 и 15, а также на закрытый элемент И 16. С выхода элемента И 14 импульсы счета поступают на счетный вход счетчика 2, а с ныхада элемента,И 15 через элемент ИЛИ 22 — на счетный вход счетчика 4. Тем самым обеспечивается синхронное вычитание единиц с модулей обоих слагаемых.

Как только счетчик одного из слагаеыых обнулится (в этот момент в счетчике другого слагаемого будет сформирована разность модулей слагаемых), счетный вход его запрещающим уровнем, снимаемьж с ныхада соответствующего дешифратора нуля, блокируется, на выходе элемента ИЛИ 21 образуется разрешающий уровень, кото" рый открывает элемент И 13, и импульсы счета через элемент ИЛИ 19 начи.нают поступать на счетный вход счет3 67997

BTQpoI Î слагаемого са входами де шифратора нуля второго слагаемого, выходы триггеров знака пернага и второго слагаемых подключены к первым входам соответственно седьмого и восьмого элементов И, а также соединены со входами сумматора по модулю

5 два, выход которого подключен ко вторым входам второго и шестага эле,ментов И и ко входу первого элемента НЕ, выход дешифратора нуля первого слагаемого подключен ко вторым входам четвертого и седьмого элементов И, первым входом первого элемента ИЛИ и входом второго элемента HE выход дешифратора нуля второго слагаемого подключен ко вторым входам пя- 15 того и васьмага элементов И, первого элемента NJiH а также ка входу третьего элемента НЕ, выход гервого элемента НЕ подключен ко второму входу третьего элемента И и третьему нхо- щ ду пятого элемен-а И, Х а выход — ко входу счетчика суммы, вход счетчика первого слагаемого подключен к ныходу четвертого элемента И, вход счетчика второго слагаемого падктпочен к выходу 25 третьего элемента ИЛИ, входы которого соединены с выходами пятого и шестого элементов И, вход триггера знака суммы соединен с выходом четвертого элемента ИЛИ, входы которого падкгпочены к выходам седьмого и восьмого элементов И, ныход второго элемента НЕ соецинен с третьими входами шестого и восьмого элементов И и с первым входом пятого элемента ИЛИ, выход которого соединен с третьим

35 входом третьего элемен-а И, выход третьего элемента HE coe+HHGI3 c Tpe тьим входом седьмого элемента И и вторым входом пятого элемента ИЛИ, Выход второго элемента И соединен с 40 первым входом второго элемента ИЛИ, второй нхад которого подключен к ныхаду третьего элемента И„

На чертеже представлена структурная схема предлагаемого устройства. 45

Устройство содержит генератор 1 импульсов, вычитающий счетчик 2 первого слагаемого, в который записывается модуль перного слагаемого, триггер 3 знака первого слагаемого, вычитающий счетчик 4 второго слагаемого, в который записывается модуль второго слагаемого, триггер 5 знака второго слагаемого, суммирующий счетчик 6 суммы, триггер 7 знака суммы, дешифраторы 8 и 9 нуля соответственна первого и второго слагаемых, сумматор 10 па модулю два, элементы И 11-18, элементы ИЛИ 19-23, элементы НЕ 24-26.

6О

Работу устройства рассмотрим сначал- для случая, когда знаки слагаемых не совпадают. Заметим, чта н случае алгебраического сложения двух чисел с разными знаками модуль суммы равняется разности между большим и

679978 чика 6 до тех пор, пока счетчик слагаел»ого с большим модулем тоже не обнулится. Тогда на выходе элемента ИЛИ 20 мы получим запрещающий уровень (так как уже на обоих его входах будет запрещающий уровень), и элемент И ll остановит счет. В счетчике 6 получена разность модулей слагаемых.

Допустим, что первым обнуляется счетчик 2. Тогда на выходе дешифратора 8 уровень напряжения становится 10 запрешающим, а на выходе элемента НЕ

24 — разрещающим. Этот уровень подается на вход элемента И 18, на одном из входов которого уже имеется разрешающий уровень с выхода дешифратора 15

9, а на другой вход подан уровень с единичного плеча триггера 5. Если триггер 5 находится в нулевом состоянии (слагаемое с большим модулем, записанное в счетчик 4, положительно), ур элемент И 18 не сработает и тригрег 7 не изменит свого исходного нулевого состояния, и знак суммы получится отрицательным. Заметим, что по обнуле" нии счетчика 4, знак обнулиншегося ранее слагаемого (то есть информация записанная в триггере 3) уже не перепишется в триггер 7, так как элемент И 17 по обнулении счетчика 2 будет сблокиронан запрещающим уровнем напряжения, снимаемым с выхода дешифратора 8. Если же ранее обнулится счетчик 4, разрешающий уровень напряжения с выхода элемента НЕ 26 посредством элементов И 17 и ИЛИ 23 перепишет информацию относительна знака слагаемого, записанного н триггере 3, в триггер 7, обеспечив при этом соответствие знака алгебраической суммы знаку слагаемого с большим модулем, Запрешающий уровень с выхода дешифра- 40 тора 9 при этом сблокирует поступление информации относительно знака слагаемого с меньшим модулем в триггер 7.

Таким образом получаем прямой кад 45 алгебраической суммы.

Рассмотрим теперь случай, когда знаки слагаемых совпадают. Заметим, что в случае алгебраического сложения двух чисел с одинаковыми знаками модуль суммы равняется сумме модулей слагаемых, а знак совпадает сб знаками слагаемых. Данное положение в предлагаемом устройстве реализуется посРедством последовательнога перевода сначала модуля, записан:ного н счетчике 2, затем модуля, записанного в счетчике 4, в счетчик б.

Формирование знака осуществляется при этом так же, как и в случае несовпадения знаков слагаемых. Естественно, что в этом случае н силу последовательности в обнулении счетчикан

2 и 4 знак алгебраической суммы будет совпадать со знаком слагаемого, записанного в триггере 5 (знак слагаемого, записанный в триггере 3, имеет тот же знак) .

При з аписи чисел с совпадающими знаками н счетчики 2 и 4 соответственно уровни напряжений на выходах элементов схемы установятся такими же, как и при описан»,ом вьгше случае несовпадения знаков слагаемых, за исключением уровней напряжений на выходе сумматора 10 по модулю два и, как следствие, на выходе элемента HF.

25, которые меняются на протиноположные. В силу этого на нсе время счета элементы И 13 и 15 блокируются, элемент И 12 отпирается, а элемент И

16 подготавлинается к отпиранию по обнулении счетчика 2. Разрешающий уровень напряжения с выхода элемента ИЛИ 20 отпирает элемент И 11, и импульсы счета поступают на счетные входы счетчиков ? и б. По обнулении счетчика 2 в счетчике б получаем модуль первого слагаемого, при этом высоким уровнем напряжения, снимаемым с выхода элемента НЕ 24, отпирается элемент И 16 и начинается сложение содержимого счетчика 4 (модуля второго слагаемого) с уже введенным н счетчик б модулем первого слагаемого. Когда обнулится счетчик 4, на выходе элемента ИЛИ 20 получаем запрешающий уровень напряжения, который будучи поданню» на вход элемента И 11 останавливает счет, В счетчике б получен прямой дноичный код алгебраической суммы.

Предлагаемое устройство позволяет получать алгебраическую сумму двух днаичных чисел, представленных в прямом двоичном коде„ что не обеспечивается ни н одном из известных устройств для сложения, построенных на счетчиках. Благодаря предложенному техническому решению обеспечивается существенное расширение функциональных возможностей сумматора, в которых нычисления организуются посредстнам счетчикон-регистров.

Фсрмула изобретения

Устройство для сложения, содержащее генератор импульсон, счетчики перного и второго слагаемых, счетчик суммы, первый элемент И, первый вход которого соединен с выходом генератора импульсон, о т л и ч à ю щ ее с я тем, что, с целью расширения функциональных возможностей устройства, заключающемся в возможности алгебраического сложения, устройство содержит дополнительно сумматор по модулю дна, триггеры знаков слагаемых и cyt»tm, дешифраторы нуля первого и второго слагаемых, элементы И, ИЛИ и »Е, причем второй вход первого элемента И соединен с выходом первого элемента ИЛИ, а выход — c

67997

ЦЯИИПИ Эаказ 4795/44

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4 первыми входами второго, третьего, четвертого, пятого и шестого элементов И, выходы счетчика первого слагаемого соединены со входами дешифратора нуля первого слагаемого, а выходы счетчика второго слагаемого — со входами двшифратора нуля второго слагаемого, выходы триггеров знака первого и второго слагаемых подключены к первым входам соответственно седьмого и восьмого элементов И, а также соединены со входами сумматора по 10 модулю два, выход которого подключен ко вторым входам второго и шестого элементов И и ко входу первого элемента НЕ, выход дешифратора нуля первого слагаемого подключен ко вторым входам четвертого и седьмого элементов И, первым входом первого элемента ИЛИ и входом второго элемента НЕ, выход дешифратора нуля второго слагаемого подключен ко вторым входам .пятого и восьмого элементов И, первого элемента ИЛИ, а также ко входу третьего элемента НЕ, выход первого элемента HE подключен ко второму входу третьего элемента И и третьему входу пятого элемента И, выход второго элемента И соединен с первым вхо8 8 дом второго элемейта ИЛИ, второй вход которого подключен к выходу третьего элемента И, а выход — ко входу счетчика суммы, вход счетчика первого слагаемого подключен к выходу четвертого элемента И, вход счетчика второго слагаемого подключен к выходу третьего элемента ИЛИ, входы которого соединены с выходамн пятого и шестого элементов И, вход триггера знака суъвы соединен с выходом четвертого элемента ИЛИ, входы которого подключены к выходам седьмого и восьмого элементов И, выход второго элемента НЕ соединен с третьими входами шестого и восьмого элементов И и с первым входом пятого элемента ИЛИ, выход которого соединен с третьим входом третьего элемента И, выход третьего элемента ЯЕ соединен с третьим входом седьмого элемента И и вторым входом пятого элемента ИЛИ.

Источники информации, принятыв во внимание при экспертизе

1. Авторское свидетельство СССР

Р 368599, кл. G 06 F 7/38, 1969.

2. Авторское свидетельство СССР

В 394785, кл. G 06 F 7/50, 1971.

Тираж 780 Подпи сн ое