Устройство для исправления арифметических ошибок

Иллюстрации

Показать всеРеферат

Союз Советских

С<щиалистических

Республик оо 679985 (61) Дополнительное к авт. свид-ву (22) заявлено 200228(21) 2581721/18-24 с присоединением заявки М (23) Приоритет (51)М. Кл.2

G 06 F 11/08

Государственный кои нтет

СССР но делан изобретений н открытнй (5Ç) УД 681. 325 . (088. 8) Опубликовано 150879. Бюллетень М 30

Дата опубликования описания 150879 (72) Авторы изобретения

В.H. Горшков и Н.Н. Трофимов (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ

АРИФМЕТИЧЕСКИХ ОШИБОК

Изобретение относится к области вычислительной техники и гредназначено для использования в электронных вычислительных машинах, использующих арифметические коды с исправлением ошибок.

Известно устройство для обнаруже-. ния ошибок (1), содержащее инвертор, схему совпадения, триггер, схему исключающее ИЛИ, схему ИЛИ.

Недостатком этого устройства является малое быстродействие.

Наиболее близким по технической сущности к данному изобретению является корректор числа (2), содержащий табличную матрицу синдромов, группу конъюнктивных элементов, реверсивный счетчик, дешифратор, управляющий счетчик, управляющий конъюнктивный элемент, генератор единиц, причем входы реверсивного счетчика соединены с выходами конъюнктивных элементов, соединенных первыми своими входами с выходами табличной мат рицы синдромов, а другими входами— с выходами управляющего счетчика, подключенного через управляющий конъюнктивный элемент к генератору единиц, другой вход того же управляющега конъюнктивного элемента соединен с сигнальным выходом наличия ошибки табличной матрицы синдромов.

Недостатком такого устройства является большой объем оборудования и невысокое быстродействие.

Целью изобретения является повышение быстродействия и сокращение объема оборудования.

Для этого устройства для исправления арифметических ошибок, содержащее блок определения вычетов, блок преобразования сигналов, генератор единиц, двухвходовые элементы И и реверсивный счетчик, причем выходы блока определения вычетов подключены к входам блока преобразования сигналов, выходы первого разряда блока преобразования сигналов соединены со входами первого разряда реверсивного счетчика, входы всех последующих разрядов реверсивного счетчика подключены к выходам,двухвходовых элементов И, первые входы которых соединены с выходами блока преобразования сигналов, содержит элементы HE u трехвходовые элементы И, причем выходы разрядов блока преобразования сигналов, кроме последнего разряда, под67998 ключены ко входам элементов НЕ, выходы элементов НЕ каждого разряда подключены соответственно к первому и второму входу трехвходового элемента И своего разряда, третий вход трехвходового элемента И каждого разряда, кроме последнего, соединен со вторыми входами двухвходовых элементов И, третий вход трехвходового элемента И первого разряда соединен с выходом генератора единиц, третий вход трехвходового элемента И каждого последую-10 щего разряда подключен ко второму входу каждого двухвходового элемента И и к третьему входу трехвходового элемента И последующего разряда, кроме последнего, второй вход каждого 15 элемента И последнего разряда под" ключен к выходу трехвходового элемента И предыдущего разряда.

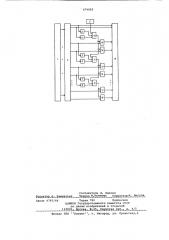

На чертеже представлена схема пред" лагаемого устройства для исправления арифметических ошибок.

Устройство содержит блок 1 определения вычетов, блок 2 преобразования сигналов, элементы 3 — 8 НЕ, генера.тор 9 единиц, трехвходовые элементы

10-12 И, двухвходовые элементы 13-18

И, реверсивный счетчик 19.

Устройство работает следующим образом.

B исходном состоянии на выходах блока определения вычетов, блока преобразования сигналов и на входах реверсивного счетчика коды 0 .

В момент поступления сигналов на выходах всех разрядов блока преоб- 35 разовяния сигналов 2 по выходным сигналам блока 1 определения вычетов формируется код 1 в разрядах, в которых несбходимо прибавить или вычесть единицу. Из -енератора 9 еди- 40 ниц поступает поочередно ) (М -максимальная кратность арифметических ошибок, исправляемых устройством) единичных сигналов.

Пусть, например, на выходах вто" рого разряда блока 2 преобразования сигналов код 1 .

Через двухвходовой элемент И 13 по первому сигналу генератора 9 единиц код 1 поступает на вход реверсивного счетчика.

В реверсивном счетчике 19 производится прибавление единицы и после срабатывания блока 1 определения вычетов и блока 2 преобразования сигналов код 1 остается только на втором выходе третьего разряда.

По второму сигналу генератора

9 единиц код 1 поступает на вход реверсивного счетчика 19 со второго 60 выхода третьего разряда через двухвходовой элемент И 16. Искаженные разряды скорректированы. Блок 1 определения вычетов и блок 2 преобразова5 4 ния сигналов после срабатывания выдают код 0 и по остальным -2 тактовым импульсам прибавления (вычитания) единиц не производится.

Объем оборудования С пр. предложенного устройства равен

Ар. сх орр Вь1ч T.ìс 2 "C2è зй Ht

СРС, С Е е ы

Гд Conp abiu.,С м с. С as< С нв, С p.cu iCrep".q" соответственно объем оборудования блока определения вычетов, блока преобразования сигналов, 1 в входового элемента И, элемента НЕ, реверсивного счетчика и генератора единиц и — количество разрядов кодовой комбинации.

Формула изобретения

Устройство для исправления арифметических ошибок, содержащее блок определения вычетов, блок преобраэо" вания сигналов, генератор единиц, двухвходовые элементы И и реверсивный счетчик, причем выходы блока определения вычетов подключены к входам блока преобразования сигналов, выходы первого разряда блока преобразования сигналов соединены со входами первого разряда реверсивного счетчика, выходы всех последующих разрядов реверсивного счетчика подключены к выходам двухвходовых элементов И, первые входы которых соединены с выходами блока преобразования сигналов, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия и сокращения оборудования, устройство содержит элементы НЕ и трехвходовые элементы И, причем выходы разрядов блока преобразования сигналов, кроме последнего разряда, подключены ко входам элементов НЕ, выходы элементов НЕ каждого разряда подключены соответственно к первому и второму входу трехвходового элемента И своего разряда, третий вход трехвходового элемента И каждого разряда, кроме последнего, соединен со вторыми входами двухвходовых элементов И, третий вход трехвходового элемента H первого разряда соединен с выходом генератора единиц, третий вход трехвходового элемента И каждого последующего разряда подключен ко второму входу каждого двухвходового элемента И и к третьему входу трехвходового элемента И последующего разряда, кроме последнего, второй вход каждого элемента И последнего разряда подключен к выходу трехвходового элемента И предыдущего разряда.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 235399, кл. G 06 F 11/00, 1968.

2. Авторское свидетельство СССР

Р 264786, кл. С 06 F 11/08, 1968.

679985

Заказ 4795/44

Филиал ППП Патент, г. Ужгород, ул. Проектная,4

Составитель Н. Быкова

Редактор Н. Каменская Техред M.Kåëåìåà Кощектор М. ВигУла

Тираж 780 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

11ЗОЗ5 Москва, Ж-35с Ра шская наб.< д. 4l5