Аналоговое запоминающее устройство

Иллюстрации

Показать всеРеферат

( 1." вО СоаЗН - (i 680057

О П И С А Ы "И".Ж

ИЗОБРЕТЕНИЯ

Союз Советскнк

Социалистическими

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 230577 (21) 2489758/18-24 с присоединением заявки М(23) Приоритет— (51)М. Кл.2

6 11 С 27/00

Государственный комитет

СССР но делам изобретений и открытий (53) УДК 681. 327.66 (088,8) Опубликовано 150879. Бюллетень М 30

Дата опубликования описания 180879 (72) Авторы

ИЗОбрЕтЕНИя Н.В. Кукушкина, В.В. Лавров и А.З. Ходоровский

1 (71) ЗаяВИтЕЛЬ Московский ордена Ленина авиационный институт им. Серго Орджоникидзе (5 4 ) АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к области цифровой и вычислительной техники и может быть использовано в контрольно-измерительных системах различного назначения.

Известно запоминающее устройство, содержащее компаратор, ключ, зарядноразрядную цепь с запоминающей емкостью, способное запоминать мгновенные значения функции в заданный момент времени (1).

Известно также аналоговое запоминающее устройство, содержащее основной накопительный элемент, например, конденсатор, одна из обкладок 15 . которого подсоединена к параллельно включенным первому ключу и первому нелинейному элементу„ а также к одному из входов компаратора, другая обкладка конденсатора соединена с шиной нулевого потенциала, шину входного сигнала и шины сигналов ошибки (2) .

Однако описанные запоминающие устройства, обладая ограниченными воэможностями, не позволяют реализовать эффективные методы устранения избыточности во входных цепях контрольно-измерительных и телеметрических устройств ° Для устранения избыточности, при представлении контролируемых процессов параметрами аппроксимирующих полиномов, наименьший объем данных обеспечивается, если передаются параметры полинома наилучшего приближения.

Целью изобретения является расширение области примененния устройства

0 за счет запоминания выделенных иэ полинома сигналов нулевого порядка.

Для этого в устройство введены элементы задержки, сумматоры, вспомогательный накопительный элемент, например конденсатор, ключи, второй нелинейный элемент и фиксирующий элемент, подключенный к выходу устройства и через второй ключ — к одному из входов компаратора, другой вход которого соединен с одной из обкладок вспомогательного конденсатора и с параллельно включенными третьим ключом и вторым нелинейным элементом, выход компаратора подключен к управляющему входу второго ключа и через элемент задержки — к управляющим входам первого и третьего ключей, выходы сумматоров подсоединены к параллельно включенным первому ключу и первому нелинейному элементу и к параллельно вклоченным третьему ключу и второму нелинейному элементу соответственно, шина входногоо си гн ал q соедин ен а с одним и s входов сумматоров, другие входй ког торых подключены к шинам сигналов ошибки соответственно.

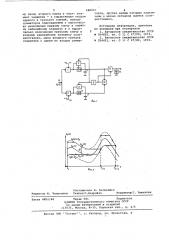

На фиг. 1 изображено предлагаемое устройство, функциональная схема; фиг. 2 — временная диаграмма.

Устройство содержит сумматоры 1 и 2, ключи 3 и 4, нелинейные элементы 5 и 6, основной и вспомогательный элементы 7 и 8, элемент 9 задержки, компаратор 10, ключ 11, фиксирующий элемент 12, шину 13 входного сигнала, шину 14 сигнала ошибкиг шину 15 сигнала ошибки, фиксирующий элемент 12 выполнен на конденсаторе.

В качестве нелинейных элементов

5. и 6 используются диоды,а в качестве накопительных элементов 7 и 8— конденсаторы.

Сигнал аппроксимируется полиномом ступенчатым, наилучшего приближения с некоторой допустимой скцибкой v Для определения координат концов отреэков полинома формируется так называемый коридор ошибок, равный 2vt, и сужающийся до нуля в точке отсчета. Текущие значения верхней границы коридора равны минимальному значению величины vc (t) +

+ v на интервале (;, t j, а нижняя граница равна максимальному значению величины vc (t) — ч„на этом же интервале. Таким образом в начальны1 момент работы t. значения верхней и нижней границ коридора ошибок равны чс (t„) + v и vc (t;) чп ° По мере измейения сигнала формируются новые значения границ коридора ошибок. В момент их совпадения t„.+< значение

V (t ) + Чп ИЛИ V (t) ) ) Vp является ордйнатой, à t„.+„— абсцис-, сой конца отрезка полинома наилучшего приближения нулевого порядка на интервале (t „, t -+ ) .

Предлагаемое устройство работает следующим образом.

Со входа 13 входной сигнал в аналоговой форме подается на входы сумматоров 1 и 2, на которые подаются еще напряжения ошибок + ч„ на сумматор 1, -vä на сумматор 2. На выходе сумматоров 1, 2 формируются сйгналы, соответствующие v (t) ч () - ч „ и ч, () = vc (t) + V>.

B начальный момейт t„. ключи 3 и 4 открыты и конденсаторы 7 и 8 заряжаются до напряжений чс (t)=v< (t)

vce (t) = v<(t) ПОсле этОГО ключи

3, 4 закрываются. Если на выходе сумматора 1 текущее значение чц (t) 7

7 чс (t) то конденсатор 7 через нелинейный элемент 5 заряжается до значениЯ vq (t) и vcy (t) = vq (t) если v„(t) < "сч (t) To чсч (t) ие меняется.

80057

5

35 т.

4

Если на выходе сумматора 2 текущее значение v<(t) < ч (), то конденсатор 8 через нелийейный элемен;

6 разряжается до значения ч () и чсэ (t) = ъg (t) если ч (t) ъ чсз (t) то V«(t) и е меняется .

Текущие напряжения vcz (t) и

vcs (t) сравниваются на компаратор

10. В момент- равенства напряжения на конденсаторах 7, 8 срабатывает компаратор 10, открывается ключ 11 и на фиксирующий элемент 12 запоминается значение ординаты полинома наилучшего приближения на интервале (t<, t „.+ ) . Входной сигнал компаратора 10 через элемент 9 задержки открывает ключи 3 и 4, конденсаторы

7 и 8 заряжаются до значений ч (t„.+„) и ч („ ), процесс повторяется сначала.

Таким образом, предлагаемое запоминающее устройство позволяет выделять и запоминать параметры полинома наилучшего приближения нулевого порядка.

Использование этого устройства на входе аналого-цифровых преобразователей позволяет осуществлять адаптивную выборочную дискретизацию сигнала, при этом значительно сокращается объем данных, необходимых для последующего восстановления сигнала с заданной точностью. Кроме того, при отсутствии фиксатора на выходе устройства, оно может использоваться самостоятельно в качестве адаптивного дискретизатора.

Формула изобретения

Аналоговое запоминающее устройство, содержащее основной накопительный элемент, н апример, к онден сатор, одна из обкладок которого подсоединена к параллельно включенным первому ключу и первому нелинейному элементу, а также к одному из входов компаратора, другая обкладка конденсатора соединена с шиной нулевого потенциала, шину входного сигнала и шины сигналов ошибки, о т л и ч а ю щ е е с я тем, что, с целью расширения области применения устройства за счет запоминания выделенных из полинома сигналов нулевого порядка, в него введены элемент задержки, сумматоры, вспомогательный накопительный элемент, например конденсатор, ключи, второй нелинейный элемент и фиксирующий элемент, подключенный к выходу устройства и через второй ключ — к одному из входов компаратора, другой. вход которого соединен с одной из обкладок вспомогательного конденсатора и с параллельно включенными третьим ключом и вторым нелинейным элементом, выход компаратора подключен к управляющеИсточники информации, прин ятые во внимание при экспертизе

l. Авторское свидетельство СССР

Р 394855, кл. G 11 С 27/00, 1973.

2. Авторское свидетельство СССР

9 354421, кл. G 11 С 27/00, 1972. с з с.

t. иг.2

Составитель И. Вагинайко

Редактор Ю. Челюкапов Техред О. Андрейко Корректор Г. Решетник тираж 681 Подписное

ЦЛИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 4802/48

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4 с

5 680057 6 му входу второго ключа и через зле- торов, другие входы которых подклюмент з адержки — к управляющим входам чены к шинам сигналов ошибки соотпервого и третьего ключей, выхоцы ветственно. сумматоров подсоединены к параллельно включенным первому ключу и первому нелинейному элементу и к параллельно включенным третьему ключу и второму нелинейному элементу соответственно, шина входного сигнала соединена с одним из входов сумма