Устройство для исправления ошибок при итеративном кодировании

Иллюстрации

Показать всеРеферат

се ::з г„ ;,;-. „

W ен тн . ", в "ная

6 а,. ".о, е1;а f 1 с." ф

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Социалистических

Республик

«»680061 (61) Дополнительное к авт. сеид-ву 9 364032 (22) Заявлено 030677 (21) 2492655/18-24 с присоединением заявки ¹ (23) Приоритет

Опубликовано 150879 Бюллетень ¹ 30

Дата опубликования описания 180879 (51)М. Кл.

11 С 29/00

Государственный комитет

СССР по делам изобретений и открытий (53) УДК 681. 327 (088. 8) (72) Авторы

ИЗОбрЕтЕНИя Ю.Н. Вутин, Л.A. Гаврилова и О.Л. Маковеев (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК

ПРИ ИТЕРАТИВНОМ КОДИРОВАНИИ

15

30

Изобретение относится к области запоминающих устройств.

Одно из известных устройств содержит блок хранения информации, блок исправления ошибок для кода, записанного по строкам, подключенный ко входам сумматора по модулю два всех строк кода и перемножителя, к другому входу которого подсоединен выход сигнала вектора ошибки блока исправления ошибок, а выход перемножителя соединен через блок сравнения с блоком номеров, разрешающим запись в этот блок номера строки из блока управления.

При этом выход импульсов кодовой комбинации блока исправления ошибок .соединен со входом полусумматора, другой вход которого через ключ, подсоединенный к выходу блока номеров, связан с выходом сумматора (1).

Недостатками-этого устройства являются большие аппаратурные затраты и невысокая надежность.

Из известных устройств наиболее близким техническим решением к данному изобретению является устройство для исправления ошибок при итеративном кодировании по авт. св. (т 364032, содержащее блок хранения информации с дешифратором адреса, сумматор по модулю два, регистры, ключи и элементы Отрицание равнозначности, при этом выходы блока хранения информации соединены с соответствующими входами сумматора по модулю два, регистра со счетными входами и с первыми входами элемен— тов Отрицание равнозначности, выходы регистра со счетными входами соединены с первыми входами ключей переписи информации, другие входы; которых соединены с выходом дешифратора адреса, а выходы ключей соединены с соответствующими входами регистра запоминания ошибок, выходы которого соединены с первыми входами ключей переписи информации, другие входы ключей соединены с выходом сумматора по модулю два, а выходы ключей соединены со вторыми входами элементов Отрицание равнозначности (2).

Однако, это устройство не позволяет обнаружить ошибки четной кратности в строке. При наличии же ошибой нечетной кратности, находящихся в разных строках, происходит их неправильное исправление, что снижает надежность устройства.

680061

Целью настоящего изобретения является повышение надежности устройства за счет обнаружения ошибок четной кратности в строке и нечетной кратности в разных строках и предотвращение неправильного исправления последних.

Поставленная цель достигается тем, что устройство содержит элементы И и ИЛИ и счетчик, первый выход которого подключен к одному из входов первого элемента И, другой вход которого подключен к выходу сумматора по модулю два, выход первого элемента И соединен с одним из входов ключей переписи информации и со входом счетчика, второй выход счетчика подключен к одному из входов первого элемента ИЛИ, другой вход которого соединен с выходом

Второго элемента И, входы второго элемента И соединены соответственно с первым и третьим выходами счетчика и выходами второго элемента ИЛИ, входы которого подключены к выходам регистра запоминания ошибок.

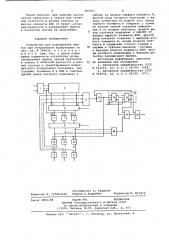

На чертеже изображена блок-схема устройства. Устройство содержит дешифратор 1 адреса, блок 2 хранения информации, сумматор 3 по модулю два, регистр 4 со счетными входами

5, элементы 6 Отрицание равнозначности, ключи 7 переписи информации со входами 8, регистр 9 запоминания ошибок, ключи 10 переписи информации с выходами 11, первый элемент И 12, счетчик 13, состоящий из триггеров

14 и 15, первый элемент ИЛИ 16, второй элемент И 17 и второй элемент

ИЛИ 18.

Первый выход счетчика 13 подключен к одному из входов элемента И 12, другой вход которого. подключен к выходу сумматора по модулю два.

Выход элемента И 12 соединен с одними из входов ключей 10 и со входом счетчика. Выход счетчика подключен к одному из входов элемента ИЛИ 16, другой вход которого соединен с выходом элемента И 17 ° . Входы элемента

И срединены соответственно с первым и третьим выходами счетчика 13 и вы- ходом элемента HJIH 18, входы которого подключены к выходам регистра 9.

Устройство работает следующим образом.

Перед считыванием первого числа из блока 2 разряды регистров 4 и 9 и триггеры 14 и 15 счетчика 13 устанавливаются в нулевое состояние. 3атем в регистре 4 происходит накопление информации, считанной с блока 2, причем последняя строка массива яв ляется контрольной и составлена таким образом, чтобы при отсутствии ошибок все триггеры регистра 4 установились в состояние О.

В случае нечетного количества оши"к в любом из столбцов в соответствующем триггере регистра 4 записывается 1 и по сигналу с выхода дешифратора 1 переписывается через ключи

7 в регистр 9. Нечетное количество ошибок в любой из строк фиксируется сумматором 3 по модулю два, который выполнен из элементов отрицание равнозначности, соединенных между собой в виде пирамиды или цепочки, причем, поскольку при обнаружении первой неисправной строки в устройство.управления машины подается сигнал о прерывании программы по причине неисправности, информация с выходов элементов 6 не используется для дальнейшей работы.

f5 Исправление ошибок и снятие прерывания происходит на следующем цикле обращения к блоку 2 после повтор° ного обнаружения ошибок сумматором

3 по модулю два.

20 При отсутствии неисправных строк триггеры 14 и 15 счетчика 13 будут находиться в нулевом состоянии, что соответствует сигналу О на прямом выходе триггера и сигналу 1 — на ин75 версном.

В случае обнаружения сумматором

3 по модулю два одной неисправной строки триггер 14 счетчика установится в состояние 1, а триггер 15 будет н аходиться в состоянии О. После повторного обнаружения ошибок сумматором 3 сигналом с выхода элемента И 12 разрешается выдача содержимого регистра 9 через ключи 10 на элементы б Отрицание равнозначности

l I

В случае обнаружения двух неисправных строк и более оба триггера счетчика будут находиться в состоянии 1. Сигнал 1 с прямого выхода

40 триггера 15 поступит на вход элемента ИЛИ 16 и на его выходе будет сигнал неисправности.

Сигнал 0 с инверсного выхода триггера 15 счетчика 13 поступит на вход

45 элемента И 12 и запретит прохождение сигнала с выхода сумматора 3 при повторном обнаружении ошибок сумматором, поэтому исправления ошибок не произойдет.

В случае четного количества ошибок в,строке сумматор 3 по модулю два неисправной строки не зафиксирует, поэтому триггеры 14 и 15 счетчика 13 будут находиться в нулевом состоянии и с их инверсных выходов сигнал 1 поступит на входы элемента

И 17. Но в соответствующих триггерах регистра 9 запоминания ошибок в результате контроля по столбцам

60 будет записана 1 и с выхода элемента

ИЛИ 18 сигнал 1 поступит на один из входов элемента И 17, а затем на вход элемента ИЛИ 16. На выходе этого элемента будет сигнал неисправ65 ности °

Формула изобретения

Составитель В. Рудаков

Редактор Э. Губницкая Техред 0.Андрейко Корректор В. Бутяга

Тираж 681 Подписное

ЦНИИПИ Государственного комитета СССР по делам, изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 4802/48

Филиал ППП Патент, r. Ужгород, ул . Проектная, 4

Таким образом, при наличии ошибок четной кратности в строке или нечетной кратности в разных строках на выходе элемента ИЛИ 16 будет сигнал неисправности и исправления ошибок в последнем случае не произойдет.

Устройство для исправления ошибок при итеративном кодировании по авт. св. 9 364032, о т л и ч а ю щ е е с я тем, что, с целью повы° шения надежности устройства путем обнаружения ошибок четной кратности в строке и нечетной кратности в разных строках и предотвращения неправильного исправления последних, оно содержит элементы И и ИЛИ и счетчик, первый выход которого подключен к

680061 ь одному из входов первого элемента Й, другой вход которого поднлючен к выходу сумматора по модулю два, выход первого элемента И соединен с одним из входов ключей переписи информации и со входом счетчика, второй выход счетчика подключен к одному входов первого элемента ИЛИ, другой вход которого соединен с выходом второго элемента И, входы второго элемента И соединены соответственно с

10 первым и третьим выходами =четчика и выходом второго элемента ИЛИ, входы которого подключены к выходам регистра запоминания ошибок.

Источники информации, принятые

15 во внимание при экспертизе

1. Авторское свидетельство СССР

9 251253, кл. G 11 С 29/00, 1968.

2. Авторское свидетельство СССР

М 364032, кл. G 11 С 29/00, 1971.