Устройство задержки импульсов

Иллюстрации

Показать всеРеферат

Союз Соввтскн»

Соцналмстм чески»

Республик

onисАнИЕ

ИЗОБРЕТЕН >

К АВТОРСКОМУ СВИДВТИДЬСТВУ (61) Дополнительное к авт. свид-ву(22) Заявлено27.05.77 (21)2488788/18-21 (it 680163

2...

;3 ( (51) М. Кл.

Н 03 К 5/13 с присоединением заявки №H 03 К 17/28

Государстве««ый «оы«твт

СССР во делам взоорвтвн«й и открыткй (23) ПриоритетОпубликовано15.08.79. Бюллетень № 30

Дата опубликования описания17.08.79 (53) УДК 621.374..28(088.8) Е. С. Сельков, В. M. Гусаков, A. И. Дементьев и А. В. Зеленцов (72) Авторы изобретения (71) Заявитель (54) УСТРСЙСТВО ЗАДЕРЖКИ ИМПУЛЬСОВ

Изобретение относится к импульсной технике, а именно к аналоговым устройст-. вам задержки импульсов.

Известно устройство задержки импульсов на цепочке последовательно включенных одноканальных полевых транзисторов с изолированным затвором. Затвор каждого транзистора в цепочке соединен со стоком того же транзистора, а задерживаемый импульс подается на один конец этой цепочки, к другому концу которой подклю- 10 чен конденсатор. При подаче импульса на вход такой цепочки выходное напряжение на стоке какого-либо из транзисторов появляется через время, необходимое для заряда емкостей затворов всех транзисто- !5 ров от начала цепочки до точки сьема выходного напряжения. Подключая выход к различным точкам схемы, можно изменять время задержки переднего фронта. Для формирования заднего фронта импульса и его задержки существует специальная paw рядная цепь, управляемая разрядным импульсом и представляющая собой цепочку последовательно включенных полевых транзисторов с изолированным затвором. Затворы этих транзисторов соединены параллельно и на них подается разрядный импульс. Разрядная цепь подсоединена к задерживающей цепи параллельно (11

К недостаткам этой схемы относятся зависимость выходного напряжения от времени задержки, необходимость форл ирования специального разрядного импульса для приведения схемы в исходное состояние, малое время задержки переднего фронта импульса, так как в качестве элементарной ячейки задержки используется собственная емкость затвора полевого транзистора.

Известно также устройство задержки импульсов, содержащее нагрузочный конденсатор, первая обкладка которого подключена к общей шине, а вторая - к одному выводу цепи заряда, состоящей из последовательно соединенных МДП транзисторов одного типа проводимости, затвор каждого из которых подключен через пер680163

3 вый конденсатор связи к стоку, и цепь разряда, включенную между второй обкладкой нагрузочного конденсатора и общей шиной (2)

Однако известное устройство имеет недостаточно высокое максимальное время задержки и время задержки зависит от амплитуды выходного сигнала.

Бель изобретения - увеличение максимального времени задержки и исключение зависимости задержки от амплитуды выходного сигнала — достигается тем, что в устройство задержки импульсов, содер жащее нагрузочный конденсатор, общую шину, цепь заряда из последовательно соединенных МДП транзисторов одного типа проводимости и цепь разряда, введена ши/ на питания, подключенная к другому выводу цепи заряда, а цепь разряда выпол нена в виде последовательйо включенных

МДП транзисторов другого типа проводимости, затвор каждого; из которых через второй конденсатор связи подключен к истоку, причем затворы всех МДП транзисторов цепей заряда и разряда объединены и подключены к входному выводу устройства.

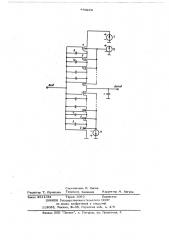

Принципиальная схема устройства задержки изображена на чертеже.

B процессе работы устройства, когда напряжение на его входе равно нулю, все р-канальные MQTI транзисторы открыты, и-канальные закрыты и конденсатор 1

35 подключен к шине питания 2. Если на вход схемы подать положительный импульс с амплитудой, большей разности напряжения .питания и величины порогового напряжения р-канальных МДП транзисторов, то

4О д -канальный МДП транзистор 3 открывается, а р-канальные МДП транзисторы последовательно закрываются, конденсатор 1 отключается от шины и общего провода и на нем сохраняется высокий

45 потенциал, Конденсатор 5 начинает заряжаться током открытого транзистора

3 и, когда разность потепциалов на нем достигнет порогового напряжения и-канального МДП транзистора 6, он откры50 вается и начинается заряд конденсатора 7, Этот процесс повторяется до тех пор, пока не откроется последний в цепочке п-канальный транзистор 3, тогда происходит разряд конденсатора 1 через откры55 тые транзисторы. Задержка переднего фронта определяется амплитудой входного импульса, емкостью конденсатора, промежутком исток-затвор транзистора, поро4 говым напряжением, крутизной и числом транзисторов в цепочке.

В момент включения входного импульса И -канальные МДП транзисторы последовательно закрываются, а МДП транзис» тор 4 открывается, конденсатор 1 оказывается:отхлюченным от общего провода и шины питания 2 и на нем сохраняется нулевой потенциал. Конденсатор 8 начинает заряжаться тохом открытого транзистора

4 и, когда разность потенциалов на нем достигнет порога открывания транзистора 9, он открывается и начинается заряд конденсатора 10. Этот процесс повторяется до тех пор, пока не откроется транзистор 4, тогда конденсатор 1 начинает заряжаться через открытые р-канальные

МДП транзисторы до напряжения шины питания 2. Задержка заднего фронта зависит от амплитуды входного импульса, напряжения питания, емкости конденсатора промежутка исток-затвор р-канального

МДП транзистора, порогового напряжения, крутизны и числа транзисторов в цепочке.

Задержка переднего и заднего фронтов осуществляется независимо и ее можно сделать любой в диапазоне до И .„или

hK, где М, 4 — число транзисторов, — задержка на одном транзис» и ) торе соответственно для переднего и заднего фронтов.

Если не принимать в расчет парамет- . ры транзисторов и внешние напряжения, то .С „и Г зависят только от емкости конденсаторов, шунтирующих промежутки исток-затвор транзисторов, т.е. для расчета на требуемое время задержки необходимо оптимально выбрать значение емкости указанных конденсаторов и количество транзисторов в цепочках. B общем случае значение емкостей указанных конденсаторов может быть различным не только для разных цепочек, но и для одной иепочки.

Для регулирования времени задержки как переднего, так и заднего фронтов в некотором диапазоне может быть использовано смешение подложек. Известно, что при увеличении смещения на подложке полевого транзистора с изолированным затвором его пороговое напряжение увеличивается, а крутизна уменьшается. Для данкой схемы это приводит к, тому, что время задерласи увеличивается. Зто удобный способ независимого регулирования времени задерхаси переднего и заднего фронтов импульса, развязанный от входа и выхода

680163

5 схемы. Как указывалось выше, задержку можно изменять, регулируя амплитуду входного импульса или напряжение ясточt ника питания, но при этом происходит одновременное изменение задержки как переднего, так, и заднего фронтов импульса.

Причем если одна из задержек при этом увеличивается, то другая, уменьшается и изменения происходят по разнйм законам.

Задержка цереднего фронта;является не- 1О линейной функцией амплитуды входного напряжения, задержка заднего фронта линейно зависит от амплитуды входного напря кений, Подложки транзисторов одного типа проводимости на чертеже соединены вместе и подключены к источнику смещения

11 для MQFI транзисторов с и-каналом и к источнику смешения Х2 для МДП транзисторов с р-каналом. Это не единствен20 ный .способ подключения подложек. На каждую из них может быть подано автономное смещение. Кроме того, подложка каждого из транзисторов может соединять25 ся с соответствующим электродом источника питания или с истоком того же транзистора.

Из анализа работы схемы следует, что задержанный импульс инвертирован относительно входного. Поэтому, если требуется получить задержанный импульс без инверсии, на выходе схемы следует включить инверт ор.

Изменение устройства по сравнению с

HBBBcTBbIM дало качественное изменение принципа задержки импульса.

В данном устройстве .задержки-те же транзисторы работают как активные элементы в переключающем режиме, поэтому недостатки, отмеченные выше для известного устройства,, устранены.

Ф ормула и зобретения

Устройство задержки импульсов, содержащее нагруэочный конденсатор, первая обкладка которого подключена к общей шине, а вторая — к одному выводу цепи заряда, состоящей из последовательно соединенных МДП транзисторов одного типа проводимости, затвор каждого из которых подключен через первый конденсатор связи к стоку, и цепь разряда, включенную между второй обкладкой нагрузочного конденсатора и общей шиной, о т л и ч а юш е е с я тем, что, с целью увеличения максимального времени задержки и исключения зависимости времени задержки от амплитуды выходного сигнала, в него.введена шина питания, подключенная к другому выводу цепи заряда, а цепь разряда выполнена в виде последовательно включенных МДП транзисторов другого типа проводимости, затвор каждого из которых через второй конденсатор связи подключен к истоку, причем затворы всех MQfI транзисторов цепей заряда и разряда. объединены и подключены к входному выводу устройства.

Источники информации, принятые во внимание при экспертизе

1. Патент США % 3638047, кл. 307-293, 07.11.72.

2. Патент США No 358408, кл. 507-276, 14.03.71. О163

Составитель П. Лягин

Редактор Т, Юрчикова ..Техред М. Келемеш Корректор М. Вигула

Закав 4811-/54 Тираж 1060 Подписное

GHHHllH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент", г. Ужгород, ул. Проектная, 4