Логический элемент

Иллюстрации

Показать всеРеферат

Союз Советскии

Социалистимвскик

Республик

ОП ИСААКИЕ

И3ОБВЕТЕН ИЯ

К АВТОВСКОМУ СВИДИТВЛЬСТВУ

680123! !, ( (6l) Дополнительное к авт. свиа-ву (22) Заявлено 06,05 77 (21) 2485144/18-21 (51) М. Кл

Н 03 К 19/08 с присоединением заявки №2482822/18-21 (23) Приоритет

Гееударственнвй комитет

СССР аа делам иэобретений и открытий (53) ; УДК 621.374 (088.8) Опубликоваио15.08.79.Бюллетень № 30

Дата опубликования описания 17.08.79 ! (72) Автор изобретения

А. Н. Кармазинскйй

Московский ордена Трудового Красного Знамени инже нерио-фи зический институт (71) Заявитель (54) ЛОГИЧЕСКИЙ ЭЛЕМЕНТ

Изобретение относится к области вычислительной техники, электроники, автоматики и может быть использовано, в частности.при создании больших интегральных схем на дополняющих МДП-транзисторах. е

Известны инверторы на дополняющих

МДП-транзисторах и логические элементы„ выполняющие различные логические функции, существенными признаками которых является наличие пар дополняющих транзисторов, м и р-канальных, в которых сток те-канального транзистора подключен к стоку р-канального транзистора и к выходу элемента, затвор тэканального транзистора подключен к затвору р-канального тран.т5 зистора и к входу элемента, истоки тт-канальных транзисторов и их подложки подключены к общей шине, истоки р-канальных транзисторов и их подложки подключены к плюсовой шине.

Многовходовые логические элементы содержат группы последовательно и параллельно включенных транзисторов с каналами дополняющих типов проводимости, причем группе последовательно включенных транзисторов с каналами еэ-типа соответствует группа р-канальных транзисторов, включенных параллельно, и наоборот. Каждому и-канальному транзистору соответствует р.-канальный транзистор, затворы которых подключены к входу элемента fl).

Недостатком известных логических элементов является наличие только одного выхода.

Известен логический элемент, содержащий три инвертора на дополняющих МДПтранзисторах, первый инвертор подключен между шинами источника питания, второгомежду одной из шин источника питания и выходом первого, а инвертора, причем вход и выход каждого из инверторов являются соответственно входом и выходом элемента, в каждом из инверторов подложки тЭ-канальных транзисторов подключены к общей шине, а подложки р-канальных транзисторов - к плюсовой шине 21 .

6801

Недостатком известного логического элемента является реализация функций только одного типа (НЕ-И либо НЕ-ИЛИ).

Целью изобретения является расширение функциональных возможностей элемента.

Йля этого в логическом элементе, содержащем три инвертора на дополняющих

МЙП-транзисторах, в котором первый инвертор подключен между шинами источника питания, второй - между выходом пер- !О вого и одной из щин источника питания, вход и выход каждого из инверторов являются, соответственно, входом и выходом элемента, в каждом из инверторов подложки Ф;канальных транзисторов подключены к общей шине, а подложки р-канальных транзисторов.— к плюсовой шине, третий инвертор включен между выходами первого и второго инверторов.

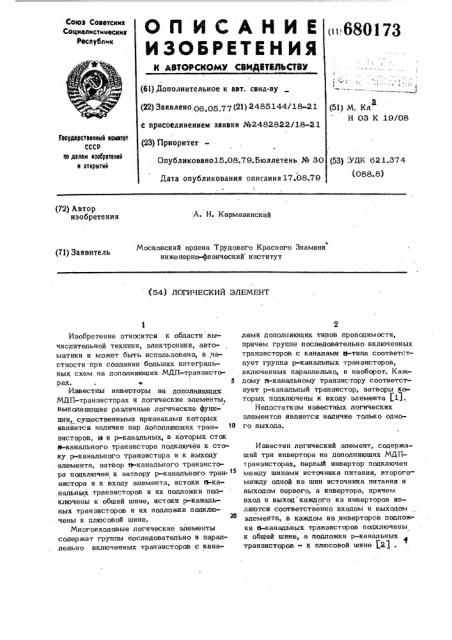

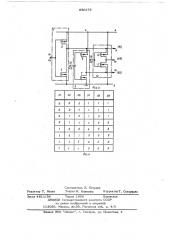

На фиг. 1 представлена принципиальная 40 схема предлагаемого логического элемен- та; на фиг. 2 — таблица истинности поясняющая работу элемента; на фиг. 3— принципиальная схема логического элемен25 та; на фиг. 4 - таблица истинности, поясняющая работу элемента, принципиальная схема которого изображена на фиг. 3, Первый инвертор 1 на дополняющих

МДП-транзисторах 2 и 3 подключен между

30 плюсовой шиной 4 и обшей шиной 5, второй инвертор 6 на дополняющих МДП-транзисторах 7 и 8 подключен между плюсовой шиной 4 и выходом 9 первого инвертора 1 третий инвертор 10 на дополняюI

35 щих МЙП-транзисторах 11 и 12 включен между выходом 9 первого инвертора 1 н выходом 13 второго инвертора 6, входы 14,15 и 16 инверторов 1, 6 и 10 соответственно являются одновременно входа- 40 ми элемента, на которые поступают соответственно входные переменные Xl,Х2 и

ХЗ, выходы 9,13 и 17 инверторов 1,6 и

10 соответственно являются одновременно выходами элемента, на которых выпол- 45 няются функции Уl, У2 и УЗ. Подложки

tl -канальных транзисторов 2,7 и 11 подключены к общей шине 5, подложки

-канальных транзисторов 3,8 и 12 подключены к плюсовой шине 4.

$0

Второй инвертор 6 (фнг.З) подключен к другой шине источника питания, в частности — к общей шине 5.

Логический элемент работает следующим образом.

Если на вход 14 (фнг. 1) поступает напряжение логического нули, то -канальный транзистор 2 закрыт, à р -канальный транзистор 3 открыт, на выходе

73

4 появляется напряжение логической единицы, если на вход 14 поступает напряжение логической единицы, то h.-канальный .транзцетор 2 открыт, а ь -канальный

J. транзистор 3 закрыт, и на выходе 9 возникает напряжение логического нуля. Следовательно, на выходе 9 выполняется функция НЕ от входной переменной Xl на входе 14-

33 = xi

Изменение значения напряжения на выходе 13 происходит только в том случае, если на входе 14 появляется напряжение логической единицы и соответственно на выходе 9 — напряжение логического нуля.

В этом случае при поступлении на вход

15 напряжения логической единицы на выходе 13 устанавливается напряжение логического нуля, Если на входе, 15 появляется напряжение логического нуля, то на выходе 13 устанавливается напряжение логической единицы, последнее устанавливается на выходе 13 всегда, независимо от напряжения на входе 15 при напряжении логического нуля на входе 14.

Таким образом, на выходе 13 выполняется функция -HE от двух входных переменных Xl и Х2 соответственно на входах 14 и 15.

У2 = Хl Х2, Напряжение на выходе 17 соответствует напряжению логического нуля в тех. случаях, когда на входах 14 и 16 возникает напряжение логической единицы, или, когда напряжение логической единицы поступает на входы 14 и 15. Во всех остальных случаях на выходе 17 устанавливается напряжение логической единицы.

Например, при поступлении на вход 14 напряжения логической единицы, а на входы 1 5, 16 - напряжения логического нуля открыты транзисторы 2,8 и 12, а закрыты транзисторы 3,7 и 11. На выходах

13 .и 17 устанавливаются напряжения логической единицы, так как потенциал плюсовой шины передается через открытый транзистор 8 на выход 13 и через открытый тра н вист ор 12 на выход 1 7.

Таким образом, на выходе 17 выполняется функция от трех входных переменчых

УЗХ1+Х2 - ХЗ.

Если второй инвертор 6 подключить к об- щей шине 5 (фиг. 3), то в соответствии

680173

5 с таблицей истинности (фиг. 4) на выходах 9,13 и 17 соответственно выполняют ся нкции

Фу

3 У1 *Х1

У2=Х1+Х2

УЗ=эХ1 Х2 ХЗ, Таким образом, данный элемент выполняет три различные функции от трех входных переменных, что расширяет его функциональные возможности по сравнению с известными элементами.

Ф ормула изобретения

Логический элемент, содержаший три инвертора на дополняюших MQH-транзиоторах, первый инвертор подключен между шинами источника питания, второй - меж1 пу выходом первого и одной из шин источника питания, вход н выход каждого из инверторов являются соответственно входом и выходом элемента, в каждом из инверторов подложки A-канальных .транзисторов подключены к обшей шине, а подложки р-канальных транзисторов — к плюсовой шине, о т л и ч а ю ш и и с я тем, что, с целью расширения функциональных воэ>О можностей, третий инвертор включен между выходами первого и второго инверто ров.

Источники информации, принятые во внимание при экспертизе

1. Букреев И. Н. и др. Микроэлектронные схемы цифровых устройств. М., Сов. радио, 1973.

2. Патент Великобритании ¹ 1300495, кл. Н3Т, 1972.

680173

Г 1

Уг) Составитель Л. Петрова

Техред M. Келемеш Корректор Т. Скворцова

Редактор Т. Янова

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

Заказ 4811/54 Тираж 1060 Подпис н ое

БНИИПИ Государственногь комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5