Устройство для контроля последовательности чередования аналоговых сигналов

Иллюстрации

Показать всеРеферат

(72) Авторы изобретения

B. С. Алешин, В. М. Воробьев и Г. А. Гоманчук (7I) Заявнтель (S4) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОСЛЕДОВАТЕЛЬНОСТИ

ЧЕРЕДОВАНИЯ АНАЛОГОВЫХ СИГНАЛОВ

Изобретение относится к устройствам контроля систем связи и может использоваться в автоматике и вычислительной технике.

Известно устройство для контроля последовательности чередования аналоговых

5 сигналов, содрежащее И блоков обработки аналогового сигнала, каждый из которых содержит первый и второй двухвходовые элементы И-НЕ, первые входы ко1О торых объединены и являются входом блока обработки аналогового сигнала, причем выход первого элемента И-НЕ подключен к второму входу второго элемента И-НЕ а каждый вход предыдуще15 го блока обработки аналогового сигнала объединен с вторым входом первого элемента И-НЕ последующего блока обработки аналогового сигнала, выход каждого второго элемента И-НЕ является выходом блока обработки аналогового сигнала, и блок отображения информапии (1).

Однако известное устройство имеет невысокую точность контроля, так как в нем фиксируется лишь факт появления сигнала ошибки, а не пропуск каких-либо аналоговых сигналов в чередовании и определение того сигнала, на котором произошло нарушение последовательности чередования.

Целью изобретения является повышение точности контроля.

Для этого в устройство для контроля последовательности чередования аналоговых сигналов, содержащее N блоков обработки аналогового сигнала, каждый из которых содержит первый и второй двухвходовые элементы И-НЕ, первые входы которых объединены и являются входом блока обработки аналогового сигнала, причем выход первого элемента И-HE подключен к второму входу второго элемента И-НЕ, а каждый вход .предыдущего блока обработки аналогового сигнала объединен с вторым входом первого элемента И-НЕ последующего блока обработки аналогового сигнала, выход каждого второго элемента И-FIF является выходом

680183

3 блока обработки аналогового сигнала, и блок отображения информации, введены низкочастотный генератор, Н инверторов, М третьих и N четвертых двухвходовых элементов И-НЕ, при этом выход каждого блока обработки аналогового сигнала подключен через инвертор к первому входу одного из И третьих элементов И-НЕ, вторые входы которых объединены с выходом низкочастотного генератора, пер- 10 вый вход каждого из N четвертых элементов И-НЕ соединен. с входом соотвеч ствующего блока обработки аналогового сигнала, а второй вход — с выходом одного иэ К -третьих элементов И-НЕ, выход каждого из М четвертых элементов И-HE подключен к соответствующему входу блока отображения информации.

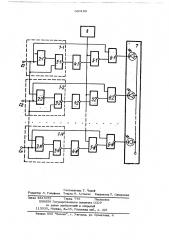

На чертеже представлена структурная электрическая схема предложенного устройства.

Устройство дпя контроля последователь ности чередования аналоговых сигналов содержит N блоков обработки аналогового

25 сигнала 1 (1-1...1- И), каждый иэ которых содержит первый 2 (2-1...2- и ) и второй 3 (3-1 ...3- N ) двухвходовые элементы И-НЕ, 8 инверторов 4 (4-1...

4- Й ), Й третьих и И четвертых двухвходовых элементов И-HE 5 (5-1...5- И)

30 и 6 (6-1...6- г() соответственно, блок отображения информации 7 и низкочастотный генератор 8.

Предложенное устройство работает сле35 дующим образом.

В исходном состоянии на всех входах блоков обработки аналогового сигнала l присутствуют низкие уровни входных Cl..

C д аналоговых сигналов.

Поэтому в исходном состоянии все двухвходовые элементы И-НЕ 2, 3, 5 и 6 устройства за счет наличия на их входах нулевых уровней напряжения находятся в

45 единичном состоянии, а инверторы 4 за счет наличия на его входах высоких уровней напряжения находятся в нулевом состоянии

При поступлении на входы блоков обра-

50 ботки аналогового сигнала 1 высоких уровней аналоговых сигналов С1...С и в соответствии с заданной последовательностью их чередования первый двухвходовый элемент И-НЕ 2, на который приходит

\ 55 аналоговый сигнал, перебрасывается в нулевое состояние, а второй двухвходовый элемент И-НЕ 3 за счет наличия на первом его входе низкого уровня напряжения

4 первого двухвходового элемента И-HE 2 остается в единичном состоянии.

Первый инвертор 4 (4-1) и третий двухвходовый элемент И-НЕ 5 при этом также остаются в исходном состоянии, а четвертый двухвходовый элемент И-НЕ 6 эа счет наличия на его входах высокого уровня соответствующего входного аналогового сигнала и высокого выходного уровня третьего двухвходового элемента

И-НЕ перебрасывается в нулевое состояние, и в блоке отображения информации

7, выполненном, например, на светодиодах, загорается соответствующий приходящему аналоговому сигналу светодиод.

При этом каждым предыдущим входным аналоговым сигналом производится подготовка к работе первого двухвходового элемента. И-НЕ 2 последующего блока обработки аналогового сигнала 1. Таким образом, при соблюдении задайной после» довательности следования аналоговых сигналов Cl...Сп производится последовательное изменение состоянии первых двухвходовых элементов И-НЕ 2 блоков обработки аналогового сигнала 1 и в соо ветствии с заданной последовательностью свечение светодиодов блока отображения информации 7.

При выпадении иэ контролируемой последовательности чередования аналоговых сигналов одного или нескольких сигналов, первый двухвходовый элемент И-НЕ 2 блока обработки аналогового сигнала, на котором произошло нарушение последовательности, не изменяет своего единичного состояния, а второй двухвходовой элемент И-НЕ 3 блока обработки аналогового сигнала за счет появления на его втором входе высокого уровня входного аналогового сигнала изменяет свое состояние на нулевое.

При этом инвертор 4 изменяет свое состояние на единичное и своим высоким выходным уровнем напряжения по первому входу третьего двухвходового элемен-. та И-HE 5 разрешает прохождение ни кочастотных импульсов с низкочастотного генератора 8 на первый вход четвертого двухвходового элемента И-НЕ 6, на втором входе которого присутствует высокий уровень того входного аналогового сигнала, на котором произошло нарушение последовательности чередования сигналов.

С выхода четвертого двухвходового элемента И-НЕ 6 низкочастотные нмпу исы поступают на соответствующий свс

680183

5 тодиод, который будет периодически загораться с частотой, равной частоте низкочастотного генератора 8.

Таким образом, прн выпадении какихлибо аналоговых С 1...Сп СИГHsJIQB из за- 5 данной последовательности нх следования, обнаружение нарушения последовательности чередования сигналов определяется по ми гающим с частотой низкочастотного гене. ратора S и соответствующим месту нару- 1о шения чередования сигналов светодиодам блока отображения информации 7.

Возврат устройства в исходное состояние осуществляется подачей на все входы блоков обработки аналогового сигнала низких уровней аналоговых Cl ...Сп сигналов.

Предложенное устройство имеет высокую точность контроля, надежно в работе, 2о компактно и .просто по конструкции, обладает высокой информативностью и может быть выполнено на однотипных логических элементах с повышенным уровнем ин25 теграции.

Формула изобретения

Устройство для контроля последовательности чередования аналоговых сигназо лов, содержащее N блоков обработки аналогового сигнала, каждый из которых содержит первый и второй двухвходовые элементы И-НЕ, первые входы которых

6 объединены и являются входом блока обрабо ки аналогового сигнала, причем выход первого элемента И-НЕ подключен к второмувходу второго элемента И-НЕ, а каждый вход предыдущего блока обработки аналогового сигнала объединен с вторьпм входом первого элемента И-НЕ последующего блока обработки аналогового сигнала, выход каждого второго элемента И-НЕ является выходом блока обработки аналогового сигнала, и блок отображения информации, о т л и ч а ю m е е с я тем, что, с целью повышения точности контроля, введены низкочастотный генератор, М инверторов, t4 третьих и N четвертых двухвходовых элементов И-HE„при этом выход каждого блока обработки аналогового сигнала подключен через инвертор к первому входу одного из N третьих элементов И-НЕ, вторые входы которых . объединены с выходом низко« частотного гннератора, первый вход каждого из N четвертых элементов И-HE соединен с входом соответствующего блока обработки аналогового сигнала, а второй вход - с выходом одного из N третьих элементов И-НЕ, выход каждого из N четвертых элементов И-НЕ подключен к соответствующему входу блока отображения информации.

Источники информации, принятые во внимание прн экспертизе

1. Авторское свидетельство СССР

No 568173, кл. Н 04 В 17/00, 1975.

680l83

Составитель Г. Челей

Редактор Л. Гельфман Техред H. Асталош Корректор Т. Скворцова

Заказ 4813/55 Тираж 775 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 филиал ППП "Патент, r. Ужгород, ул. Проектная, 4