Генератор цифровых и аналоговых испытательных сигналов

Иллюстрации

Показать всеРеферат

Союз Соеетсеа

Социалмстическик

Респубпмк

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6l) Дополнительное к авт. саид-ву (22) Заявлено 21.09.77 (21) 2529365/18-09 с присоединением заявки № (23) Приоритет

Опубликовано 15.08.79. Бюллетень № 30

Дата опубликования описания 19.08.79

680199 (51) М. Кл.

Н 04 N 7/02

Гаеударетвенны9 нееипет

СССР на делам изобретений и еткрмтнй (53) УДК 621397 (088.81 (72) Авторы изобретения

М. И. Кривошеев, А. И. Шлайн и М. А. Рабинович (71) Заявитель (54) ГЕНЕРАТОР ЦИФРОВЫХ И АНАЛОГОВЫХ

ИСПЫТАТЕЛЬНЫХ СИ ГНАЛОВ

Изобретение относится к связи и может использоваться для контроля качества каналов связи, Известен генератор цифровых и аналоговых испытательных сигналов, например, для контроля каналов связи, содержаший блок управления, первый, второй, третий и четвертый выходы которого подключены соответственно к управляюшему входу коммутатора, к управляюшему входу первого блока оперативной памяти, подключенного информационными входом и выходом соответственно к первым выходу и входу коммутатора, к управляюшему входу второго блока оперативной памяти, подключенного информационными входом и выходом соответственно к вторым выходам и входу коммутатора, к управ- 15 ляюшему входу блока постоянной памяти, информационный выход которого соединен с третьим входом коммутатора, третий и четвертый информационные выходы этого коммутатора соединены соответственно с первым и вторым входами вычислительного блока, преобразователь параллельного кода в последовательный, выход которого является первым выходом генератора, последовательно включенные цифроаналоговый преобразователь и фильтр низкой частоты, выход которого является вторым выходом генератора (1).

Однако известный генератор обладает значительной сложностью и не позволяет производить контроль работоспособности входящих в него блоков.

Целью изобретения является упрошение устройства за счет сокрашения объема блоков постоянной памяти и самоконтроля его работы.

Зля этого в генератор цифровых и аналоговых испытательных сигналов, например, для контроля каналов связи, содержаший блок управления, первый, второй, третий и четвертый выходы которого подключены соответственно к управляюшему входу коммутатора, к управляющему входу первого блока оперативной памяти, подключенного информационными входом и выходом соответственно к первым выходу и входу коммутатора, к управляюшему входу второго блока оперативной памяти, подключенного информационными входом и выходом соответственно к вторым выходу и входу коммутато680199

3 ра, к управляющему входу блока постоянной памяти, информационный выход которого соединен с третьим входом коммутатора, третий .и четвертый информационные выходы этого коммутатора соединены соответственно с первым и вторым входами вычислительного блока, преобразователь параллельного кода в последовательный, его выход является первым выходом генератора, последовательно включенные цифроаналоговый преобразователь и фильтр низкой часто- 1О ты, выход последнего является вторым выходом генератора, введены блок согласования, два блока программируемой памяти, блок контроля испытательных сигналов, индикатор и элемент

И, причем управляющий вход блока согласова- 15 ния, на вход которого подан сигнал внешнего источника информации, соединен с пятым вы/ ходом блока управления, шестой, седьмой и восьмой выходы этого блока подключены соот-. ветственно к.управляюшсму-входу первого бло- э0 ка программируемой, памяти, к управляющему входу второго блока программируемой памяти, к первому входу блока контроля испытательных сигналов, выход которого соединен с входом индикатора и с первым входом элемента И, вто- 25 рой вход которого подключен к выходу вычислительного блока и к второму входу блока контроля испытательных сигналов, выход элемента И соединен с входом цифроаналогового преобразователя и с входом преобразователя щ параллельного кода в последовательный, а первый и второй выходы блока согласования подключены соответственно к информационному входу первого блока программируемой памяти, к информационному входу второго блока программируемой памяти, выход каждого из которых соединен соответственно с пятым и шестым информационными входами коммутатора..

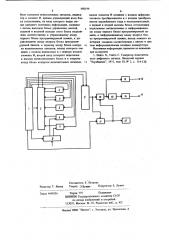

На чертеже приведена структурная электрическая схема предложенного генератора. 40

Генератор цифровых и аналоговых испытательных сигналов содержит блок 1 управления, коммутатор 2, первый блок 3 оперативной памяти, второй блок 4 оперативной памяти, блок 5 постоянной памяти, два блока 6 и 7 программируе 45 мой памяти, блок 8 согласования, вычислительный блок 9, элемент И 10, блок 11 контроля испытательных сигналов, цифроаналоговый преобразователь 12, преобразователь 13 параллельного кода в последовательный, фильтр 14 низкой частоты, индикатор 15, соответственно первый и второй выходы 16 и 17, Генератор работает следующим образом.

Блок 1 управления задает цикл работы всего генератора, а также при необходимости включает блок 8, который служит для обновления информации, записанной в блоках 6 и 7, а так как последние имеют низкое быстродействие, то. информация через коммутатор 2 поступает на пер4 вый и второй блоки 3 и 4. В блок 5 информацйя записывается при изготовлении прибора.

В соответствии с циклом работы генератора информация считывается с требуемой скоростью с первого и второго блоков 3 и 4 и блока 5 и через коммутатор 2 подается на вычислитель- ный блок 9, затем информация через элемент

И 10 поступает на цифроаналоговый преобразователь 12, преобразующий цифровой код в аналоговчю величину, и на фильтр 14, с выхода ко1орого испытательный сигнал поступает в аналоговый канал — второй выход 17 генератора.

Преобразователь 13 преобразует параллельный код в последовательный, с его выхода испытательный сигнал поступает в цифровой канал— первый выход 16. генератора. Блок 11 контро: лирует цифровые испытательные сигналы, индикатор 15 ицпицирует режим неправильной работы генератора и предотвращает выдачу неправильного сигнала. Блок 11 контроля может быть выполнен по любой известной схеме контроля цифровых сигналов.

Предложенный генератор отличается простотой и позволяет исключить возможность выдачи испытательных сигналов, не соответствующих заданным.

Формула изобретения

Генератор цифровых и аналоговых испытательных сигналов, например, для контроля каналов связи, содержащий блок управления, первый, второй, третий и четвертый выходы которого подключены соответственно к управляющему входу коммутатора, к управляющему входу первого блока оперативной памяти, подключенного информационными входами и выходом соответственно к первым вв ходу и входу коммутатора, к управляющему входу второго блока оперативной памяти, подключенного информационными входом и выходом соответственно к вторым выходу и входу коммутатора, к управляющему входу блока постоянной памяти, информационный выход которого соединен с третьим входом коммутатора, третий и четвертый информационные выходы которого .соединены соответственно с первым и вторым входами вычислительного. блока, преобразователь параллельного кода в последовательный, его выход является первым выходом генератора, последовательно включенные цифроаналоговый преобразователь и фильтр низкой частоты, выход последнего является вторым выходом генератора, отличающийся тем, что, с целью упрощения устройства за счет со-. кращения объема блоков постоянной памяти и ! самоконтроля его работы, введены блок согласования, два блока программируемой памяти, 6З0199

Составитель Е. Петрова

Редактор Т. Янова Техред; g.мужик. Корректор Е. Лукач

Заказ 4649/56 Тираж 775 Подписное

11НИИПИ Государственного комитета СССР по делам изобретений н открьггий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

5 блок контроля испытательных сигналов, индикатор н элемент И, причем управляющий вход блока согласования, на вход которого подан сигнал внешнего источника информации, соединен с пятым выходом блока управления,.шестой, седьмой и восьмой выходы этого блока подключены соответственно к управляющему входу первого блока программируемой памяти, к управляющему входу второго блока программируемой памяти, к первому входу блока контро- io ля испытательных сигналов, выход которого соединен с входом индикатора и с первым входом элемента И, второй вход. которого подключен к выходу вычислительного блока и к второму входу блока контроля испытательных сигналов, 15

6 выход элемента И соединен с входом цнфроана. логового преобразователя и с входом преобразователя паралйльного кода в последовательный, а первый и второй выходы блока согласования подключены соответственно к информационному входу первого блока программируемой памяти, к информационному входу второго блока программируемой памяти, выход кажного иэ которых соединен соответственно с пятым и шее тым информационными входами коммутатора.

Источники информации, принятые во внимание. при экспертизе

1. Найто Х., Сайто С. Генератор испытательного цифрового сигнала. Японский журнал

"Тэрэбидзен", 1971, том 30, Н 2, с. 114-120.