Способ уменьшения помех в измерительных устройствах уравновешивания и устройство для его осуществления

Иллюстрации

Показать всеРеферат

п1 682830

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свпд-ву (22) Заявлено 22.06.77 (21) 2499368/18-21 с присоединением заявки № (23) Приоритет (43) Опубликовано 30.08.79. Бюллетень ¹ 32 (4 ) Дата опубликования описания 30.08.79 (51) M. Кл 2

G 01R 17/10

Государственный комитет (53) УДК 681.325. (088.8) по делам изобретений и открытий (72) Авторы изобретения

В. М. Бреннерман н В. М. Власенко (71) Заявитель (54) СПОСОБ УМЕНЬШЕНИЯ ПОМЕХ В ИЗМЕРИТЕЛЬНЫХ

УСТРОЙСТВАХ УРАВНОВЕШИВАНИЯ И УСТРОЙСТВО

ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ

Изобретение относится к измерительной технике.

Известен способ уменьшения помех в измерительных устройствах уравновешивания, основанный на предварительной амплитудно-импульсной модуляции измеряемых сигналов и последующем синхронном детектировании смеси сигнала с помехой, и устройство для его осуществления (1).

Однако устройство имеет низкую помехоустойчивость.

Известен способ уменьшения помех в измерительны. устройствах уравновешивания, основанный на амплитудно-импульсной модуляции измеряемого сигнала и синхронном детектировании разности промодулированного измеряемого сигнала и компенсирующего сигнала, и устройство для реализации этого способа, содержащее измерительный блок, выход которого соединен с первым входом блока вычитания, выход которого через последовательно соединенные синхронный детектор нуль-орган, блок автоматики и блок уравновешивания соединен со вторым входом блока вычитания (2).

Недостатком устройства является низкое подавление помех.

Целью изобретения является повышение помехоустойчивости.

Указанная цель достигается тем, что в способе, основанном на амплитудно-импульсной модуляции измеряемого сигнала и синхронном детектировании разности промодулированного измеряемого сигнала и компенсирующего сигнала, в каждом пз т последовательных тактов п разрядного уравновешивания, предшествующих каждому k-му такту уравновешивания, запоми10 нают однофазные значения промодулированного измеряемого сигнала, а в каждом

k-ом такте уравновешивания запомненные значения сигнала и промодулированный измеряемый сигнал той же фазы суммируl0T

1З с соответствующими весовымп коэффициентами с результатом синхронного детектирования, причем весовые коэффициенты устанавливают методами интерполяции по m запомненным значениям сигнала п значе20 нию промодулированного измеряемого сигнала той же фазы в /г-ом такте из условия нахождения изменения помехи за время между моментами получения в k-ом такте противофазных значений упомянутой раз25 ности сигналов при синхронном детектировании, а в устройстве для осуществления способа, содержащем измерительный блок, блок вычитания, синхронный детектор, нуль-орган, блок автоматики и блок урав3О новешивания, введены т+1 узлов запоми682830

3 нания, сумматор т+1 групп ключей, по т+1 ключу в каждой группе ключей, и масштабный сумматор, причем выход;змсрительного блока соединен со входами узлов запоминания, входы каждой l-й группы ключей соединены соответственно с

l, /+1,..., m+1,1,...,l — 1 выходами узлов зaпоминания, выходы групп ключей соединены соответственно с т+1 входами масштабного сумматора, выход которого соеди- !О нен с первым входом сумматора, второй вход которого соединен с выходом синхронного детектора, а выход — с входом пульоргана.

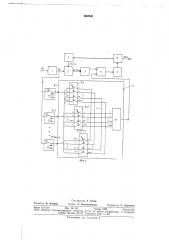

Временные диаграммы, поясняющие предлагаемый способ, приведены на фиг. 1.

Структурная электрическая схема устройства для осуществления способа приведена на фиг. 2.

Устройство содержит последовательно 20 соединенные измерительный блок 1, блок 2 вычитания, синхронный детектор 3, сумматор 4, нуль-орган 5, блок 6 автоматики, блок 7 уравновешивания, выход которого связан с блоком 2 вычитания, причем вхо- 25 дом устройства является вход измерительного блока, а выходом — выход блока автоматики, узлы запоминания 8= 1 — 8=

= (т+1), входы которых соединены с «ыходом измерительного блока 1, группы !О

9=1 — 9= (т+1) ключей по т+1 ключей в каждой группе, масштабный сумматор 10, масштабный сумматор и m+I группы ключей образуют блок циклического интерполирования 11, узлы запоминания состоят 35 из ключей 12 и конденсаторов 13.

Преобразование измеряемого сигнала в устройстве основано на поразрядном уравновешивании и происходит за и тактов. Измерительный блок 1 и блок 7 уразновсши- I; вания питаются прямоугольными двухиолярными импу льс2 ми. В к2ждом TIKTc ila сигнала У„измерите. !ьны!! блок 1 (фиг.

1a) вычитает очередной o lnellciip, !Огц:!:! импульс блока уравновешивания 7. Из бло- !5 ка вычитания 2 разпостные импульсы амплитудой U,.— U„»,„(ôèã. I б) ггодаются иа синхронный детектор 3, в котором попарно вычитаются значения сигнала блока 2 вычитания, соответствующие концам импуль- 50 сов питания разной полярности (эти значения условно показаны точками на фиг. Iб).

При этом абсолютные значения сигнала (U — U; ) складываются, а значения помехи воздействующей на измерительный 55 блок 1, вычитаются. Через сумматор 4сигнал синхронного детектора поступает на нуль-орган 5, определяющий сбросить или оставить очередную порцию компенсирующего сигнала. 60

Изменение помехи Ag за время между концами разнополярных импульсов питания (в !г-ом такте за время между моментами (II, и 4) компенсир,ется с помощью узлов запоминания, блока 11 и сумматора 4. 55

Ключи 12 B узлах запомгшанпя работают так (см. фиг. 1), что в течегние первых т+1 тактов в соответствующих узл;..; 8 запоминаются значения Ui, U ., U„„+i сигнала в измерительном блоке 1. В (т+1)-ом

; ак гг замыкакггся ключи первой группы бло-! 2 11 (фиг. 1") п >!Ia÷oå!èß U;,Uv,...,Um+I сх м мируются в масштабном сумматоре 10 соответственно с коэффициентами Х!,Х., Х „,

На выходе масштабного сумматора 10 появляется сигнал A(I, который в сумматоре

4 вычитается из сигнала синхронного детектора 3. В (т+2) -ом такте очередное значение сигнала измерительного блока 1 (У„,+ ) запоминается в узле 8 — 1. запоминания, при этом значение U:, запо ггseинcе ранее в узле 8 — 2 запомгшания, о,;азывается первым в очередной серии из ги —, 1 значений сигнала, значение U, — вторым и т. д. В (m+2)-ом такте ключи группы 9 — 1 блока 11 размыкаются и замыкаются ключи группы 9 — 2, с помощью которых выход узла 8 — 2 запоминания подключается к первому входу масштабного сумматора 10, выход узла 8 — 3 запоминания — ко второму входу и т. д., а выход узла 8 — 1 запоминания к (т+1)-му входу масштабного сумма гора 10. При этом значения U, U>.

Um 2 суммируются соответственно с коэффициентами л!, i.q, ..., л",-,,, и иа выходе масштабного с1мматора 10 появится новое значение М!, соответствующее второй серии

m+I значений cIIIIIaла измерительного б гонг! 1.

Последующая работа устройства происходит аналогично.

Форму".а изобретения

1. Способ уменьшения по c. в измерительных устройствах уравиовсшг!вания, осио" IIIIhi!! н 2 2 м n;Ill Дно-импУ льсной МОДУ

:,яции измеряемого сигнала и синхронном дстсктирован;ш разности г;ромодулиро32!гно о измеряемого сигна.га и компенсирующего сигнала, о тл ll ч а !о щи и с я тем, что, с целью повьгшения г!Омехоустойчивости, в каждом из и последовательных тактов и разрядного уравновешивания, предшествующих каждому k-му такту уравновешивания, запоминают однофазные значения промодулированного измеряемого сигнала, а в каждом k-ом такте уравновсшг!ваггия запомненные значения сигнала и иромодулированный измеряемый сигнал той же фазы суммируют с соответствующими весовыми коэффициентами, с результатом синхронного детектирования, причем весовые коэффициенты устанавливают методами интерполяции по т запомненным значениям сигнала и значению промодулированного измеряемого сигнала той же фазы в k-ом такте из условия нахождения изменения Iloмехи за время между моментами получения в /г-ом .акте противофазных значений упо682830

) К1 кя

Р (m-! (l(1 г:. мянутой разности сигналов при синхронном детектировании.

2. Устройство для осуществления способа по п. 1, содержащее измерительный блок, выход которого соединен с первым входом блока вычитания, выход которого соединен с входом синхронного детектора, нуль-орган, выход которого через последовательно соединенные блок автоматики и блок уравновешивания соединен со вторым входом блока вычитания, отл и ч а ю щеес я тем, что в устройство введены m+1 узлов запоминания, сумматор, т+1 групп ключей по

m+1 ключу в каждой группе ключей и масштабный сумматор, причем вход измерительного блока соединен со входами узлов запоминания, входы каждой 1-й группы ключей соединены соответственно с

1+1,... т+1, 1,... 1 — 1 выходами узлов запоминания, выходы групп ключей соединены соответственно с т+1 входами масштабного сумматора, выход которого соединен с превым входом сумматора, второй вход которого соединен с выходом синхронного детектора, а выход — с входом нульоргана.

Источники информации, принятые во внимание при экспертизе

1. О. Хорна. Тензометрическпе мосты, М., «Энергия», 19б2., с. 205 — 234.

2. М. И. Корниенко. Цифровой измерительный автокомпенсатор, выполненный на элементах интегральной микроэлектроники.

Сборник работ по вычислительным и измерительным системам для исследования аэродинамики, динамики и прочности летательных аппаратов. Труды ЦАГИ, выпуск

1б89, М., 197б.

682830

Составитель А. Титов

Техред А. Камышникова

Редактор Н. Коляда

Корректор р. Беркович

Заказ 2111/14 Изд. № 522 Тираж 1090 Подписное

НПО «Поиск» Государственного комитета СССР по делам изобретений и открытий

113035, Москва Я-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2