Цифровой линейный интерполятор

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ()682923

Союз Советских

Социалистических

Республик (61) Дополнительное к аат. свил-ву— (22)) Заявлено 04.04,77 (21) 2472524!18-24 с присоединением заяаки №вЂ” (23) Приоритет— (43) Опубликовано 30.08.79. Бюллетень ¹ 32 (45) Дата опубликования описания 31.08.79

P1) М.Кл 6 06 К 15/20

Государственный комитет

СССР (53) УДК 621.327

{088.8) ло делам изобретений и открытий (72) Авторы изобретения

В. Ф. Каплун, Т, Г. Семенюк и В. И. Хомяков

Научно-исследовательский и конструкторский институт периферийного оборудования (71) Заявитель (54) ЦИФРОВОЙ ЛИНЕЙНЫЙ ИНТЕРПОЛЯТОР

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в устройствах отображения и преобразования данных, преимущественно в устройствах отображения графической информации на электронно-лучевых трубках (ЭЛТ).

Известны аналоговые устройства (генераторы, интерполяторы) для формирования прямых линий на экране ЭЛТ,(1). Недостаток этих устройств заключается в том, что они имеют значительную погрешность выхода в заданную точку, которая увеличивается по мере увеличения длины линии.

Известны также цифровые линейные ин- !5 терполяторы на делителях частоты (2). Такие устройства обладают методической погрешностью выхода в заданную точку и значительно уступают аналоговым устройствам в быстродействии.

Наиболее близким по технической сущности к предлагаемому техническому решению является цифровой линейный интерполятор (3), содержащий генератор тактовых импульсов, интеграторы, каждый из которых содержит приемный регистр, входы которого подключены ко входным информационным шинам интерполятора, и .накапливающий сумматор, вход синхронизации которого соединен с одним из выходов генератора тактовых импульсов. Недостатком известного интерполятора является ограниченная скорость интерполирования линий.

Сущность этого ограничения заключается в следующем.

За время одного такта генератора тактовых импульсов на выходе каждого из двуx интеграторов вырабатывается не более одного элементарного приращения. Следогательно, предельно достижимая скорость пп— терполирования однозначно определяется максимально допустимой частотой fn следования тактовых импульсов, которая, в свою очередь, определяется разрядностью накапливающего сумматора и временем переключения применяемых логических элементов. Минимальное время, необходимое для интерполирования линии с п-разрядной (двоичной) проекцией на координатную ось х или у

Для линии с 10-разрядной проекцией (характерной для графических устройств отображения на ЭЛТ) и при f;;, =2 Мгц (для 10-разрядного накапливающего сум45

6О

65 матора, выполненного на базе интегральных микросхем серии 155) Т„„,,„;, =500 и с, что в 5 — 10 раз превышает время построения линии аналоговыми методами.

Именно недостаточно высокое быстродействие ограничивало до настоящего времени применение этих интерполяторов в графических устройствах отображения на ЭЛТ, Целью изобретения является повышение быстродействия интерполятора. Указанная цель достигается в интерполяторе тем, что он содер>кит блок элементов ИЛИ, Входы которого подключены к выходам приемных регистров интеграторов, блок фиксации заиитой, Входы I

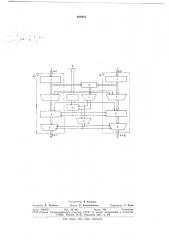

На чертеже представлена блок-схема предлагаемого интерполятора.

Он состоит из генератора 1 тактовых импульсов, интегратора 2 приращений по координате х и полностью идентичного ему по структуре и связям интегратора 3 приращений по координате у. Каждый интегратор содержит приемный регистр 4, входы которого подключены ко входным информационным шинам 5, и накапливающий сумматор б, вход синхронизации которого подключен к одному из выходов генератора 1 тактовых импульсов, блок 7 параллельного сдвига информации, информационные входы которого;подключены к выходам приемного регистра 4, управляющие входы — ко входным управляющим шинам 8, а выходы — к информационным входам накапливающего сумматора 6, и блок 9 формирования приращений координат, информационные входы которого подключены к входам сумматора б, а выходы — к выходным информационным шинам 10. В состав интерполятора включены также блок 11 фиксации запятой, блок 12 элементов ИЛИ, первые входы которого подключены пораз5

Зз

40 рядно к выходам приемного регистра 4 интегратора 2, вторые входы — к соответствующим выходам приемного регистра 4 интегратора 8, а выходы соединены со Входами блока 11 фиксации запятой, блок 13 установки нуля, выходы которого подключены поразрядно ко входам установки «О» старших (слева от запятой) разрядов сумматора б, а вход синхронизации — к другому выходу генератора 1, и дешифратор 14, входы которого соединены со входами блока 18 установки нуля и с выходами блока

11 фиксации запятой.

Интерполятор работает следующим образом.

В исходном состоянии в регистрах 4

«нулевые» коды, запятая фиксирована перед младшим разрядом (нет ни одного разряда, равного «1»), все разряды накопительных сумматоров б установлены в «О», на выходные шины 10 информация не поступает. Генератор 1 тактовых импульсов вырабатывает две серии сдвинутых во времени тактовых импульсов, ка>кдый из которых подтверждает состояние интеграторов

2 и 3.

Коды координатных приращений Лх и

Лу со входных информационных шин 5 заносятся в приемные регистры 4 интеграторов 2 и 8 соответственно. С выходов регистров через логический блок 12 дизыонкция этих кодов поступает на входы блока

11 фиксации запятой, который Выделяет самый старший, равный логический «1» разряд кода дизъюнкции. Сигнал этого разряда с выхода блока 11 через блок установки нуля 13 .подготавливает условия для сброса разрядов переполнения сумматоров б, а через дешифратор 14 и блоки 9 формирования приращений координат осуществляет логическое подключение k разрядов переполнения каждого сумматора б к выходным шинам 10. Кроме того, I<03, с выходом,приемного регистра 4 каждого интегратора, сдвинутый с помощью блока 7 на

i разрядов (0 (i --.. k) в сторону старшего разрчда, поступает на входы накапливающего сумматора б.

В первом полутакте по тактовому импульсу от генератора 1 выполняется суммирование суммы и выдача содержимого k разрядов переполнения каждого сумматора в виде малых приращений координат

Л(Лх) и Л(Лу) на выходные шины 10.

Во втором полутакте через блок 18 установки нуля BbIIIIoëíÿåòñÿ «обнуление» разрядов переполнения сумматоров.

Затем в следующем полутакте опять

Вьшолняется суммирование содержимого сумматоров б с кодами на их входах, запоминание новой суммы, выдача очередных выходных приращений Л(Лх) и Л(Лу) и т. д. Последовательность операций циклически позторяется до получения сигнала конца интерполяции, о чем свидетельствует

682923 занесение «нулевого» кода на приемные регистры 4, после чего интерполятор переходит в исходног состояние.

Максимальная разрядность формируемых в каждом такте малых приращений равна /+ 1 и, следовательно, однозначно определяется разрядностью сдвига входных приращений в бчоке 7 параллельного сдвига информации, которая, в свою очередь, задается кодом на управляющих шинах 8 что позволяет программно изменять скорость интерполяции за счет изменения разрядности выходного приращения.

Примгнение предлагаемого интерполятора в графических устройствах отображения на ЭЛТ предполагает формирование промежуточных точек отрезков, задаваемых малыми приращениями, с помощыс аналоговых формирователей. При этом погрешность формирования линии не превышает погрешности обработки одного выходного приращения и не зависит от полной длины линии, задаваемой входными приращениями координат Лх и Лу.

Следовательно предлагаемый интерполятор позволяет резко увеличить скорость интерполяции и дает возможность выбора оптимального соотношения между скоростью интерполяции и допустимой точностью обработки линии при обеспечении выхода в заданную точку без,погрешности.

Формула изобретения

Цифровой линейный интерполятор, содержащий генератор тактовых импульсов, интеграторы, каждый из которых содержит приемный регистр, входы которого подключены ко входным информационным шинам пнтерполятора, и накапливающий сумматор, вход синхронизации которого соединен с одним из выходов генератора тактовых импульсоз, отличающийся тем, что, с целью повышения быстродействия интерполятора, он содержит блок элементов ИЛИ, входы которого подключены к выходам приемных регистров интеграторов, блок фиксации запятой, входы которого соедине10 ны с выходами блока элементов ИЛИ, блок установки нуля н дешифратор, входы которых подключены к выходам блока фиксации запятой, вход синхронизации блока установки нуля соединен с другим выходом

15 генератора тактовых импульсов, а выходы— с установочными входами сумматоров, причем в каждый из интеграторов введены блок формирования приращений координат и блок параллельного сдвига информации, 20 информационные входы которого подключены к выходам приемного регистра, управляющие входы — ко входным управляющим шинам интерполятора, а выходы— к информационным входам сумматора, вы25 ходы которого соединены через блок формирования приращений координат с выходами интерполятора, а управляющие входы блока формирования приращений координат подключены к выходам дешифратора.

Источники информации, принятые во

Bi-имание при экспертизе:

1. Авторское свидетельство СССР

¹ 424177, кл. G 06 G 7/30, 1973.

2. Авторское свидетельство СССР № 395839, кл. G 06 К 15/20, 1972.

3. Карибский В. В. и Чернышев А. В, Цифровые интерполяторы для систем программного управления. М., «Машиностроение», 1962, с. 10 — 13.

682923

Составитель В. Киселев

Техред А. Камышникова

Редактор В. Девятов

Корректор С. Файн

Тип. Харьк. фил. вред. «Патент»

:заказ 7 66/965 Изд. ¹ 482 Тираж 780 Подписное

Vi1O «Поиск» Государственного комитета СССР по делам изобретений и orêðûòèé

113035, Москва, 7К-35, Раушская наб., д. 4/5