Регистр сдвига

Иллюстрации

Показать всеРеферат

о т1 4 т)1

Ф т4в IA

Ii i! 68295О

Со1оз Советских

Социалистических

Республик т.

xsosve TeHI1

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 04.01.76 (21) 2311736/18-24 с присоединением заявки ¹ (51) . 111. 1(л.-

G 11С 19 28

ГосУдаРственный комитет (23) г1риоритет (43) Опубликовано 30.08.79. Бюллетень ¹ 32 (53) УДК 681.327.66 (088.8) по делам изобретеиий и открытий (45) Дата опу бликования описа1шя 30.08.79 (72) Авторы изобретения

В. Е. Мельник и Г. С. Мельник (71) Заявитель Таганрогский радиотехнический институт имени В. Д. 1(алмыкова (54) РЕГИСТР СДВИГА

Изобретение относится к области вычислительной техники и может быть использовано для построения быстродействующих регистров с двусторонним сдвигом (реверсивных регистров), на основе которых могут создаваться сверхоперативные и ассоциативные запоминающие устройства, коммутирующие регистровые структуры.

Известны реверсивные регистры сдвига на триггерах, которые используются для построения сверхоперативных и ассоциативных запоминающих устройств и коммутирующих регистровых структур (1).

Наиболее близким техническим решением является быстродействующий регистр с односторонним сдвигом на туннельных диодах, который может быть использован для построения запоминающих устройств циклического типа и последовательных устройств (2).

Однако известные регистры сдвига на туннельных диодах, имеюгцие большое быстродействие, не обеспечивают двустороннего сдвига и, следовательно, не являются реверсивными регистрами сдвига. Известные реверсивные регистры сдвига на триггерах имеют меньшее быстродействие и сложны в конструктивном отношении и поэтому использование их для построения вычислительных устройств приводит к значительным аппаратурным затратам последних и не обеспечивает необходимого быстродействия.

Один разряд известного регистра состоит из трех последовательно соединенных посредством резисторов бистабильнь1х триггеров на туннсльных диодах. Тактированис таКОГО РЕГИСтРа ОС) ЩССТВЛЯСТСтl С ПОМ01>Ц!>IO трех серий синусоидального сигнала или

10 трех серий прямоугольных импульсов со скважностью равной двум, сдвинуты.; по фазе на одну треть периода и поступающих соответственно на первый, второй и третий триггеры каждого разряда. Использование

15 минимум трех серий такгиру10щих С11гналов (импульсны., илп синусопдальны i) обусловлено необходимостью обес1ц 1.синя однонаправленного распространения информации, поскольку триггеры на туннсль20 ных диодах являются двухполюсннками и не имеют развязки входа от выхода.

Известныс формирователи, прпменясмыс для формирования тактовых импульсов ис обеспечивают необходимого быстродсйст25 вия и работают в непрерызном режиме. что

НЕ ПОЗВОЛЯСТ ОС;.ЩССТВИТЬ ДВ1.СТОРОННН>1 сдвиг информации и статичсскос хранение ее.

Цель изобретения — расширение облаЗО сти применения регистра за счет обсспсчс682

3 ния режима двустороннего сдвига и статического хранения.

Поставленная цель достигается тем, что регистр сдвига, содержащий последовательно соединенные триггеры, каждый из которых выполнен на двух последовательно включенных туннельных диодах, один из которых подключены к шине нулевого потенциала, а другой к одной из управляющих шин, связанных с соответствующими выло- 10 дами формирователя тактовых импульсов, шины синхроимпульсов и шины сдвига влево и вправо, содержит дополнительный триггер, выполненный на двух последовательно включенных туннельных диодах, 15 один из которых соединен с шиной нулевого потенциала, а другой — с другой управляющей шиной, а влоды формирователя тактовых импульсов соединены соответственно с шинами синхроимпульсов и сдвига 20 влево и вправо, а также тем, что формирователь тактовых импульсов содержит два

RS-триггера, входы которых соединены с выходами элементов И вЂ” ИЛИ, первые и вторые входы которых соединены с соответ- 25 ствующими входами формирователя тактовых импульсов, выходы RS-триггеров подключены к соответствующим выходам формирователя тактовых импульсов и третьим выходам элементов И вЂ” ИЛИ. 30

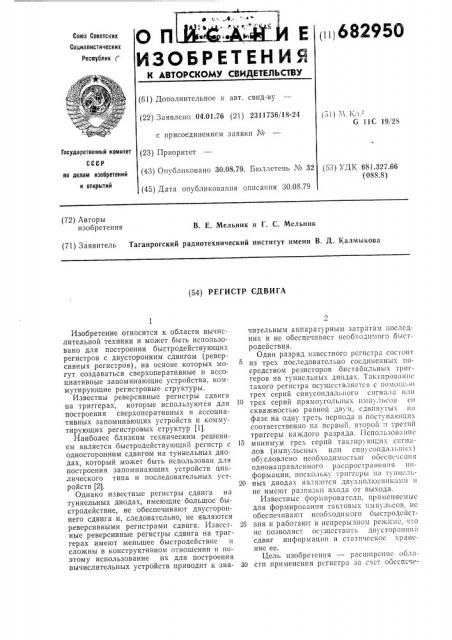

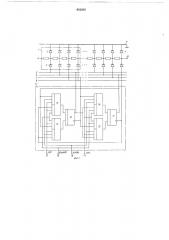

На фиг, 1 представлена схема предложенного регистра; на фиг. 2 — временная диаграмма работы формирователя.

Регистр содержит последовательно соединенные триггеры 1, выполненные на двух 35 последовательно включенных туннельных диодах 2 и 3, причем диоды 2 подключены к шине 4 нулевого потенциала, диоды 3— к соответствующим управляющим шинам

5 — 8, которые связаны с соответствующими 40 выходами формирователя 9 тактовых импульсов, который состоит из двух RS-триггеров 10 и 11, входы которых соединены с выходами элементов И вЂ” ИЛИ 12, 13 и 14, 15. Шина синхронизации 1б и 17, и шина 45 сдвига влево 18 и вправо 19, соединены со входами формирователя 9.

Формирователь 9 обеспечивает формирование тактовых импульсов на шинах 5 — 8 50 в требуемой последовательности при подаче одного из управляющих сигналов «Вправо» или «Влево». Формирование серий тактовых импульсов и сдвиг информации в регистре осуществляется при подаче одного 55 из управляющих сигналов «Вправо» или

«Влево». Одновременная подача указанных сигналов недопустима. При отсутствии обоих сигналов регистр обеспечивает статическое хранение ранее записанной информа- 60 ции, Синхронизация работы формирователя осуществляется двумя непрерывными сериями импульсов по шинам 16 и 17, сдвинутыми друг относительно друга на полпериода (фиг. 2, в, г). 65

950 г 4

При подаче сигнала «Вправо» (фиг. 2, а, временной промежуток T ) на шину 19 единичный выход триггера 10 через элемент

14 подключается ко входу триггера 11, нулевой выход триггера 10 через элемент 15— ко входу триггера 11, единичный выход триггера 11 через элемент 13 — ко входу У триггера 10, а нулевой выход триггера 11 через элемент 12 — ко входу S триггера 10.

Из непрерывных серий СИ1 и СИ2 по шинам 16 и 17 выделяются «пакеты» импульсов ПСИ1 и ПСИ2 (фиг. 2, д, е), которые в течение временного интервала Т, поступают на выходы триггеров 10 и 11. Поскольку формирователь 9 на триггерах 10 и 11 представляет собой триггер со счетным входом, то он осуществляет пересчет импульсов ПСИ1 и ПСИ2 по модулю два.

Выходные сигналы триггеров 10 и 11, используемые для регистра как тактовые серии ТИ1 — ТИ4 (фиг. 2, ж, к), обеспечивают сдвиг информации в регистре вправо.

При этом длительность Т> сигнала «Вправо» (фиг. 2, а) определяет количество тактов сдвига, то есть число разрядов, на которое сдвигается информация в регистре вправо.

При подаче сигнала «Влево» (фиг. 2, б, интервал Т ) на шину 18 единичный выход триггера 10 через элемент )5 подключается ко входу R триггера 11, нулевой выход триггера 10 через элемент 14 ко входу $ триггера 11, единичный выход триггера 11 через элемент 12 ко входу S триггера 10, а нулевой выход триггера 11 через элемент

13 — ко входу R триггера 10. С помощью сигнала «Влево» из серий СИ1 и СИ2 на элементах 12 — 15 выделяются пакеты импульсов ПСИ1 и ПСИ2, которые в течение временного интервала 7> поступают на входы триггеров 10 и 11. Выходные сигналы триггеров 10 и 11 используются как тактовые серии ТИ4 — ТИ1, обеспечивают сдвиг информации в регистре влево. Длительность Т определяет количество тактов сдвига.

Рассмотрим работу регистра при сдвиге информации вправо.

Для записи «1» на вход регистра должен поступить импульс высокого уровня, опережающий импульс серии ТИ1 на /4 такта.

При поступлении серии ТИ1 первый триггер первого разряда переключится в единичное состояние. Если же на входе присутствует «О», то первый триггер первого разряда окажется в нулевом состоянии.

Соответственно при поступлении импульса

ТИ2 второй триггер первого разряда устанавливается в то же состояние, что и первый триггер. По окончании серии ТИ1 первый триггер устанавливается в «О», а второй триггер хранит свое состояние.

Аналогично, при появлении импульса серии ТИЗ информация переписывается со второго триггера на третий, а при появле682950

Зо

40 нии импульса серии ТИ4 — с третьего на четвертый триггер первого разряда.

При подаче сигнала сдвига «Влево» (фиг. 2, б) процессы записи информации влево протекают подобно предыдущему, по только в обратном направлении, т. е. с выхода — входа 20 информации записывается на четвертый триггер последнего разряда и последовательно сдвигается на третий, второй, первый триггеры последнего разряда, на триггеры предпоследнего разряда и т. д.

Предложенный регистр имеет больпьос быстподействие (частота сдвига до

100 МГц), мал1ю потребляемую мощчос1ь (не более 1 — 1,5 МВт на разряд) и характеризуется простотой и регулярностью схемы, что позволяет легко реализовать указанный регистр в виде гибридной интегральной схемы. Формирователь реверсивного регистра достаточно прост в схемном отношении, не содержит нестандартных элементов и для его построения могут быть использованы серийные интегральные схемы

ЭСЛ-типа. Один такой формирователь может обеспечить управление 20 — 30 разпядами регистра, а сам регистр сдвига обеспечивает сдвиг информации в требуемом направлении, а также режим статического хранения записанной информации и может быть использован для построения различных устройств последовательностных машин, сверхоперативных запоминающих устройств магазинного и циклического типа, ассоциативных запоминающих устройств и коммутирующих регистровых матриц однородных вычислительных структур.

Формула изобретения

1. Регистр сдвига, содержащий последовательно соединенные триггеры, каждый из которых выполнсн на двух послсдоватсльНо вклю IBHHbIx туннсльных диодах, один пз

I

2. Регистр по п. 1, отл пч а 1ощп и с я тем, что формировател1. TBI.ToBhIx пмп"льсов содержит два RS-триггера, входь1 котопых соединены с выходамп элементов И—

ИЛИ, первые и вторые входы которых соединены с соответств .ю1цими входамп формирователя тактовых импульсов. выходы

RS-триггеров подкл1о 1сны к соответствм1ощим выходам формирователя тактовых имп львов и третьим выходам элементов

И вЂ” ИЛИ.

Источники информации, прпнять1е во внимание при экспертизе

1. Майоров С. А. и др. Структурьl цифровых вычислительных машин, Л., «Ìàïøностроение», 1970, с. 69.

2. Котт В. М. и др. Туннельные дподь1 B вь1числител1.ной технике, М., «Советское радио», 1967.

682950

Т7

/г г сигТиг и тию

Г 1 1 1 Г

Редактор H. Коляда

Корректор Е Хмелева

Заказ 2202/4 Изд. № 493 Тираж 681 Подписное

НПО «Поиск» Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр, Сапунова, 2 и

79—

//

78 д

err 7 д

ПЕИ7 е псиг ж

ТИ7Составитель Г. Мельник

Техред А. Камышникова