Преобразователь временных интервалов в код

Иллюстрации

Показать всеРеферат

:I 6830l8

ОПИСАНИЕ

ИЗОБРЕТЕН И Я

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. саид-ву— (22) Заявлено 01.03.77 (21) 2457141/18-21 с присоединением заявки М— (23) Приоритет— (43) Опубликовано 30.08.79. Бюллетень ¹ 32 (45) Дата опубликования описания 31.08.79 (51) М.Кл. Н 03 К 13/20

1осудерственный комитет

СССР (53) УДК 621.314.27 (088.8) ло делом иэобретеии» и открыт»Й (72) Авторы изобретения

1О. Я. Личидов, В. Г. Трофименко и Б. В. Аксенов (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ ВРЕМЕННЫХ ИНТЕРВАЛОВ

В КОД

Изобретение относится к области вычислительной техники и может быть использовано в измерительных устройствах, в устройствах автоматики.и вычислительных устройст.вах.

Известные преобразователи временных интервалов:позволяют лишь преобразовывать одиночные или периодически повторяюшиеся временные интервалы, поступающие от одного источника 11, 2).

Наиболее близкое к изобретению техническое решение — преобразователь временных интервалов .в код, содержащий в каждом канале триггер основной памяти, триггер пуска, триггер дополнительной памяти, 15 а в групповой части — генератор счетных импульсов, ключ, счетчик, группу элементов

И, блок разрешения, схему блокировки, блок управления, блок памяти, блок вывода результатов преобразования 113). 20

Недостатком известного преобразовате.ля является то, что он не позволяет производить одновременные преобразования ,входных сигналов от нескольких источников, у которых начало временных интервалов разнесено во времени относительно друг друга. Это объясняется тем, что в нем ,индивидуально оцифровываются в блоке

7IBMIITH лишь моменты окончания:временных интервалов, а момент их начала должен быть общим для всех интервалов, так как он фиксируется в преобразователе только исходным (нулевым) состоянием счетчика. Следовательно этот преобразователь позволяет производить лишь одновременное преобразование нескольких временных интервалов, связанных друг с другом общим начальным (пусковым) моментом, что сужает функциональные возможности известного устройства.

Цель изобретения — расширение функциональных возможностей преобразователя.

Указанная цель достигается тем, что в преобразователь временных интервалов в код, содержапптй идентичные каналы преобразования по количеству одновременно преобразуемых .временных интервалов, генератор импульсов, выход которого подключен непосредственно к первому входу кaæäîãî канала преобразования и через ключ к входу счетного блока. выходы которого через блок элементов И соединены с ,информационным;: входамн блока памяти, управляющий вход которого подключен к входу блока вы вода результата, блок управления, первый выход которого подключен к управляющему входу блока элементов И, второй и третий выходы блока управления соединены соответственно с вторыми и третьимп входами каждого канала преобразо683018

l5

ЗО

55 !

G0 вания, первые выходы которых через блок разрешения подключены к одному из «ходов ключа, дополнительно введен блок вычитания, ВхОды HoT01!Oro подкл!Оче((ы «ыходам блока памяти. Выходы блока вычитания .поразрядно соединены с входами блока вывода результата. Выход генератора,импульсов подключен к четвертому «ходу каждогс канала преобразования, вторые выходы которых соединены с соответст«у ющими входами блока управления. Третьи и четвертые выходы каждого канала преобразования соединены с адресными входами блока памяти.

Кроме того, каждый канал преооразо«ания содержит триггер основной памяти, триггер дополнительной памяти, триггер пуска, сумматор по модулю два и два элемента И. Прямой выход триггера основной памятн подкл(очен к первому входу сумматора ло модулю два, первому входу первого элемента И, первому выходу канала преобразования и к прямому входу триггера пуска, инверсный вход которого является четвертым в одом канала преобразования.

Прямой выход триггера пуска лодключен непосредственно к первому .входу второго элемента И и через сумматор по модулю два .к управляющему входу триггера дополнительной памяти:и к второму выходу канала преобразования. Выход триггера дополнительной памяти соединен с вторыми входами первого и,втор ого элементов И, выходы которы.; являются соответственно третьим и четвертым выходами канала преобразования. Инверсный выход триггера основной памяти соединен с третьим входом второго элемента И, а инверсный выход триггера .пуска соединен с третьим .входом первого элемента И. Прямой и инверсный входы триггера дополнительной памяти я«ляются соответственно вторым и третьим входами канала преобразования.

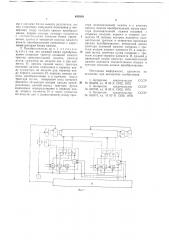

На фиг. 1 приведена структурная схема предлагаемого преобразователя; на фиг.

2 — временная диаграмма его работы.

Преобразователь содержит входную часть, разбитую на и независимых каналов (по числу временных интервалов), и групповую часть. На фиг. 1 ооозначены входы, на которые поступает сигнал, соответствующий началу одного из преобразуемых временных .интервалов, входы, на,которые поступает сигнал, соответствующий концу одного из этих интервалов, триггеры

1!,..., 1„осно«ной памяти, триггеры

2!,..., 2„пуска, .информационные входы которых подключены к прямым выходам соответствующих триггеров основной памяти, логпческ!(е элементы 8,,..., З„сложения по модулю д«а, входы которых связаны с прямыми выходами триггеров основ ной пачятп,и триггеров пуска, а выходы-с информационными входамн триггсро«

4„..., 4„дополнительной памяти, прямыс выходы последнего связаны с соответст«ующими входами элементов И 5(, ..., 5„ и 6(,...,б,.

Групповая часть преобразователя содержит генератор 7 счстных импульсов, «ыход которого соединен с одним .из входов ключа 8 и с синхрочизирующимн входами триггеров основной памяти и триггеров пуска всех;каналов, другой вход ключа подключен к выходу блока 9 разрешения, входы которого связаны с прямыми выходами всех триггеров основной памяти. Выход кл(оча подкл(0-reH K счетному входу счетно О блока 10, выходы которого через элемент

И 11 соединены с информационными входами блока 12 памяти, адресные «ходы которого подключены к выходам соответствующих элементов И 5(,..., 5,„и элементов И 6(,..., б„, а информационные выходы блока 12 памяти через вычитатель 18 соединены с входами блока 14 «ы«ода результатов преобразования, управляющий выход которого подключен к управляющему входу блока памяти. Входы блока 15 управления связаны с.выходами логических элементов сложения по модулю два, а один из входов блока управления соединен со стробирую!цими входами группы элементов И 11, два других выхода блока управления подключены к cooтветствуюшим cH!iхронизирующим входам всех триггеров дополнительной памяти.

Преобразователь работает следу(ощим образом.

Пусть на один,из входов триггера основной памяти, например, первого канала поступил сигнал, соответствующий началу первого временного интервала. По первому счетному импульсу. с генератора 7 он фиксируется в триггере 1! основной памяти. С появлением на прячом выходе триггера 1! основной памяти высокого уровня напряжения блок 9 разрешения переключается, формируя на выходе сигнал управления ключом 8. С этого момента последующие счетные импульсы с выхода генератора 7 начинают поступать через ключ 8 на вход счетного блока 10.

Одновременно с момента фиксации в триггере 1, основной памяти сигнала о начале данного временного интервала на выходе логического элемента 8! сложения по модул!о два начинает формироваться сигнал пуска, который поступает на информационный вход тргиггера 4! дополнительной памяти и на вход блока 15 управления. По этому сигналу блок 15 управлечия вырабаты«ает три управляющих импульса. Первый уира«ляющий импульс этой серии фиксирует сигнал пуска «три«перс 4 дополнитель«ой пачяти. На его прямом «ыходс поя«ляется сигнал с высоким уровнем напряжения, который через элемент 5 поступает на а !ресг(ы(! вход блока 12 памяти как сигнал

О о о я и1(I(«St Г(Огr> лгг ггг . гг чл °

683018

З0

15

65 памяти, подготавливая их к приему исходного, кода со счетного блока 10.

Второй управляющий импульс (импульс записи), сформированный блоков 15 управления поступает На стробируюший вход элемента 11 11 и осуществляет запись исходного кода счетчика 10 (т. е. производится оцифровка принятого сигнала о начале данного временного интервала) в,выбранные ячейки блока 12 памяти. Третий управляющий импульс этой серии поступает на вход сброса триггера 41 дополнительной памяти, переводит elo в исходное состояние и прекращает тем самым действие сигнала обра|цення к блоку 12 памяти.

С приходом второго счетного импульса с выхода генератора 7 триггер 2! пуска переходит в единичное состояние, что вызывает прекращение сигнала пуска на выходе логического элемента 8, сложечия по модулю два. Одновременно с этим счетный блок 10 подсчитывает поступающие на его вход счетные импульсы.

Аналогично происходит процесс оцифровки приходящих сигналов о начале временных интервалов и IIQ любому другому каналу, т. е. каждый раз в момент выработки сигнала обращения .к блоку 12 памяти в соответствующие его ячейки записывается текущий код счетного блока 10.

Пусть теперь в определенный момент времени на другой вход триггера основной памяти (на пример, первого канала) постулает сигнал 06 окончании данного временного интервала. Очередным счетным импульсом с выхода генератора 7 он фиксируется в триггере 1, основной памяти, что вызывает появление HB прямом его выходе низкого уровня напряжения. При этом на выходе логического элемента 81 сложения по модулю два вновь выделяется сигнал пуска, а блок 15 управления вырабатывает очередну!o серию управляющих импульсов, по,которым триггер 4, дополнительной памяти формирует сигнал обращения. Последний поступает на адресный вход блока 12 памяти (в данном случае через элемент б1) и в соответствующие ячейки его памяти записывается текущий код счетного блока 10, который соответствует сигналу,об окончании данного временного интервала. Последующим счетным импульсом с выхода генератора 7 триггер 2, пуска переходит в нулевое состояние, что вызывает прекращение сигнала пуска на выходе логического элемента З1 сложения по модулю два.

Аналогично проходит процесс оцифровки приходящих сигналов Об окончании временных интервалов и по любому другому каналу, причем с приходом сигнала об окончании последнего из преобразуемых временных,интервалов и фиксации его в соответствующем триггере 1„основной памяти блок 9 разреш-ния переключается в исходное состояние и запрещает прохождение через ключ 8 счетных импульсов на вход счетного блока 10. На этом заканчивается процесс оцифровки Всех поступающих сигналов о начале и конце преобразуемых временных интерваloB.

Далее с помон ьк. блока 14 вывода результатов преобразования осуществляется процесс последовательного считывания из ячеек блока 12 памяти в блок вы иггання 13 кодов, соответствующих концу и началу первого временного интервала. В блоке вычи1ания 13 пу т м вы I!iTBH!IH этих кодов oilределяется окончательный результат преобразования первого временного интервала в код и считывание его в блок 14 вывода результатов преобразования. Затем определяется код преобразования второго временного интервала, третьего и так дал"-е до и-го временного интервала. После вычислений и преобразований в код 13сех временных интервалов осуществляется установка счетного блока 10 Б IicxoäHoc cocTOHilHC u цикл p300Tbl прсооразователя вновь повторяется.

Предлагаемый преобразозате Ib временHhIx интервалов в код за счет обеспечения для каждого из независимых каналов поc;IepoBaTeльной оцифров H «a! сигнала, соответств чощего на галу временного интервала, так и сигнала, соопве1ствуюшего его концу, и последующего нахождения с помощью .вычитателя кода их разности. который является искомым кодом преобразуемого времечного интервала, позволяет расширить функциональныс возможности данного преобразователя по c!laB» нию с извести тм

Формула изобретения

1. Преобразозатель временныx интервалов в код, содсожащий иден Гичные каналы преобразования по колшгеству одновременно преобразуемых временных интервалов, генератор импульсов, выход которого подключен непосредственно к первому входу каждого канала преобразования и через ключ к входу счетного блока. выходы которого через блок элементоз 11 соединены с информационными входамп блока памяти, управляющий вход которого подклочен к входу блока вывода результата, блок управления, первый выход которого подключен к управляющему входу блока элементов И,,второй и третий выходы блока управления соединены cool BcTcTileH!io с Вторыми,и третьими входамн каждого канала преобразования, первые выходы которых через блок разрешения подключены к одному из входов ключа, о т л и ч а ю щл и с я тем, что, с целью расширения функцпанальных возможностей, в него дополнительно введен блок вы питания, входы которого подкл очены к выходам блока памяти. выходы блока вычитания норазрядHO соедине683018 ны с вхоламп блока вывода результата, зыход г: нсратора импульсов подключен к четвертому входу каждого канала преобразовапия, вторые выходы которых соединены с соответств. гцпми входами блока управления, третьи .и четвертые выходы каждого канала преобразования соединены с адресными, входами блока памяти.

2. Преобразователь по и. 1, о т л.и ч а юшийся тем, что каждый канал преобразования содержит триггер основной памяти, триггер дополнительной памяти, триггер пуска, сумматор по модулю два и два элемента И, причем прямой выход триггера основной памяти подключен к первому входу сумматора по модулю два, первому входу первого элемента И, первому выходу канала лреобразования,и к прямому входу триггера пуска, инверсный вход которого является четвертым входом канала преобразования, прямой выход триггера пуска аодключен непосредственно к первому входу второго элемента И и через сумматор по модулю два к управляющему, входу триг1. Авторское свидетельство

20 № 503359, кл. Н 03 К 13/02, 1973.

2. Авторское свидетельство

¹ 336793. кл. Н 03 К 13/02, 1970.

3. Авторское свидетельство № 343375, кл. Н 03 К 13/20, 1970.

СССР

СССР

СССР гера дополнительной памяти и к второму выходу канала преобразования, выход триггера дополнительной памяти соединен с вторыми входами первого и второго элементов И, выходы которых являются соответственно третьим и четвертым выходами канала преобразования,,инверсный выход триггера основной памяти соединен с третьим входом, второго элемента И, а инверс10 ный выход триггера пуска соединен с третьим входом первого элемента И, прямой и инверсный входы триггера дополнительной памяти являются соответственно вторым и третьим входами канала преобразования.

Источники информации, принятые во внимание при экспертизе изобретения:

683018! 1

Риа, 2

Составитель Л. Плетнева

Корректор С. Файн

Техред А. Камышникова

Редактор Е. Караулова лзказ 757/964 Изд. Хе 481 Тираж 1060 Подписное

НПО «Поиск» Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Тип. Харьк. фил. пред. «Патент»

1 !

1 1 1