Ячейка ассоциативной среды

Иллюстрации

Показать всеРеферат

О П И C А Н И-"И-

ИЗОБРЕТЕН ИЯ

Союз Советскин

Социалистических

Республик (6) ) Дополнительное к авт. свид-ву (22) Заявлено 29.01,76 (2l)2319938/18-21 (5I) M. Кл .

С 06 Г 7iOO с присоединением заявки М . (23) Приоритет

Геаударстеенньй квинтет

СССР на делам нзобретаннй н нткрытнй

Опубликовано 05,09.79. Бюллетень Ж 33

Дата опубликования описания 10.09.79 (53) Д (681.332 (088.8) (72) Автор изобретения

В, Г. Лак (71) Заявитель

Ростовский ордена Трудового Красного Знамени государственный университет (54) ЯЧЕЙКА АССОБИАТИВНОЙ СРЕДЫ

Изобретение касается автоматики и вычислительной техники и может быть применено как элемент Однородной вычислительной среды.

Известна ячейка однородных настраи5 ваемых структур, содержащая логический элемент, блок памяти и адресный блок, в которой логический элемент может настраиваться на выполнение одной или нескольких функций из заданного набора логических функций (1 ) .

Недостатком этой ячейки является то, что настройка ее может быть осуществлена только с помощью внешних управляющих устройств, в частности БВМ или .аапоминающих устройств, что сужает функциональные возможности устройства.

Известны также ячейки ассоциативной среды, содержащие каналы из соединенных последовательно канальных интеграторов, т управляемых сопротивлений и элементов сравнения, а также сумматоры, логические элементы, счетчик, преобразователи, усилитель и умножитель (2 j .

Недостатками этих ячеек являются большое число внешних выводов из-за ïàðности ВхОдных и ВыхОдных кОнтактОВ1 НОГ решности записанного значения аналоговой памяти из-за подверженности утечки заряда во времени, невозможность оперативного стирания записанной информации в памяти и невозможность. изменения дина» мического диапазона постоянных интегрирования.

Бель изобретения - уменьшение внешних выводов и расширение функциональных возможностей.

Для этого в ячейке ассоциативной среды, содержащей сумматор, каждый из входов которого соединен с соответствующей информационной входной шиной через канал, состоящий из последовательно соединенных канального интегратора, управляемого сопротивления и элемента сравнении, а выход сумматора подключен к входу умножителя, выход которого соединен с первым входом преобразователя напряжения в частоту, второй вход которого соединен с

684537

3 выходом интегратора, а выход преобразователя напряжения в частоту через цепочку из последовательно соединенных формирователей подключен к выходным шинам, выходы канальных интеграторов через дополнительный сумматор также подключены к одному из входов усилителя, выход которого соединен с другими входами элементов сравнения, и дополнительные канальные интеграторы, триггер Шмитта, три 10 алемента И, два элемента ИЛИ„два формирователя уровня, реверсивный счетчик и цифро-аналоговый преобразователь, другой выход интегратора через триггер

Шмитта соединен с первым входом первого элементе И, второй вход которого подключен к шине записи, а выход - к первому входу первого алемента ИЛИ, второй вход которого соединен с шиной запоминания, а третий- с выходом второго эле- 0 мента И. Выход первого элемента ИЛИ подключен к первому входу третьего алемента И и к входу прямого счета реверсивного счетчика, вход инверсного счета которого подключен к выходу второго элемента ИЛИ и. к первому входу второго элемента И, вход установки — к шине сброса, а выход — через цифро-аналоговый преобразователь, к другим входам

-умножителя и усилителя, а также через соответствующие формирователи уровня .к вторым входам второго и третьего элементов И, .причем выход последнего соединен с входом второго алемента ИЛИ, другой вход которого подключен к шине стирания, кроме того, в каждом канале выход элемента сравнения через дополнительный канальный интегратор соединен с управляющим входом управляемого

40 сопротивления.

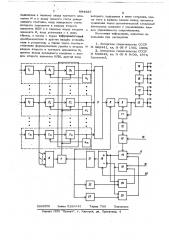

На чертеже представлена структурная схема предложенного устройства.

Каждый канал устройства содержит интегратор 1, управляемые сопротивления

2, элемент сравнения 3 и канальный интегратор 4. Выходы элементов сравнения

3 подключены к сумматору 5, а выходы

Р интеграторов 1 «к сумматору 6 и через усилитель 7 — к соответствующим алемен50 там сравнения 3. Выход сумматора 5 подключен к первому входу умножителя 8, который через преобразователь 9 напряг жения в частоту соединен последовательно цепочкой формирователей 10 выходных импульсов, каждый из которых соединен с выходными шинами. Выход интегратора

11 последовательно через триггер Шмит та 12, элемент И 13 и элемент ИЛИ 14 4 соединен с входом сложения реверсивного счетчика 15. Управляющий вход элемента И 13 подключен к шине записи 16, а второй вход элемента ИЛИ 14-- к шине запоминания 17. Вычитающий вход реверсивного счетчика 15 соединен через эле» мент ИЛИ 18 с шиной стирания 19, а вход установки реверсивного счетчика 15 соединен с шиной сброса 20. Выход реверсивного счетчика 15 подключен к входу цифро-аналогового преобразователя 21, выход которого соединен с вторыми входами умножителя 8 и усилителя 7, входами формирователей уровня 22 и 23. Входы элемента И 24 подключены к выходу формирователя уровня 22 и к выходу элемента

ИЛИ 14, а выход соединен с входом элемента ИЛИ 18. Выход формирователя уровня 23 через элемент И 25 подключен к входу элемента ИЛИ 14, а другой вход элемента И 25 соединен с выходом алемента ИЛИ 18..

Работа ячейки происходит следуюшим образом.

Входной поток импульсов . поступает через канальные интеграторы 1, управляемые сопротивления 2 и элементы сравнения 3 на сумматор 5. Входные импульсы .интегрируются с постоянной времени в канальном интеграторе 1. В зависимости от интенсивности входного потока импульсов по какому-либо каналу накапливается постоянная составляющая в дополнительном интеграторе 4 при постоянной времени интегратора Г >> <>, являю» щейся в данном случае кратковременной памятью интенсивности сигнала по данному входу ячейки, которым управляется коаффициент передачи сигнала по этому входу.

В дополнительном сумматоре 6 с постоянной ° времени заряда и разряда 4> (<< суммируются входные сигналы со всех входов ячей- . ки и через усилитель 7 поступают на все алементы сравнения 3, последними выделяются каналы с максимальными сигналами, Таким образом, в элементе сравнения 3 срезается по амплитуде (уровню интенсивности) входной сигнал по каждому каналу в зависимости от общей интенсивности входного потока на всех входах ячейки. На сумматор 5 поступают сигналы с входов, где произошло превышение сигнала относительно других входов, fIpoсуммированный аналоговый сигнал с сумматора 5 с постоянной времени Я, эС поступает в умножитель 8 и умножается на аналоговое значение напряжения, считываемого с цифро-аналогового преобраЯчейка ассоциативной среды, содержащая сумматор, каждый из входов которого соединен с соответствующей информационной входной шиной через канал, со« стоящий из последовательно соединенных канального интегратора, управляемого сопротивления и элемента сравнения, а вы« ходы суммагора подключены к входу умножителя, выход которого соединен с первым входом преобразователя напряжения в частоту, второй вход которого соединен с

Мыходом интегратора, а выход преобразователя напряжения в частоту через цепочку из последовательно соединенных формирователей подключен к выходным шинам, выходы канальных интеграторов через дополнительный сумматор также подключены к одному из входов усилителя, выход которого соединен с другими входами элементов сравнения, и дополнительные каналы интеграторы, триггер Шмитта, три элемента И, два элемента ИЛИ, два формирователя уровня, реверсивньп» счетчик и цифра-аналоговый преобразователь, о тличаю ю щ а я с я тем,что, с целью уменьшении внешних выводов и расширения функциональных возможностей, другой выход интегратора через триггер Шмитта соединен с первым входом первого элемента И, второй вход которого подключен к шине записи, а выход — к первому входу первого элемента ИЛИ, второй вход которого соединен с, шиной запоминания, а третий - с выходом второго элемента

И, при этом выход первого элемента ИЛИ

5 68453 зователя (ЦАП) 21, и далее поступает в преобразователь 9 напряжения в частоту

Преобразование напряжения в частоту им пульсов происходит с учетом обратной связи, поступающей от интегратора 11.

Постоянная времени интегратора 11, Эта отрицательная обратная связь формирует адаптацию по выходному сигналу. Импульсы с преобразователя 9 напряжения в частоту стандартиэируются 1р по амплитуде и длительности в формирователе 10 выходных импульсов, причем каждый последующий формирователь 10 в цепочке формирует импульсы, задержанные на величину длительности импульса. Задержки необходимы дпя учета эффективного действия ячеек в среде ко времени.

Триггер Шмитта 12 формирует периоды наиболее интенсивной импульсации ячейки.

Сформированный импульс с триггера Шмит- о та 12 через элемент И 13 и элемент

ИЛИ 14 поступает на прямой вход реверсивного счетчика 15. При наличии потенциального сигнала "1" (разрешение на

25 запись) на коммутирующей шине записи

16 этот импульс проходит через элементы И 13 и ИЛИ 14 в реверсивный счетчик 15. В реверсивный счетчик 15 могут быть записаны имйульсы также извне по

I зо шине запоминания 17 через элемент ИЛИ

14. Стирание значений с реверсивного счетчика 15 в динамическом режиме работы происходит подачей импульсов стира» ния по шине стирания 19 через элемент

ИЛИ 18 на инверсный вход реверсивного

35 счетчика 15. Количественные значения активной генерации ячейки записанные в реверсивном счетчике 15 преобразуются в аналоговую форму в ЦАП 21 и поступают в умножитель 8. Этим производится сопряжение характеристики преобразователя ячейки с предистарией его активностей. Аналоговое напряжение с UAH 21 постуйает на второй вход усилителя 7 и

45 управляет его коэффициентом усиления (для,уменьшении числа выделяемых каналов с максимальными интенсивностями сигналов), а также поступают на формирователи уровня 22 и 23. Формировате50 ли уровня 22.и 23, а также элементы

И 24,и 25 предназначены для предотвращения переполнения реверсивного счетчика 15 и предохранения от перестирания и потери информации. Формирователь уровня 22 срабатывает и выдает на выходе потенциал " 1" при значении аналоговой величины на выходе ПАП 21, превышающей, например 95% от мак.".имального его

6 значения. При этом на элемент И 24 поступает разрешающий потенциал и импульсы с выхода элемента ИЛИ 14, поступающие на суммирующий вход реверсивного счетчика 15 и на вход элемента И

24, с выхода его через элемент ИЛИ 18 поступают на инверсный вход реверсивного счетчика 15. Формирователь уровня

23 срабатывает при значении аналоговой величины напряжения на выходе ЦАП 21 меньшем 5 .4 от его максимального значения.

Тогда с выхода формирователя уровня 23 на элемент И 25 поступает разрешающий, потенциал . 1" и с выхода элемента ИЛИ

18 импульсы через элементы И 25 и

ИЛИ 14, поступают на прямой вход реверсивного счетчика 15.

Таким образом в предложенной ячейке оперативна управляется процесс. оаписи и стирания в реверсивный счетчик 15 однородной среды в процессе функционирования.

Формула изобретения

684537

ЦНИИПИ Заказ 5289/43 Тираж 780 Подписное

Филиал ППП Патент", г. Ужгород, ул. Проектная, 4 подключен к первому входу третьего элемента И и к входу прямого счета реверсивного счетчика, вход инверсного счета которого подключен к выходу второго элемента ИЛИ и к первому входу второго элемента И, вход установки - к шине сброса, а выход — через цифроаналоговмй преобразователь к другим входам умножи теяя и усилителя, а также через соотве ствующие формирователи уровня к вторым 10 входам второго и третьего элементов И, причем выход последнего соединен с входом второго элемента ИЛИ, другой вход которого подключен к шине стирания, кроме того в каждом канале выход элемента сравнения через дополнительный канальный ийтегратор соединен с управлякнцим входом управляемого сопротивления.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

% 328441, кл. 6 06 F 1/00, 1969.

2. Авторское свидетельство СССР.

М 533948, кл. 9 06 К 9/00, 1974 (прототип) .