Интерполятор

Иллюстрации

Показать всеРеферат

(72) АвтоР яаобретення

Ю С Ицкови ч с (7I ) Заявитель (54) И НТЕРПОЛ ЯТОР

- поляции.

Изобретение относится к области ав» томатики и вычислительной техники, в частности к устройствам для интерполяции сигналов полосового спектра.

Известен ингерполятор, содержаший сумматор, ключ, регистр н интегратор (1).

Известен также ингерполятор содержа» ший регистры, элемент задержки, цифроаналоговые преобразователи н интегратор

И. î

Обшим недостатком известных устройств является пониженная точность интерПрототипом изобретения является ингерполятор сигнала, содержашнй ннтегра« торы и группу последовательно соединенных регисгоов. подключенных выходами к входам формирователя разности (гъ -1) -го порядка, причем вход первого регистра является входом ннтерполятора (33 .

f eäîcòaòêoM прототипа является пониженная точность интерполяции амплитудно-частотных характеристик полосовых. ссео оз, а 1 затеи . нс r .,м;.,ес л б..о, отела Ч Б Л спектров прн наличии высокочастотных помех.

Целью изобретения является повышение точности интерполяции сигнала полосового спектра путем подавления высокочастотных помех

Поставленная цель достигается тем, что в ингер олягор дополнительно введены вычигатели, усреанители и согласуюший делитель, подключенный входом к выходу формирователя разности (tt -1}-го порядка и соединенный выходом с входом первого интегратора, причем выход каждого 1 -го из (И -1) интеграторов соеди нен с первым входом 1 -го вычитателя и подключен через j -й усреднитель к второму входу того же вычигателя, выход каждого 1»го из (И -2) вычитателей соединен с входом (j+1)-ão интегратора, а выход (П-1)-го вычнгателя подключен к выходу ингерполятора.

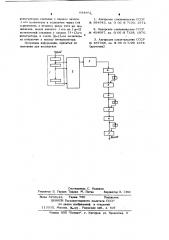

На чертеже изображена блок-схема устройстваа.

684 562

Интерполятор содержит группу 1 ггоследовательно соединенных регистров, выходы которых подключены к входам формирователя 2 разности (г1 1)-го порядка, а вход первого регистра соединен с входом интерполятора. Выход формирователя 2 через согласующий делитель 3 подключен к входу первого интегратора

4, выход каждого 1-ro интегратора 4 из (И -1) интеграторов соединен с первым входом 1-ro вычитателя 5 и подключен через 1 -й усреднитель .6 к второму «ходу того же вычитателя. Выход каждого 1-го из (г{ -2) вычитателей 5 соединен с входом (3+1)-го интегратора 4, а выход ({{ -1)-го вычитателя 5 подключен к выходу интерполятора, Интерполятор работает следующим образом.

Опорные значения входного сигнала в цифровом виде поступают через равные промежутки времени, соответствующие периоду квантования входного сигнала, на вход первого регистра из группы 1 последовательно соединенных регистров. При записи очередного значения входного сигнала в первый регистр предыдущее значение переписывается во второй регистрг а еше более ранние значения переписыва30 ются в следующие регистры в порядке очередности. С выходов всех регистров опорные значения входного сигнала поступают на формирователь 2 разности (г{-1)-го порядка. Формирователь 2 производит попарное вычитание соседних эна33 чений входного сигнала, вычисляя разности первого порядка, далее производит попарное вычитание соседних разностей первого порядка, вычисляя разности второго порядка и так далее, до получения разнос40 ти ({{»1)-го порядка на выходе. Разность { {{-1)-го порядка с выхода формирователя 2 через согласующий делитель

3 поступает на вход первого интегратора

4. Интегратор 4 работает с требуемой

4S частотой квантования выходного сигнала.

Выходной сигнал интегратора 4 поступает в первый усреднитель 6, где вычисляется его постоянная составляющая, и в первый вычитатель 5, на второй вход которого поступает выходной сигнал первого усреднителя 6. В вычитателе 5 производится вычитание иэ выходного сигнала интегратора 4 постоянной составляющей, сформированной в усреднителе 6. С выхода первого вычитателя 5 сигнал поступает на следующий интегратор 4. Лаг{ее вышеуказанные процессы повторяются.

Выход (г{-1)-ro вычитателя 5 является выходом интерполятора, сигнал на котором соответствует входному сигналу, проинтерполированному с требуемой частотой квантования.

B качестве интеграторов 4 в интерполяторе используются накапливающие сумматоры.

Изменяя коэффициент деления согла» сующего делителя 3, можно изменить коэф .ициент пропорциональности между входным и выходным сигналами интерполятора.

Иэ приведенного описания видно, что в интерполяторе (Ц-1)-я производная выходного сигнала в течение периода квантования входного сигнала остается постоянной и равной разности (n-1)-го порядка в опорной точке входного сигнала, При каждом интегрировании производной вырабатывается производная более низкого порядка, которая повторяет соответствующую разность входного сигнала с точностью до постоянной величины, ата постоянная величина отфильтровывается с помощью усреднителей 6 и вычитателей

5. В реэульrare многократного интегрирования сигнала, поступающего с формирователя 2, его высокочастотные составляк-шие {тодавляются пропорционально (г{- 1)-й степени частоты. В то же время поло"а частот в диапазоне ориентировочно от одной десятой частоты квантования входно-.

{ о сигнала {1o одной второй частоты квантования передается на выход интерполя ора с высокой точностью, практически беэ искажений, что и обусловливает преимушество данного интерполятора перед известнь{ми устройствами.

Формула изобретения

Интерполятор, содержащий интегратс ры и группу последовательно соединенных регистров, подключенных выходами к входам формирователя разнос ти (P-1 )-го порядка, причем вход первого регистра является входом интерполятора, о т л ичаюшийс я тем, что, сцельюповышения точности интерполяции сигнала полосового спектра путем подавления высокочастотных помех, в интерполятор дополнительно введены вычитатели, усреднители и согласующий делитель, подключенный входом к выходу формирователя разности (г{-1)-ro порядка и соединенный выходом с входом первого интегратора, причем выход каждого 1 -го из ({3 — 1) 684562

Составитель С. Казинов

Реиентор Б. Гериен Тенреа M. Bema Керренгор Н. Стеи

-"аказ 5290/44 Тираж 780 Подписное

11ГтИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, 35 Раушскаи наб., n. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4 интеграторов соединен с первым входом

j -го вычитателя и подключен через j-й усреднитель к второму входу того же вычитателя, выход каждого -ro из (д-2) вычитателей соединен с входом .(1+1)-го интегратора, а выход (ц-1)-го вычнтателя подключен к выходу интерполятора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

М 364943, кл. G 06 G 7/30, 1971

2. Авторское свидетельство СССР

M 404097, кл. G 06 G 7/28, 1970.

3. Авторское свидетельство СССР

Мр 467368, кл. 9 06 Э 7/30 1974 (прототип).