Преобразователь угла поворота вала в код

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Реслублик

ОП ИСАНИ Е

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВ ()684578 (61) Дополнительное к авт. свид-ву— (22) Заявлено 11.03.77 (21) 2461458/18-24 с присоединением заявки №вЂ” (23) Приоритет— (5l) М,К .

G 08 С 9/04

Государственный комитет

СССР оо делам нзооретеннй н открытий (53) УДК 681.325 (088.8) Опубликовано 05.09.79. Бюллетень № ЗЗ

Дата опубликования описания 15.09.79 (72) Авторы изобретения

А. С. Буданов, А. А. Гаврилов, В. П. Максимов и Е. Ф. Тупиков (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД

Изобретение относится к автоматике и вычислительной технике, может быть использовано для преобразования угла поворота вала в код.

Известен преобразователь углового положения вала в цифровой код, содержащий 5 вращающийся трансформатор, соединенный со входами сумматоров, выходы которых через фазочувствительные выпрямители подключены к первым входам вентилей, вторые входы которых подключены к выходу генератора импульсов, а выходы соединены через реверсивный счетчик и преобразователь

«код — напряжение» (11.

Недостатком этого устройства является малая точность.

Наиболее близок к предлагаемому пре- 15 образователь угла поворота вала в код, содержащий преобразователь напряжения в частоту, три формирователя синусоидального сигнала, фазовый синхронный детектор. задающий генератор, выход которого подключен ко входам двух делителей частоты, выход первого делителя частоты соединен со входом первого дешифратора, два выхода которого через формирователи синусоидального сигнала подключены ко входам синусно-косинусного вращающегося трансформатора, выход блока управления подключен ко входу реверсивного счетчика, выход которого соединен со входом блока ввода кода, выход блока ввода кода подключен ко второму входу второго делителя частоты, выход которого соединен со входом второго дешифратора, выход первого делителя частоты через формирователь импульса ввода кода подключен к управляющему входу блока ввода кода (2 .

Недостаток устройства — низкая точность преобразования угла поворота вала в код и низкая разрешающая способность преобразователя, которые объясняются нелинейностью преобразования, температурной нестабильностью элементов и трудностью реализации работы преобразователя с высокой частотой задающего генератора.

Цель изобретения — повышение точности и разрешающей способности преобразователя угла поворота вала в код.

Согласно изобретению постчвлеHt.àÿ цель достигается тем, что в устройство введены интегратор, четвертый формирователь сину68-1 578 (. 0H, (3,:1 H НОГО (И Г Н (Е>Л! Ь! И,>((Л И 1 (< )I I> II «К ОД - l! и I I P Я Ж (. 1! И С >>, а М I I Cf И Т >> Д Н Ы Й С И и—

xJ)ñ>II H 13!>I Xu>I, !!ТОРОI О . (<>III И(() J) И и ГО i t < I I I f ) SI—

ih(н и и и Од к, l I(> I(fl к It(1) !30 л! ч !3 х О, I i (. i il if il f) i -!

Оп(с !0 блока, второй Выход второго леп!ифрап>р;«! p(з четверть!й (j)0 f)it ltðîâÿòå, ll> синуСОИД<3,1ЬНО(О <, ИГИЯЛ <1 (??(.(?? lf(ll \ fl(. f)13 hl ?? !!???? ?????? ?????????????????????????????? ??ku;f -- ??????????????????????, 3(> второй вход которого полклк)чен к выходу младших разрядов реверсивного счетчика, а выхол преобразователя «код--напряжение»

II<>;(KJf E0 I(. ll h0 и ГО f)Oil i ВХО LЛ С Л". 31lt f)>< E()И(с(0 ();10K;1, БЫ ХО;(КОТОРОГО I (. J)(.» У II P;I и, I Sl(il I l И (с з ИТГ IЬ IIHIIpsl)KCIIIIH llu;1K 1К)

Бxоду О, I0кя ср<1В(н>11 И Я, Втоp(>и Б ;(). (б, luhя сравнения, подключен к выходу синусно-коси. нусного вращак>щегося трансформатора, Быxo<(блока сравнения через избирательный уси,!итель подключен Ки входам фазово!О и амплитудногu синхронных детекторов, Bf>fxol фя»<и>ого сlitlxpolliluf 0 .I(. текторя и<>лклк>ч II

К О Б Х О; (и Ч I I Р (О () P . 1 и I I B I I f ) Sf )K u I I I I St 13 и;1 Tu ki ll иорогol301 б, IOKB, !3ь!хо.(ы к<> ГОf) hIX П ОЛКЛ 10 1 I II>l КО БХО (Я М 0.10КЯ i ll f) <113,1(. 2> ния, в! !ход яч! III Ti;(lful o cHllxpullliuf летекто);I через и!ГгегпятuJ) (О(линеí o Бторыч

ВХО (Oil i I IP;1 Б, 1 Я<> 310 f u, ((! 11ТC,! Я if

Tf)(. гий If чсli3(рг! !й I31>lxuды Втор<но . (си!ифPI h0 f3T0Phlil БХ<>ЛЯ)1 ЯМ3(3 (диту.п!Ого ll (!>((з013010 HIIXpullfll>i !С(СKT(iРО В.

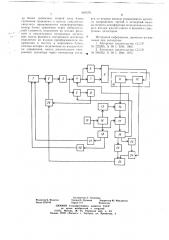

11я i(ерТСЖ(llpll B(>.l(>kl;l Tp i Кт 3 pfIBH з I(. hTричсскяя схема устройства. Преобразователь солержи Г сину(я!О-косинусный врац(акицийся Tf>dlfc(f)upi!

19, формирователи синусоидальных сигналов 20 — 23, преобразователь «код — напряжение» 24, суммирующий блок 25, управляемый делитель напряжения 26.

Выход задающего генератора 15 подключен ко входам делителей !астоты 16 и 17. выход делителя 16 через дешифратор 18 и формирователи синусоидального сигнала

20, 21 подключен ко входам синусно-косинусного вращающегося трансформатора 1.

Выход блока сравнения 2 через реверсивный счетчик 10, блок ввода кода 14 и делитель частоты 17 соединен со входом дешифратора 19.

Выхол делителя ч(!с(отhl 16 через формиров<>гсль импульса Бволя кода 13 подклк> и и к управляк>щему Входу олока вводя кода 14. Иср!3!!й выход лешифратора 19 через формирователь сииусоидального наиряж llllH 22 Ilo.(êëlo÷uí к пс рв<>му Вхо.(ó суilililpi ющего олокя 25, второй выход де-! иифряторя 19 через формирователь синусоидяльffufo сигнала 23 соединен с одним из вхс>дс) Б преобразс>!3атсля «кол — напряжение»

24, второй вход которого подключен к выходл ч,ld Llff ltx разрядов 12 ре в(. рсиВнОГО счетчика 10, а Бхол преобразователя «ко:L-l1s1flf)(жние>> 24 подключен ко Второму Входч суммирующеfu блока 25, выход последисго через управляемый лслитель напряжения 26 подключен к одному из вхолов блока с равнения 2.

Ehfopui Bxus(блока сравнения 2 подклюцп к вы.(олу сину Ho-косинусного врящак>ll(C I OCH T f) d I3C(J)Oj) Ëff X03, О 10Кя с J)B 13!1<>IIHst 2 Hерс» изоират(,ihflhIH i CH IHT(..

3 НО,(к,иОч(fl ho Бходам синхронных д(.тс ктоj)013 4 H >. Вь!хол фазОВОГО HH? J)Off Hof 0 д<>k KTuf)B 4 flu;(K.IK) I(>11 KO BXOLLdif пр(.ооря»0Бате fs»f;IffpstH(e«I>st Б чястотл 6 и llupufuBOf О блока 7, d их выхолы подключены ко вхоляч олока управления 9. Выход амплитудного сги!Хрошюго детсктора 5 через интегря H)p 8 со(ли нен с0 BTuph! м Входом i llpd Bляс м<>п> лелитсля напряжения 26. Третий и четвертый Выходы лешифрятора 9 полклк>чены ко БтОрым входам синхрОнных лет(.ктОf)ÎB.

У Tpulfc ВО работа(.T с.l<.,Li K)IL(H м Образо)(.

СКВТ 1 преобразует угол поворота вяла в напряжение, фа»с>вь(й сдвиг которого пропорционален углу поворота валя. Напряжение с выходной обмотки СКВТ 1 поступает на блок сравнения 2, в котором складывается в противофазе с кол!пе!3сирл ющим сигналом, вырабатываемым совокупностью блоков 10--26. В результате сложс ния выделяется и усиливается первая гармоника напря)кения питания СКВТ 1, несу(цяя информацHIo как о фазовом, так и об амплитудном разбалансе сравниваемых напряжений.

Избирательный усилитель 3 в цепи выделения рассогласования по фазе определяет постоянную времени, хара ктеризук) щую динамическую характеристику преобразователя, которая до некоторых пределов линейно зависит от скорости изменения угла ротора СКВТ и исключается расширением динамического диапазона преобразователя напряжения в частоту 6.

Выделенная и усиленная в результате сравнения первая гармоника, равная частогс питания, попадает на фазовый и амплитудный синхронные детекторы 4 и 5. Следует отметить, что опорные напряжения для детекторов формируются из компенсирующего канала, жестко связаны с ним по фазе, а друг относительно друга сдвинуты на 90 .

Детектор 5 выделяет напряжение, пропор684578

5 циональное Величине расс!>гласов!)ния по фазе, з>!Вк и величина его !>Иредег!як>т режим работы Л1(1!У, т. с. слож Hlfl или вычитаHHL имнуг!ьс3>!3 от преобразователя нанряжс ния в частот 6. 113>рс>гов!.!Й блок 7 13

СОВОКX 11 HОСТ И С ОЛ ОКО т команды режима р lf>(>TII реверСИHИОГО IЕтЧИКcl 10. ЛМПЛИTóËIII>lй СиихрОНны Й деTектОр 4 иы Т1.,! Яст IidllpH)Hcfllil, llp0ll0pllH0Hd IblI0c Величине амплитудного разО а Л а Н С а C P c) 13 f I H f3 го !елитсля напряжения 26.

Заполнение реверсивного счетчика 10 iip0до, 1)кается дo тех HOp, IIOKB фазОВыи сде)НГ х!ежду напряжениями В блоке сравнения не станет равным 180" . По мере уме ньшения

ФЮ фазового разбаланса уменьщаегся часTOTа заполнения с<ц тчик i 10. cl колебательный рсжим у положения равновесия исклк>чаетСЯ С помоц(ЫО IIOpOI ОНОГО 0,!ока !, IIOp01 чувствительности к!>Т3>р!>Го должен быть равным половине цепь! м,lадшего разряда. От 20 задающего генератора 15 импульсы поступают на;)елители частоты 16» 17 с одинаковыми коэффициентами 1(лс)щя. Информация с трех последних разр,lOB )ег!Нтелей частоты поступает на дешифраторы 18

29 и 19, которые формиру!от временные участки.

Синусоидальный сигнал формируется путем кусочно-линейной аппроксимации. Сформированные и усиленн)!е напряжения с формирователей синусоидального сигнала 20 и 39

21 пода!отся на первичные (статорные) обмотки СКВТ 1.

Фаза компенсационного напряжения изменяется путем Ввода начального числа в делитель частоты 17 (один раз за период формируемого сигнала). Число, записанное

И в старших разрядах реверсивного счетчика

10, через блок ввода кода 14 записывается в делитель частоты 7 в момент, когда в делителе частоты 16 все триггеры переходят из состояния «1» и «О». Данный момент 40 фиксируется формирователем импульса ввода кода 13, который вырабатывает короткий импульс для записи числа в делитель частоты 17. Дешифратор 19 и формирователи синусоидального сигнала 22 и 23 работают аналогично узлам 18, 20, 21. Квадратурная составляющая, снимаемая с формирователя синусоидального сигнала 23, подается на преобразователь «код-на пряжение» 24, амплитуда сигнала с которого определяется числом, записанным в младших SO разрядах 12 реверсивного счетчика !О. На выходе суммирующего блока 25 после сложения получается напряжение, фаза которого зависит от числа, записанного в реверсивном счетчике.

При изменении числа в младших разрядах 12 счетчика !0 происходят малые изменения фазы компенсирующего напряжения, снимае.; о с сумчир) н>цц г» f>,"«1;;. 2)7> l;менение же числа В cTHðliièx p;i рядах xOI >i бы на единицх пызын;!3 . Ки ио>)>б>рг)знги из. аЗЫ h(>XIHC ih ill ) 1< >1: ic i« ) и <)пряж< .

lll1H. Лхп)литмдн! !!1 iiiixp(>lil!, и т hTL>j) 5

БЬ!ДС ЛЯЕТ fl;III Р>!жс!!По, liP>

(В е. I l l ; I. I < I i l c 1, h 0 I (>1) a > c через интегj);iTOp 8 !и )Bcòñ>1 ll;) ) Ilp;li3, !я )I!„Il делитель напряжения 26, к<>т)>р! Н1 изм) п>1е!)!чнлитхду кохи)енсир) юивчо н!)пряя<еilll>l, поступающего на один из !)хо !1>!3 бл)>кfl

«p1 C Ill H H, 1 <1. 11 j)()11() р ционального ах)плитудн(>)!x разбал !Нсх инфоР I. ж). НИЙ, B ТРВКТЕ BBIH!3 IЕНИЯ ф<)ЗОВОГО Р<13баланса между указанными напряжениями

II()3f301HcT II0BhicIfTh ра:31)l. ц),)к>ц1 < 10 способIi T0HH0СТь а н а.1010-10)ф рового и реоб;);i ç 0B à ò åл я.

ФО!>.!!!!.)а !!зоб!>г тени.<г

Преобразователь угла поворота Ва за в код, содержащий преобразователь 1)апряжения в частоту, три формирователя синусоидального сигнала, фазовый синхронный детектор, задающий генератор, выход котороI 0 подключен ко Входам дву. делителей частоты, выход первого делителя частоты соединеH CO BX030iXI IICр!30ГО;1(IlliigpBTOpd, дВВ !

)ЫХО 1а КОТОРОП) Ч(PCB ч>ОРМИРОВВТЕ1И Сllнусоида IBHOIo сигнала подключены ко I)x0дам синусно-косинусного вращающегося трансфорх!атора, Выход 0,10ка мпраВзения подключен ко вя>ду реверсивного счетчика, выход которого соединен с0 входом реверсивного счетчика. выход которого соединен со входа м второ гÎ де, ш тел я ч астоты, выход которого соединен со входом второго дешифратора, выход первого делитсля частоты через формирователь импульса ввода кода подключен к управляю)цех!х входу блока ввода кода, От.ги<га>ощгшс.г тем, что, с целью повышения его точности и разрешающей способности, в него введены интегратор. четвертый формирователь синусоидаlbHolo сигна;1à, блок сравнения, избирательнь;й усилитель, пороговый блок, управляемый делитель напряжения, преобразователь «коднапряжение», амплитудный cHHxpoHHBIH детектор и суммирующий блок, первый выход второго дешифратора через тре ий формирователь синусоидального напряжения подключен к первому входу суммирую!цего блока, второй выход второго дешифратора через четвертый формирователь синусоидальног0 сигнала соединен с первым входом преобразователя «код — напряжение», второй вход которого подключен к выходу младших разрядов реверсивного счетчика, а выход преобразователя «код — напряжение» подключен ко второму входу суммирующего блока, выход которого через управляемый делитель напряжения подключен к первому вхо684578

Составитель Г. Антонова

Техред О. Луговая Корректор Ю. Макаренко

Тираж 710 Подписное

ЦН И И П И Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5 филиал ППП «Патент>, r. Ужгород, ул. Проектная, 4

Редактор Ь. Федотов

Заказ 5293/45 ду блока сравнения, второй вход блока сравнения подключен к выходу синусно-косинусного вращающегося трансформатора, выход блока сравнения через избиратель, ный усилитель подключен ко входам фазового и а м илитудн ого синхронных детекторов, выход фазового синхронного детектора подключен ко входам преобразователя напряжения в частоту и порогового блока, выходы KQTopblx подклк>чены ко входам блока управления, выход амплитудного синхронного детектора через интегратор соединен со вторым входом управляемого делителя напряжения, третий и четвертый выходы второго дешифратора подключены ко вторым входам амплитудного и фазового сННхронных детекторов.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 222205, G 08 С 9/00, 1964.

2. Авторское свидетельство СССР № 546922, G 08 С 9/00, 1975.