Элемент памяти для динамического регистра сдвига

Иллюстрации

Показать всеРеферат

L о:з, 1е 4 па1еч н, 1

C А Н Й Е

СПИ (684617

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 03.03.77 (21) 2458733/18 — 24 с присоединением заявки РЙ (51)М. Кд.

G 11 С 19/00

Гооудврственнье квинтет

СССР оо делам нзооретеннй к открытей (23) Приоритет

Опубликовано 05.09.79 Бюллетень Ж 33

Дата опубликования описания 05.09.79 (53) УД К 681.327..66 (088.8) (72) Авторы изобретения

Б. В. Кузнецов, Е, И. Потемкин и Ю. А. Уральский (71) Заявитель (54) ЭЛЕМЕНТ ПАМЯТИ ДЛЯ ДИНАМИЧЕСКОГО.

РЕГИСТРА СДВИГА

Изобретение относится к области вычислительной техники, в частности, к запоминающим устройствам.

Известны элементы памяти для регистров сдвига на МДП-транзисторах, в которых приме5 няются переключающие и нагрузочные транзисторы с кратковременным запоминанием сигнала переноса на конденсаторе (11.

Известны также динамические сдвиговые регистры, элементы памяти которых выпол о иены на МДП-транзисторах, содержащие в каждом разряде шесть транзисторов: два инвертора на 4-х транзисторах, два дополнительных транзистора и два конденсатора (2).

Однако известные элементы памяти для динамических сдвиговых регистрах потребляют большую мощность в момент переключения и, кроме того, критичны к нижнему частотному пределу работы из-за конечного времени хранения заряда (логическнх уровней) на паразитных емкостях МДП-транзисторов. Обычно нижняя граница рабочих частот динамических регистров лежит в диапазоне частот 1,0-10 кГц, Как правило, подобные регистры обладают не очень высокой надежностью (частые сбои информации) из-за хранения информации на паразитных емкостях.

Целью изобретения является уменьшение потребляемой мощности, увеличение надежности, расширение нижнего частотного диапазона работы.

Это достигается тем, что в элемент памяти введены разделительные элементы, например, диоды, одни из которых включены между переклн1чающими элементами, нагрузочными weментами и тактовыми шинами и триттерами соответственно, а выходы первого триттера соединены с выходами второго триггера и входами третьего триггера, выходы которого соединены с выходами четвертого триггера.

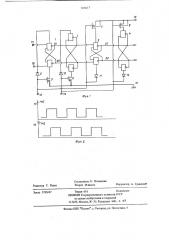

Сущность изобретения поясняется чертежом, где на фиг. 1 представлен предложенный элемент памяти для динамического регистра сдвига; на фиг. 2 — диаграмма подачи импульсного питания (тактового).

Элемент памяти содержит триггеры 1, 2, 3 и 4, переключающие 5 и 6 и нагрузочные 7 и 8 элементы, выполненные на МДП-транзисто684617

paxð раздРлитель? ые эчемееп ь! 9 10 l 1 «1 2) например, диодь1, подкшечепные к т 1ктовы: шинам 13 и 14, шину 15 питания, ши!!у 16

I нулевого потенциала и информашп1нные и1ины 17 и 18.

Элемент памяти для ди?!аь!!Гческого регистра сдвига работает следующим образом. IIpc!.;положим на информацно!шую шипу 1 7 подана логическая едишща, а па шину 18 — соответстве?шо логический нуль.

При низком урок!а нхо??ного с!И.нала !1а шине 13, на выходах 19, 20 тр?итера 1 бу. дет большое выходное сопротивление, Обуслов ленное обратными токами утечки диода 9 i транзистора 5. Трште1э 2 в это время находится В аналогичном состоянии, т-ак как На

IIBHIc 14 низкий уровень BxoHHorо с!!гпа?!а, В момент пр!иода положителы!Ого импульса на шину 13 через диод 9 будет подано питание, на триггер 1 через транзистор 5 подастся уровень шины 16 нулевого потенциала. Tpiirrep 2 запоминает информацию, !?Оступившу?о с триггера 1 через шины 19, 20. Отрицательным фронтом импульса, поступающего по шине 13, закрываются диод 9 и транзистор 5, а транзистор 7 и диод 11 открываются. Иа триггер 3 подается питание через транзистор 7 и уровень логического ну!гя через диод 11.

Информация с тр!птера 2 переписывается в триггер 3, па выходе 21 будет уровень логической единицы, а на выхоце 22 уровень логического нуля. При поступлении па шины 13 и

14 вторых положительньп импульсов процесс повторится. Таким образом, происходит сдвиг. информации в зависимости от того, что подано на входы 17 и 18.

Предлагаемый элеме?п памяти дчя дп?!ам!1ческого регистра сдвига на МДП-транзисторах обладает меньшей потребляемой мшцнастыа за счет того, что тр?Итеры предварительно подготав!?иваются к работе до момента подачи импульсного питающего напряже?п?я, и новь?шенной надежностью и расширеш!ым ннжннм частотным диапазоном работы из-за отсутствия запоминания информации на параз?!т!?ь!х емкостях.

11е!!ссообразно использование д!а??ного элемен1а памяти для динамическо!о регистра сдвига в интегралыгых схемах 3НВМ и устройств ав. томатики.

Формула изобретения

Элемент памяти для динамического регистра cpanra, содержащий триггеры, переключающие и нагрузочные элементы, выполненные на МДП-транзисторах, шины питания, тактовые, нулевого потенциала и информапионные шины, подключенные к первому триггеру, о т л ич а ю шийся тем, что, с целью уменьшения мощности, потребляемой элементом памяти за счет предварительной подготовки триггеров, повышения надежности и расширения частотного диапазона элемента, в него введены разделительные элементы, например, диоды, аноды одних из диодов подключены к затворам МДП-транзисторов переключающих элементов и к тактовым шинам соответственно, катоды их соединены с первым и вторым триггерами, като„ и других диодов подключепы к затворам МДП-транзисторов нагрузочных элементов и к тактовым шинам соответственпо, аноды их соединены с третьим и четвертым триггерами, триггеры соединены со стоками МДП-транзисторов перекл!Очаю!шах и нагрузочных элементов, истоки МДП-транзисторов переключающих элементов соединены с шиной нулевого потенциала, истоки МДП-транзисторов нагрузочных элементов соединены с шиной питания, выходы первого триггера соеIIII?ie?III с входами второго триггера и входами третьего трштера, выходы которого соединены с выходами четвертого триггера.

Источники информации, принятые во внимание при экспертизе

1. Патент Японии 49 — 38060, кл. G 11 С 19(00, опубл. 15.10.74.

2. Букреев И. H. и др. Микроэлектронные схемы цифровых устройств. М,, "Советское радио", 1975, с. 153 (прототип), 684617

pU2. 1

Составитель E. Потемкин

Техред M.Ïåòêî

Корректор А, Гриценкб

Редактор С. Равва

Заказ 5298/47

Тираж 681 Подписное

ЦИИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4