Коммутатор

Иллюстрации

Показать всеРеферат

1 iii684742

Союз Советскнж

Соцналнстнческнх

Республнн (61) Дополнительное к авт. свид-ву—

{22) Заявлено 14.04.77 (21) 2474367/18-21 с присоединением заявки М— (23) Приоритет— (5! )М. Кл.

Н 03 К 17/66

Гкударстваииь и комитет

СССР ив дтхам иза5Рейиий и атирнтий

Опубликовано 05.09.79. Бюллетень,% 33

Дата опубликования описания 15.09.79 (53 ) УД K 621 З82 (0888) (72) Авторы изобретения

А. 3. Иванников и А. Д. Кравцов (71) Заявитель (54) КОММУТАТОР

Изобретение касается вычислительной тех п1ки. Оно предназначено, например, для управления матрицей постоянного, электрически црограммируемого запоминающего устройства про- извольной емкости.

Известен коммутатор, каждый разряд которо5 го выполнен на двух и — р — н транзисторах и резисторах, причем эьпптеры транзисторов объединены между собой и соединены с шиной нулевого потенциала, коллекторы также объединены о между собой и подключены к выходу устройства и через резистор — к шине питания, а базы транзисторов связаны через резисторы с соответствующими входами селектора.

К недостаткам данного устройства относятся

35 сравнительно высокое напряжение питания и высокое потребление тока от источника питания.

Известен также коммутатор содержащий в каждом разряде два п — р — и транзистора, эмил;еры и коллекторы которых объединены, прн этом коллекторы, подключены к выходу коммутатора.

Однако этот коммутатор также имеет высокое напряжение питания и повышенное потребление тока.

Цель изобретения — снижение потребляемого тока и напряжения питания.

Это достигается тем, что в коммутатор, содержащий и каждом разряде два и — р — д транзисторй, змиттвры и коллекторы которых объединены между собой, при этом коллекторы соединены с выходом коммутатора, в каждый разряд допол ятельно введены два инжектнрующих р — п — р транзистора, коллекторы которых объединены с базами соответствующих и — р — н транзисторов и подключены к соответствующим входам коммутатора, эмиттеры р — п — р транзисторов соединены с соответствующими шинами питания, базы р — и — р транзисторов объединены и присоединены к объединенным эмиттерам и — р — и транзисторов и к шине нулевого потенциала.

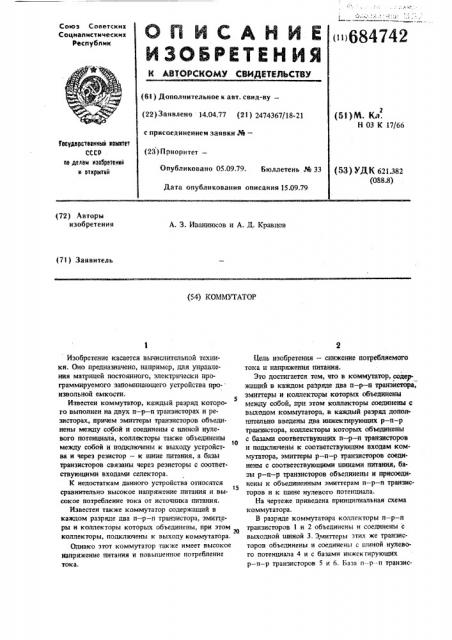

На чертеже приведена принципиальная схема коммутатора.

В разряде коммутатора коллекторы и — р — п транзисторов 1 н 2 объединены н соединены с выходной шиной 3. Эмиперы этих же транзисторов объединены и соединены с шиной нулевого потенциала 4 и с базами инжекгирующнх

p — и — р транзисторов S и 6. База и — р — и транзис3 6847 тора 1 объединена с коллектором р — и — р транзистора 5 и присоединена к выходной шике 7. База и — р — и транзистора 2 объединена с коллектором р — и-р транзистора 6 и с входной шиной 8.

Эмнттер р — и-р транзистора S подкл1очен к шине

5 питания 9, а эмиттер р — п-р транзистора 6 — к шине питания — записи 10. Входная шина 7 служит для адресной выборки при считывании, а шина 8 — для. управления поразрядной выборки лри записи. Шины питания 8 и 10 подключены к общему источнику постоянного нитряжания (М в), причем шина 9 предназначена для работы коммутатора в режиме счнтивакия и хранения ннформаЦии, а пижама 10 — в режима записи информЩин с иосладующим отключением, сто снижает потреб- >5 ляемую разрядом мощность. В соответствии с укаэанными вьппа режимами работы, транзисто. ры 2, 6 выполнены более мощньпчи по сравнению с транзисторами 1, 5. Разряд коммутатора предусматривает работу и режима записи и считывания информации в запоминающую матрицу.

Режим записи информации предусматривает иодачу тока питания по обеим шинам питания разряда коммутатора 9 и 10. На. Входную шину 7 лоступает сигнал логического нуля. Ток, икжектиру-25 емый р-п-р траизистором 5, пощщает иа базовый вывод и — р-и транзистора 1 и замыкается через птииу, на которую нриходит сигнал логический "б". Транзистор 1 закрывается и иа работу,правого канзла разряда селектора Влияиия не ,оказывает. Правый канал салжтора может иахо.двться в двух состояниях: в иавибрвином, когда иа шипу 8 щщходит сигнал логический "О", и В Выбраеном! когда ио ВХОДИОЙ юииа 7 ДОЙ«.

САЯТ сигнал логическая 1 ° Пусть к входной шике приложен сигнал логический "О", тогда праВый какал работаат аиалогичею BOSo и режиме записи. Ток от источиика через щииу N поступает на 3MHTTep p — и — р rpBR5fcTOpe б и, иижактируемый пм, попадает иа базовый вывод транзистора 2, а далее замыкается по шина 8 на шину нулевого потенияала. Транзистор 2 оказывается мпартым, так как отсутствует ток через база-эмиттврный переход, и по выходу уста-. навливается сигнал логической едннниьт. Пусть к входной тпина 8 приложен сигнал логическая

"1". Ток, инжектируемый транзистором 6, попадает на базовый вывод транзистора 2, отпирает переход база-эмиттер и включает его в проводя42 4 шее состояние. На выходной шине 3 устанавливается сигнал логический "0" н транэистор 2 пропускает значительные втекающие токи (ток программирования) по выходу на шину нулевого потенциала. Режим считывания характеризуется нахождением в рабочем состоянии менее мощного левого канала разряда коммутатора, который конструктивно выполнек на транзисторах, расчитанных на низкие уровни рабочих токов, тогда как правый канал расчитан на пропускание больших токов пережигания плавких перемычек запоминающих элементов матрицы. Правый канал разряда коммутатора в режиме считывания обесточивается шина 10 подсоединяется к шине нулевого потенциала, чем осуществляется снижение общего тока потреблении разрядом коммутатора.

Транзисторы 2 и 6 заперты и на работу левого канала влияния не оказывают. Шина 9 подсоединяется к источнику питания, и ток or источника

Ф

3 1 инжектируемый транзистором 5, попадает на базовый вывод транзистора 1, объединенный с входной шиной. Сигнал логического куля по входной шине 7 обеспечивает запертое состояние транзистора 1 и логическую "1" по выходкой . шине 3. Сигнал логической "1" ко входной шине 7 обеспечивает протекание безового тока транзистора 1 и включащаа ато в проводящее состояние с установкой логического "О" по выходной шине 3. Иапичиа сигнала логический "О" на шине

3 разрыв определяет сосникне выборки. формула изобретения

Коммутатор содаржащнй и каждом разряде два и-р — п транзистора, эмиттары и коллекторы которых объединены между собой, при этом коллекторы соединены с выходом коммутатора, о тл ичаютпийся там, что, с целью снижения потребляемого тока и напряжения питашщ, в каждый разряд дополнительно введены два ннжектирующих р-rr p транзистора, коллекторы которых объединены с базамн соответствующих и-р-и транзисторов и подключены к соответствующим входам. коммутатора, эмиттеры р — л-р транзисторов соединены с соответствующими ппшами питания, базы р — п-р транзисторов объединены и присоединены к объединенным эмиттерам п-р — п транзисторов и к шине нулевого потенциала.

684742

Составитель Г. Кутний

Редактор А. Шмелъкин Техред М.Келемеш Корректор О. Билак

Заказ 5306/54

Тираж 1060 Подписное

UHHHflH Государственного комитета СССР по делам изобретений и открытий

113035, Moncsa, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4