Устройство для преобразования кодов

Иллюстрации

Показать всеРеферат

Союз Сове

Социалистических

Республик (61) Дополнительное к авт. свид-ву М 594592 (22) ЗаЯвлено 05.12.77 (21) 2549832/18-09 (Gl)M. Кд.

Н 04 1 3/02 с присоединением заявки М—

ГааударатваннМ наинтат

СССР аа делам нзабретаннй и атнритнй (23) Приоритет—

Опубликовано 05.09.79. Бюллетень М 33

Дата опубликования описания 15.09.79 (53) УДК 621.394, .14 (088.8) Б. А. Морозов, А. C. Просалков, С. Ф. Степанюк и A. Ф. Черняков (72) Авторы изобретения (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ КОДОВ

Изобретение относится к телеграфной связи и предназначено для использования в системах обмена информацией между устройствами, использующими пяти- н семизлементные межлународные коды.

По основноиу авт. св. N 594592 известно устройство для преобразования кодов, содержащее датчик команд дешифратор и последовательно соединенныекоммутатор, шифратор и согласующий блок, первый выход которого подключен к

1О первому входу датчика команд, выходы которого соединены соответственно с вторым входом согласуюшего блока и первым входом дешифратора, выход которого подключен к второму входу шифратора, накопитель н последовательно соединенные анализатор и формирователь символов выход которого подключен к третьему входу шифратора, второй вход которого соединен с управляющим входом анализатора, второй и третий выходы которого подключены соответственно к входу коммутатора и второму входу датчика команд, дополнительные выходы которого соединены с входами анализатора и накопителя, выход которого подключен к второму входу шиф- . ратора, а второй выход согласующего блока соединен с дополнительным входом накопителя (1).

Однако в известном устройстве недостаточна точность преобразования.

Цель изобретения — повышение точности преобразования кодов при многоканальной передаче.

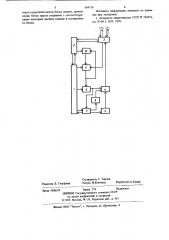

Для этого в устройство для преобразования кодов, содержащее датчик команд, дешифратор и последовательно соединенные коммутатор, шифратор и согласующий блок, первый выход которого подключен к первому входу датчика команд, выходы которого соединены соответственно с вторым входом согласующего блока и первым входом дешифратора, выход которого подключен к второму входу шифратора, накопитель и последовательно соединенные анализатор и формирователь символов, выход которого подключан к третьему входу шифратора, второй вход которого соединен с управляющим входом анализатора, второй и третий выходы которого подключены соответственно к входу коммутато. ра и второму входу датчика команд, дополнительные выходы которого соединены с входами ана3 684754 4 лизатора и накопителя, выход которого подклю- ние с выхода анализатора 7, он распределяет пречен к второму входу шифратора, а второй выход образованные символы по регистрам. С выхода согласующего блока соедичен с дополнительным . шифратора 4 информация поступает в согласуювходом накопителя, введены блок памяти и блок щий блок 5. Получив команду от датчика коадреса, выходы которого соединены с соответст- 5 манд 1, блок адреса 9 обеспечивает вывод преобвующими входами датчика команд, согласующе- разованного символа или группы символов в исго блока и блока памяти, другой вход которого ходящий канал с обслуживаемым адресом. По соединен с выходом накопителя, к дополнитель- завершении процесса преобразования исходной ному входу которого подключен выход блока последовательности датчик команд 1 дает сигнал памяти, причем входы блока адреса соешп|ены 10 стирания в накопитель 6. с соответствующими выходами датчика команд Если проверка в анализаторе 7 определила и согласующего блока. отсутствие эквивалентности информационной поНа чертеже изображена структурная электри- следовательности в накопителе 6 символу или ческы схема предложенного устройства. группе символов другого кода, то первый симУстройство содержит датчик команд 1, дешиф- 15 вол из накопителя 6 поступает в дешифратор 2 ратор 2, коммутатор 3, шифратор 4, согласую- и с его выхода непосредственно па вход шифращий блок 5, накопитель 6, анализатор 7, форми- тора 4 и анализатора 7. Получая команды с вырователь символов 8, блок адреса 9 и блок памя- хода анализатора 7, коммутатор 3 управляет ти 10. процессом преобразования 1-ro символа на шифУстройство работает следующим образом. N раторе 4. Если рассматриваемый символ отсутИнформациоиный символ в коде, требующий ствует в алфавите кода, в который он преобрапреобразования, поступает но входящему кана- зуется, то формирователь символов 8, получив лу в согласующий блок 5. Согласующий блок 5 управления с анализатора 7, обеспечивает генеобеспечивает прием входящего символа и по рацию соответствующей эквивалентности этому окончании-процесса его накопления выдает в 25 символу последовательности в преобразованном блок адреса 9 сигнал, указывающий наличие ин- коде. С выхода шифратора 4 символ или группа формационного символа для обработки и адрес символов поступает в согласующий блок 5. Покапала, по которому он поступил. Блок адреса лу-ив команду от датчика команд 1, блок.адре9 фиксирует адрес обслуяаваемого капала и вы- са 9 обеспечивает вывод преобразованного симдает в датппс команд 1 требование на преобра- вола или группы символов s исходящий канал

ЭО зование кода и на вид преобразования для дан-. c обслуживаемым адресом. По завершении процесса преобразования символа датчик команд 1

По команде блока адреса 9 в блок памяти 10 дает в накопитель 6 команду на стирание, 1-го из ячеек памяти, закрепленных за обслуживае- преобразованного символа и вывод последовамым каналом, в йакотппель 6 емкости и симво- з5 тельности из (n — 1) оставшегося символа в лов считывается информационная последователь- блок памяти 10. Команду на запись в блок памяность, состоящая из n-ro символа. На место и-го ти 10 в ячейки, закрепленные за.обслуживаемым символа записывается вновь нритпедший символ каналом, выдает блок адреса 9, получая управлеиз согласующего блока 5. Емкость накопителя ние от датчика команд 1.

6 выбирается исходя из количества символов в Запоминание, сравнение, смена и формировапоследовательности, которая составляется из их ние регистров преобразуемых кодов осуществлямаловероятиого сочетания и является зкв щален. ется анализатором 7, управляющим коммутатотом символа или группы символов другого ко- ром 3 и формирователем символов 8, Зако>гшв процесс преобразования кода, устПри полном заполнении накопителя 6 ипфор- 5 ройство для преобразования кодов готово переимация посимвольно с 1-ro no r-ый поступает в ти к обслуживанию другого канала, по которому дешифратор 2, и с выхода дешифратора 2 посту- завершен тп>ием символа. паст в анализатор 7. В анализаторе 7 производитФормула изобретения ся проверка: является ли накопленная последовательность эквивалентом ствола или гругпты

Устроиство для преобразования кодов по символов другого кода. Если в результате про- авт. св. И 594592, отл ич а1о щ е е с я тем, / верки установлено наличие эквивалентности, то что, с целью повышения точности преобразовас выхода анализатора 7 в формирователь, сим- ния кодов при многоканальной передаче, введеволов 8 поступает команда на генерирование ны блок памяти и блок адреса, выходы кото55 символа или группы символов в преобразованном рого соединены с соответствующими входами коде, поступающих с выхода формирователя сим- датчика команд, согласующего блока и блока волов 8 на вход шифратора 4. Работу шифрато- памяти, другой вход которого соединен с выРа 4 определяет коммутатор 3, Получая управле- ходом накопителя, к дополнительному входу ко684754

Составитель Г. Серова

Редактор Л. Гельфман Техред М.Келемеш Корректор О, Билак

Заказ 5306/54 Тираж 775 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушекая наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. проектная, 4 торого подключен выход блока памяти, причем входы блока адреса соединены с соответствующими выходами датчика команд и согласующего блока, 6

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР и 594592, кл. Н 04 L 3/02, 1976.