Устройство для восстановления промежуточной строки телевизионного изображения

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВ ИВЛЬСТВУ

Союа Советскиа

Социалистических

Республик (ii) 684781 (61) Дополнительное к авт. санд-ву (22) Заявлено 09.1 3.77 (21) 2541543/18-09 с присоединением аалвкн 89 (23) Приоритет (51)М, Кл.

H 04 И 5/44

Н 04 N 9/58

ГосулйрстВФннмл Воняет

СССР по лФяйн нзюб мтйинй н открытнй (53) УДК621. 397 (088. 8) Опублнковано05.09.79 Ьоллетень М ЗЗ

Дата о у опнсаннл 050$79 (72) Автор изобретения

О.В. Украинский

Ленинградский электротехнический институт связи им. проф. M.А. Бонч-Бруевича (71) Заявитель

Изобретение относится к радиотехнике и может использоваться в прикладном телевидении.

Известно устройство для восстановления промежуточной строки телевизионного (ТВ) иэображения, содержащее.две линии задержки, два дифференцирующих блока, два источника постоянного тока, два интегратора, элемент И (1), Однако в известном устройстве сигнал восстанавливаемый строки формируется в результате большого количества последовательно производимых операций: дифференцирования, суммирования, интегрирования и еще раэ суммирования, в результате чего возникают искажения.

Целью изобретения является повышение точности восстановления амплитудных соотношений промежуточной строки ТВ изображения.

Для этого в устройство для восстановления промежуточной строки ТВ иэображения, содержащее две линии задержки, два дифференцирующих блока, два источника постоянного тока, два интегратора, элемент И, введены два вычитающих блока, блок сравнения, нуль-орган, триггер, два коммутатора, при этом сигналы первой и второй строки телевизионного иэображения поданы соответственно на первый и второй входы первого вычитающего блока и на вход первой и второй линий задержки, выход первой линии задержки соединен с первым входом второго вычитающего блока и с первым входом первого коммутатора, выход второй линии задержки соединен с вторым входом второго вычитающего блока и с вторым входом первого коммутатора, причем выход первого вычитающего блока через первый источник постоянного тока и первый интегратор соединен с первым входом блока сравнения, а выход второго вычитающего блока череэ второй источник постоянного тока и второй интегратор подключен х второму входу блока. сравнения, выход которого подключен к первому входу триггера, первый и второй выходы которого подключены соответственно к первому и второму входу второго коммутатора, выход второго вычитающего блока через нуль-орган подключен к второму входу триггера, к пер30 (54) УСТРОИСТВО ДЛЯ ВОССТАНОВЛЕНИЯ ПРОМЕЖУТОЧНОЯ

СТРОКИ ТЕЛЕВИЗИОННОГО ИЗОБРАЖЕНИЯ

684781 ному входу элемента и и к входу первого дифференцирующего блока, выход которого соединен с первым управляющим входом второго коммутатора, второй управляющий вход которого соединен с выходом элемента И, второй вход которого через второй дифференцирующий блок соединен с вторым выходом первой линии задержки, а выход второго коммутатора подключен к управляющему входу первого коммутатора.

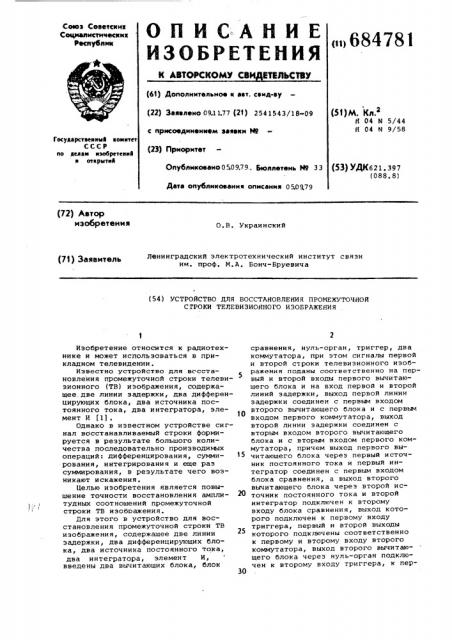

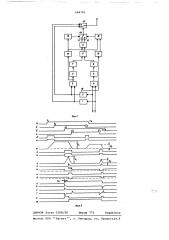

На фиг. 1 приведена структурная электрическая схема предложенного устройства, на фиг. 2 — диаграммы его работы.

Устройство для восстановления промежуточной строки ТВ изо(ражения содержит две линии задержки (ЛЗ) 1, 2, два вычитающих блока 3, 4, два источника 5, 6 постоянного тока, два интегратора 7, 8, блок сравнения 9, нуль-орган 10, триггер 11, два дифференцирующих блока 12, 13, два коюеаутатора 14, 15, элемент и

16. Яа схеме обозначены выходные плечи 17, 18 триггера 11, отвод

19 ЛЗ 2.

Устройство работает следующим образом.

Видеосигналы ТВ строК, подЛежащие обработке с целью восстанонления промежуточной строки и представляющие собой перепады яркости (фиг. 2а, б) одновременно поступают на вычктающий блок 4 и на ЛЗ 1, 2.

С выходов ЛЗ 2, 1 сигналы, задержанные относительно входных на время

= Т (фиг. 2s г), поступают на вычитающий блок 3 и коммутатор 15.

В случае, если в одном из входных сигналов имеется перепад яркости (момент времени и, фиг. 2а), сигнал на выходе вычйтающего блока

4 (фиг. 2д) скачком увеличивается, превышая некоторую пороговую величину, и включает источник б, который заряжает постоянииа током (фиг. 2е) интегратор 8, с выхода которого сигнал (фиг. 2ж) поступает на один вход блока сравнения 9, при этом, чем больше промежуток времени (12 11 ) (т4 t3 ) в течение кОтОрОгО сигналы входных строк (фиг. 2а,б) отличаются, тем большее напряжение накаплинается на выходе интегратора

8 (U > U>). Сигнал с выхода вычитаюt щего блока 3 (фиг. 2з) включает источник 5, с выхода которого сигнал (фиг. 2и) поступает на интегратор 7 и далее (фиг. 2к) — на другой вход блока сравнения 9. Однако источник

5 заряжает интегратор 7 вдвое быстрее чем источник 6 — интегратор 8.

I !

Поэтому за нремя t2 — t (см. Фиг.2н, г) на выходе интегратора 7 накапливается вдвое большее напряжение, чем на выходе интегратора 8 за время t -t то есть напряжение на выхоФ де интегратора 7 достигает уровня напряжения на выходе интегратора 8 эа время, равное t ее — 2 — . Следоt - t нательно, импульс на выходе блока

)сравнения 9 (фиг, 2л) появляется в

5 i с1 момент нременн, ревнмв М,т

В момент появления импульса (фиг. 2л) интеграторы 7, 8 начинают разряжаться через входную цепь блока сравнения 9, )0 Процесс разрядки продолжается до конца промежутка времени - (или

1 -t ). По окончании процесса разрядс 2 кй напряжения на выходах интеграторов 7, 8 равны нулю, и схема готова к следующему циклу работы.

Сигнал восстановленной промежуточной строки формируется с помощью коммутатора 15, коммутирующего сигналы с выходов ЛЗ 2, 1 (фиг. 2в,г).

20 Исходным положением коммутатора 15 является нижнее по схеме фиг. 1 положение, когда на выход устройства проходит сигнал фиг. 2н. Управляется коммутатор 15 сигналом с выхода

25 коммутатора 14, на входы которого сигналы поступают с выходных плеч

17, 18 триггера 11. При этом в отсутстние сигнала с выхода коммутатора 14 коммутатор 15 занимает иск» ходное положение, при наличии этого сигнала коммутатор 15 занимает верхнее по схеме положение. Коммутатор

14 управляется сигналами с выходов дифференцирующего блока 13 и элемента И 16, при этом сигналом с вы35 хода дифференцирующего блока 13 коммутатор 14 устанавливается в исходное (левое по схеме фиг ° 1) положение, сигналом с выхода элемента

И 16 — н правое.

40 В случае, когда перепад яркости встречается сначала н сигнале фиг. 2б (участок -t4) коммутатор

15 при появлении этого перепада не меняет своего исходного положения, 45 то есть на входы коммутатора 14 и триггера 11 поступает сигнал с выхода нуль-органа 10 (фиге 2м), на выходном плече 17 триггера 11 сигнал отсутствует (исходное положение

50 триггера 11), следовательно, отсутствует управляющий сигнал и на выходе коммутатора 14. Исходное положение ком4утатор 15 сохраняет до середины промежутка времени

t4-t то есть до прихода импульса

3 с блока сравнения 9, с приходом которого на выходном плече 17 триггера ll появляется сигнал (фиг. 2н), и коммутатор 15 меняет свое исходное положение на верхнее. При появлении перепада яркости и во второй

t строке (момент времени tg фиг. 2в) сигналы фиг. 2н,г уравниваются, и появившийся сигнал от нуль-органа

10 (фиге 2м), устанавливая триггер

65 11 н исходное положение, устананли684781

45 вает в исходное положение также и коммутатор 15.

В том случае, когда перепад яркости встречается сначала в строке фиг. 2а (участок, - ) работа коммутатора 15 происходит следующим образом: в первую половину промежутка времени t, -t> коммутатор 15 на-! l ходится в верхнем положении, а во вторую — в нижнем, исходном, Это достигается тем, что сигнал, управляющий работой коммутатора 15, на время t -t снимается с плеча 18 триггера 11 (фиг. 2о) в результате изменения положения коммутатора 14, управляемого элементом И 16. При этом с отвода 19 J13 2 сигнал (фиг. 2п), задержанный относительно входного сигнала (фиг. 2а) на время Т-t через дифференцирующий блок 12 поступает на один вход (фиг. 2р) элемента И 16, на другой вход которого поступает сигнал от нуль-органа 10.

Время задержки уменьшено на время t, необходимое для компенсации инерционности коммутаторов 14, 15.

Таким образом, элемент И 16 посылает управляющий импульс (фиг. 2с), изменяющий положение коммутатора 14 только в том случае, когда перепад яркости встречается сначала в сигнале фиг. 2а. Управляющий коммутатор 14, сработавший от импульса с элемента И 16 (фиг. 2с), возвращается в исходное положение положительным импульсом (фиг. 2т) сигнала с дифференцирующего блока 13, появляющимся при уравнении сигналов фиг. 2в,г. На фиг. 2у показан сигнал, управляющий коммутатором 15 на фиг. 2ф — сигнал восстановленной промежуточной строки.

Формула и зобре тени я

Устройство для восстановления промежуточной строки телевизионного изображения, содержащее две линии задержки, два дифференцирующих бло5

40 ка, два источника постоянного тока, два интегратора, элемент И, о тл и ч а ю щ е е с я тем, что, с целью повышения точности восстановления амплитудных соотношений промежуточной строки телевизионного изображения, введены два вычитающих блока, блок сравнения; нуль-орган, триггер, два коммутатора, при этом сигналы первой и второй строки телевизионного иэображения поданы соответственно на первый и второй входы первого вычитающего блока и на вход первоЯ и второй линий задержки, выход первой линии задержки соединен с первым входом второго вычитающего блока и с первым входом первого коммутатора, выход второй линии задержки соединен с вторым входом второго вычитающего блока и с вторым входом первого коммутатора, причем выход первого вычитающего блока через первыЯ источник постоянного тока и первый интегратор соединен с первым входом блока сравнения, а выход второго вычитающего блока через второй источник постоянного тока и второй интегратор подключен к второму входу блока сравнения, выход которого подключен к первому входу триггера, первый и второй выходы которого подключены соответственно к первому и второму входу второго коммутатора, выход второго вычитающего блока через нуль-орган подключен к второму входу триггера, к первому входу элемента И и к входу первого дифференцируюшего блока, выход которого соединен с первым управляющим входом второго коммутатора, второЯ управляющий вход которого соединен с выходом элемента И, второЯ вход которого через второй дифференцирующий блок соединен с вторым выходом первой линии задержки, а выход второго коммутатора подключен к управляющему входу первого коммутатора, Источники информации, принятые во внимание при экспертизе

1. Патент Великобритании 9 966319, Н 4 F, 1964.

684781

Ф с

I с

Э и о

Р

Р с

Уис. Х

ЦНИИПИ Заказ 5308/56 Тираж 775 Подпи сн ое

Филиал ППП Патент, r. Ужгород, ул. Проектная,4