Множительно-делительное устройство

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ 686036

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. сеид-ву (22) Заявлено 140478 (21) 2605176/18-24 (51)М. КЛ. с присоединением заявки М— (23) Приоритет—

G 06 G 7/16

Государстаекоый ком ктат

СССР по делам изобретеямй н открытой

Опубликовано 1М9.79. Бюллетень ИУ 34

Дата опубликования описания 1809.79 (53) УДК а81. З 5 (088.8) (72) Авторы изобретения

Л.Ф. Березин и A Ë. Якимаха

{71) Заявитейь Всесоюзный научно-исследовательский институт аналитического приборостроения (54 j ИНОЕИТЕЛЬНО-,ЦЕЛИТЕЛЬНОЕ УСТРОЙСТВО

Изобретение относится к области аналоговой вычислительной техники и автоматики и может быть использовано для выполнения операций умиожеиин и деления в аналоговых вычислитель- ных устройствах.

Известны множительные и делительиые устройства, содержащие два операционных усилителя, два полевых транзистора и резисторы (11.

Недостатком таких устройств является наличие двух полевых транзисторов со строго идентичныьщ характеристиками и двух операционных усилителей, что обусловливает снижение точности в работе.

Наиболее близким техническим решением к данному изобретению является множительно-делительное устройство (2), содержащее два операционных усилителя, четыре ключа, полевой транзистор, два запоминающих конденсатора, повторитель и тактирующий генератор.

Недостатком этого устройства является его сложность и невысокая точность.

Цель изобретения — упрощение устройства и повьааение точности устройства.

Для этого в устройстве содержащем генератор тактовых импульсов, первый, второй и третий двухиозицион. ные ключи делительный элемент вы полненный на полевом транзисторе, сток которого соединен с выходом второго ключа, а затвор с выходом третьего ключа и первьм запоминающим конденсатором, операционный уси10 литель, вход которого связан с входным масштабным резистором, а выходсо входом третьего двухпозиционного ключа, повторитель, вход которого связан с выходом третьего ключа и вторьм запоминающим конденсатором, а выход является выходом устройства, управляющие входы всех ключей подключены к выходу генератора тактовых импульсов, один вход первого двухпоэиционного ключа является входом устройства, второй вход подключен к выходу повторителя, а выход через входной масштабный резистор подключен ко входу операционного усилителя и к истоку полевого транзистора, выход операционного усилителя подключен ко входу третьего дв ухпозиционного ключа.

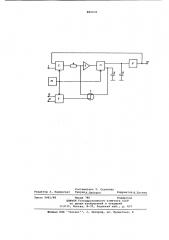

На чертеже приведена схема предложенного устройства.

686036

Устройство содержит первый вход

1 устройства перный двухпоэицион—

/ ный ключ 2, операционный усилитель

3, входной масштабный резистор 4, второй двухпозиционный ключ 5, первый запоминающий конденсатор 6, полевой транзистор 7, второй запоминающий конденсатор 8, повторитель 9, выхоц устройства 10, третий двухпозиционный ключ 11, второй и третий нходы устройстна 12 и 1 3, генератор тактовых импульсов 14.

Первый вход 1 устройства связан со входом первого днухпозиционного ключа 2, выход которого соединен со входом операционного усилителя 3 через резистор 4. Выход операционного усилителя 3 соединен со входом третьего двухпозиционного ключа 11, один выход которого соединен с первьм запоминающим конденсатором 6 и затвором полевого транзистора 7, а другой выход соединен со вторым запоминающим конденсатором 8 и входом повторителя 9. Выход повторителя 9

cîåäèíåí с выходом ключа 2. Сток полевого транзистора 7 связан с выходом днухпозиционного ключа 5, исток связан со входом усилителя 3. Второй и третий входы устройства 12, 13 связаны со входами второго днухпозиционного ключа 5. Управляющие входы всех ключей подключены к выходу генератора 14.

Устройство выполняет операцию умножения деления эа дна такта работы.

В первом такте первый двухпоэицнонный ключ 2 соедичяет первый вход

1 устройства со входом операционного усилителя 3 через резистор 4, а третий двухпозиционный ключ 11 соединяет выход усилителя 3 с затвором транзистора 7 и первым запоминающим конденсатором 6. Ключ 5 соединяет второй вход 12 устройства со стоком транзистора 7. Сопротивление стокисток транзистора 7 при этом равно

R =- — " -R

П 1 ) где U — напряжение на первом входе устройства, U — напряжение на втором входе устройства, R — величина резистора 4.

Во 5 соединяет третий вход 13 устройства через транзистор 7 со входом операционного Усилителя 3. Ключ 11 соединяет выход операционного усилителя 3 со входом повторителя 9 и запоминающим конденсатором 8. Ключ 2 соединяет выход повторителя 9 со входом операционного усилителя 3 через резистор 4.

Напряжение на выходе повторителя и выходе устройства будет равно 1 Ul ° U5 в и. где U — напряжение на третьем вхо5 де устройства.

Затем следует снова первый такт, в течение которого ключ 11 отключает конденсатор 8, а на выходе повторителя 9 остается напряжение за счет

10 сохранения напряжения на конденсаторе 8. В обоих тактах работы устройстна напряжение между истоком и затвором сохраняется постоянным с помощью конденсатора 6, что обеспечивает постоянное сопротивление сток-исток транзистора 7.

Предлагаемое устройство проще прототипа, так как позволяет исключить один операционный усилитель, один ключ и резистор. Устройство обладает большей точностью в работе за счет исключения погрешности втоpoго операционного усилителя.

Формула изобретения

Множительно-делительное устройство, содержащее генератор тактовых импульсов, первый, второй и третий двухпозиционные ключи„ делительный элемент, выполненный на полевом транзисторе, сток которого соединен с выходом второго ключа, а затвор с выходом третьего ключа и первым запоминающим конденсатором, операционный усилитель, вход которого связан с входным масштабным резистором, а выход — со входом третьего двухпозиционного ключа, повторитель, вход которого снязан с выходом третьего ключа и вторым запоминающим конденсатором, а выход является выходом

40 устройства, управляющие входы всех ключей подключены к выходу генератора тактовых импульсов, о т л и ч а ю щ е е с я тем, что, с целью упрощения и повышения точности, 45 один вход первого двухпоэиционного ключа является входом устройства, второй вход подключен к выходу повторителя, а выход через входной масштабный резистор подключен ко входу операционного усилителя и к истоку полевого транзистора, выход операционного усилителя подключен к входу третьего днухпээиционного ключа . у Источники информации, принятые во внимание при экспертизе

1 . Шор Б. Малогабаритное аналоговое вычислительное устройство для деления и умножения, журнал Электроника, 1967, У 26, с. 12.

2. Авторское свидетельство СССР

9 444201, кл. 06 7/16, 1964 (npozoтип}.

6860 3б

Тираж 780 Подписное

ЦНЙИПИ Государственного комитета СССР по делам изобретений и открытий

11 30 35, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 5461/48

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

Составитель Т. Саупнова

Редактор Н. Каменская Техред И. цабурка Корректор В.сутяга