Итегратор

Иллюстрации

Показать всеРеферат

Своз Советских

Социалистических

Республик

cia>686037 (61) Дополнительное к авт. свид-ву (22) Залвлено 160276 Pl) 2323554/18-09 с присоединением заявки Ио (23) Приоритет

Опубликовано 15.09.79. Бюллетень Ио 3 4

Дата опубликования описании 1 5.09.79 (51)М. Кл.2

G 06 С 7/18

Государственный комитет

СССР яо делан изобретений и открытий (53) УДК 621. 502

{088.8) (72) Автори

ИЗО6РФТВНИЯ

Н.А. Козвонин и В. Г. Лебедев (71) 3 »l4 6» Куйбыаевский электротехнический институт связи (5 4) ИНТЕГРАТОР

Изобретение относится к радиотехнике и может использоваться в устройствах автоматики, вычислительной и электроиэмерительной технике.

Известен интегратор, содержащий операционный усилитель, вход последнего через первый ключ соединен с источником сигнала, интегрирующий конденсатор, первый вывод которого соединен с входом операционного усилителя непосредственно, а второй вывод через второй ключ — с выходом операционного усилителя, а также третий ключ, включенный между входом и выходом операционного усилителя (1) .

Однако известный интегратор не обеспечивает полную компенсацию дрейфа нуля на выходе.

Цель изобретения — компенсация дрейфа нуля, Для этого в интеграторе, содержащем операционный усилитель, вход последнего через первый ключ соединен с источником сигнала, интегрирующий

25 конденсатор, первый вывод которого соединен с входом операционного усилителя непосредственно, а второй вывод через второй ключ — с выходом операционного усилителя, а также третий ключ, включенный между входом и выходом операционного усилителя, между общей шиной и вторьм выводом интегрирующего конденсатора введен четвертый ключ.

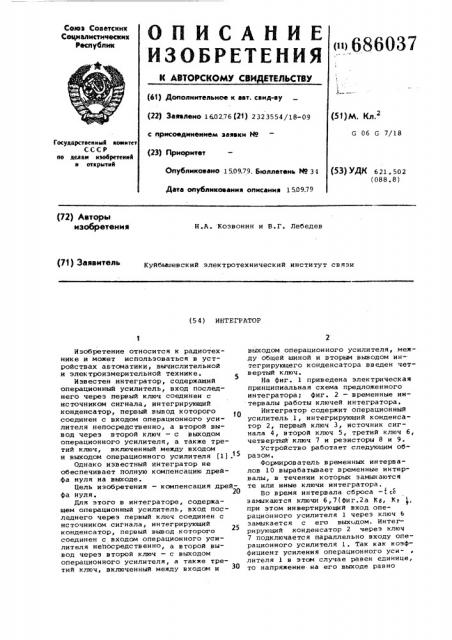

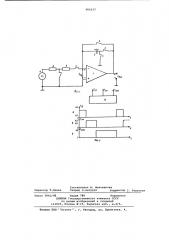

На фиг. 1 приведена электрическая принципиальная схема предложенного интегратора; фиг. 2 — временные интервалы работы ключей интегратора.

Интегратор содержит операционный усилитель 1, интегрирующий конденсатор 2, первый ключ 3, источник сигнала 4, второй ключ 5, третий ключ б, четвертый ключ 7 и резисторы 8 и 9. устройство работает следующим образом.

Формирователь временных интервалов 10 вырабатывает временные интервалы, в течении которых замыкаются те или иные ключи интегратора.

Во время интервала сброса -1 с5 заикаются ключи 6,7(фиг.2а k6, Кт при этом инвертирующий вход операционного усилителя 1 через ключ 6 замыкается с его выходом. Интегрирующий конденсатор 2 череэ ключ

7 подключается параллельно входу операционного усилителя 1. Так как коэффициент усиления операционного усилителя 1 в этом случае равен единице, то напряжение на его выходе равно

686037 формула изобретения

Источники информации, принятые во внимание при экспертизе ц Ус р где е

К вЂ” коэффициент усиления операцион- 1 „Патент. Японии 948-15588 ного усилителя 1, напряжение смеще- д 97/8/ В 2 << ° 06 < "/00 напряжению смещения нуля инвертирующего входа Бсм +, . Интегрирующий конденсатор,2 заряжается до уровня напряжения смещения нуля инвертирую- . щего входа — усм . Разомкнутый ключ 3 исключает попадание тока ис- 5 точника сигнала 4 на вход операционного усилителя 1.

Во время интервала интегрирования (ttt>) следующего за интервалом сброса (t t„(t ). замыкаются ключи 3,5 1() (фиг. 2, h К у К y ), при этом интегрирующий конденсатор 2 подключается через ключ 5 между входом и выходом операционного усилителя 1, а источник сигнала 4 через резисторы 8,9 и ключ 3 подключается на его вход.

Происходит интегрирование тока источника сигнала 4, однако в выходном напряжении операционного усилителя 1 отсутствует напряжение смещения нуля (U см-) .

Это происходит потому„что напряжение источника питания равно нулю (источник закорочен) . 1огда выходное напряжение операционного усилителя 1 в интервале интегрирования (tU< ) равно нулю, так как интегрирующий конденсатор 2, заряженный до уровня напряжения смещения нуля (1)см,}, подключается к входу операционного усилителя 1 через его выход, в результате чего в первый момент интегрирования к входу операционного усилителя 1 прикладывается двойное напряжение смещения нуля (2 UcM о) что приводит к тому, что выходное напря- Ç5 жение операционного усилителя 1 станет равным нулю, т.е. напряжение р 6, на выходе операционного усилителя 1, вызванное смещением нуля входа (UcM g равно 4О ния нуля Бвых на выходе операционного усилителя 1 компенсируется схемой таким образом, что в интервале интегрирования (tu„) оно в К-раз меньше существующего значения смещения нуля на его входе (UcM <).

Во время интервала запоминания (t3a ) замыкается ключ 5 (фиг. 2 в, Кк), в результате чего ток источника питания 4 отключается от входа, а выходное напряжение операционного усилителя 1 сохраняет значение, соответствующее концу интервала интегрирования (tg <) .

В предлагаемом интеграторе отсутствуют специальный запоминающий конденсатор, а функции его совмещены с функциями интегрирующего конденсатора, что дополнительно упрощает устройство.

Интегратор, содержащий операционный усилитель, вход последнего через первый ключ соединен с источником сигнала, интегрирующий конденсатор, первый вывод которого соединен с входом операционного усилитепя непосредственно, а второй через второй ключ - с выходом операционного усилителя, а также третий ключ, включенный между входом и выходом операционного усилителя, о т л и ч а ю щ и йс я тем, что, с целью компенсации дрейфа нуля, между общей шиной и вторым выводом интегрирующего конденсатора введен четвертый ключ.

68 6037

Составитель А. меньшикова

Техред Н.Бабурка Корректор Г. Решетник

Редактор Т.Янова

Филиал ППП Патент, г. ужгород, ул. Проектная, 4.

Заказ 5461/48 Тираж 780 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва Ж-35, Раушская наб., д.4/5.