Устройство для вычисления свертки функций

Иллюстрации

Показать всеРеферат

Союз Советским

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕтЕНИЯ "" 686ОЗ8 (61} Дополнительное к авт. сеид-ау (22) Заявлено 260577(21) 2490260/18-24 (Sf)N. Kn. с присоединением заявки 89 (23) Приоритет а ова 7/19

Гееудщктаеимый комитет

СССР яа делам нэобретееня

6I @тадмткя

Опубликовано 150979. Бюллетень 89 34

Дата опубликования описание 1 509,79 (53) УДК 681.335.8 (088. 8) В.Г. Осипенко, A ° Â. Мулеванов, В.Н. Тимофеев и М.Е.Бочарова (71} Заявитель

Таганрогский радиотехнический институт нм. В.Д.Калмыкова (54) устРОЙстВО для Вычисления сВеРтки Функций

Изобретение относится к области дискретно-аналоговой специализированной вычислительной техники и может быть использовано в радиотехнике, электросвязи и измерительной технике для вычисления свертки функций.

Кроме того, оно может быть использовано в радиолокационных и гидроакустических устройствах и системах связи для обнаружения, обработки и опознавания сигналов и при исследовании систем автоматического регулирования.

Известно устройство для вычисления свертки функций (1), в котором для создания обратного хода времени в од- 15 ной из свертываемых функций используется считывание Функции с графиков или магнитной ленты с замедлением.

Наиболее близким техническим pemeнием к данному изобретению является 20 устройство для вычисления свертки

Функций (2j содержащее блок управления, первый выход которого соединен со входом генератора импульсов, и линию задержки, состоящую из последовательно соединенных ячеек памяти, выход каждой из которых соединен со входом последующей ячейки памяти и первым входом соответствукщего блока умножения.

Недостаткам известных устройств является низкая точность вычислений и ограниченный частотой диапазон.

Целью изобретения является повышение точности и быстродействия устройства.

Это достигается тем, что предлагаемое устройство содержит распределитель, сумматор, блок пр еобразования частоты, масштабный блок и блоки памяти по числу блоков умножения, входы всех блоков памяти соединены с первьм вхОдом масштабного блока, второй выход которого соединен со входом первой ячейки памяти линии задержки, третий выход — с первым входом блока преобразования частоты, а его вход является входом устройства, управляющий вход каждого блока памяти соединен с выходом распределителя, управляющий вход каждой ячейки памяти линии задержки соединен с выходом генератора импульсов, дополнительный выход которого соединен со входом распределителя ° выход каждого блока памяти соединен со вторьм входом соответствукщего блока умножения, выход которого подключен ко входу сумматора, дополнительный вход масштабного блока соединен со вторыми выхо686038 дом блока управления, в торой вход блока преобразования частоты соединен с выходом сумматора, à егo выход явл яетс я выходом устройства .

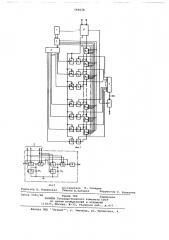

На Фиг. 1 приведена схема предлагаемого ус тройства; на фиг. 2 — схема 5 ячейки памяти.

Устройство для вычисления свертки Функций содержит блок управления 1, первый выход которого соединен со входом генератора импуль- )О сов 2, линию задержки 3, состоящую из послецовательно соединенных ячеек памяти 4 — 4, выход каждой иэ которых сое;инеи со входом последующей ячейки памяти и первым входом соответствующего блока умножения 5, — 5р.

Кроме того, устройство содержит распределитель 6, сумматор 7, блок преобразования частоты 8, масштабный блок 9 и блоки памяти 10 — 10п.

Один из возможных вариантов выполнения ячейки памяти 4 приведен на

Фиг. 2.

Ячейка памяти 4 содержит аналоговые ключи 11, и 11 . записи, аналоговые ключи 1? и 12g считывания,ана- 25 логовые ключи 13 и 13 ускорения разряда накопительных элементов,запоминающие конденсаторы 141 и 14 и операционный усилитель15 с большим входным и малым выходным сопротив- 38 лениями. При этом попарно соединенные управляющие входы аналоговых ключей

13 и 12, lip и 12Z, 13 и 121, 11 и

12 подключены соответственно к первому, второму, третьему и четвертому выходам генератора импульсов 2 управления.

Блок управления 1 предназначен для отпирания каналов масштабного блока 9, пуска генератора импульсов. 2 40 управления и автоматического изменения, например, по заданной программе частоты повторения тактовых импульсов, и может быть выполнен на элементах дискретной техники. 45

Генератор импульсов 2 предназначен для выработки импульсов управления работой линии задержки 3 и может быть выполнен, например, из генератора тактовых импульсов с перестраиваемой частотой, четырехканального распределителя импульсов последовательного действия и схемы ИЛИ, выход которой подсоединен к переключающему входу распределителя 6 им55 пульсов .

Блоки памяти 10 — 10 предназначены для аналогового запоминания и хранения одного выборочного значения исходного сигнала и могут быть выполнены с использованием аналого- 6 вого ключа записи, запоминающего конденсатора,, аналогового ключа считывания и операционного усилителя с большим входным и малым выходным сопротивлениями .

Устройство работает следующим образом.

При поступлении сигналов (,(t-) и

f,. (t) соответственно на входе масштабного блока 9 блок управления 1 будет вырабатывать импульс отпирания каналов масштабного блока 9 и импульс запуска генератора импульсов 2. В результате последний начинает вырабатывать импульсы управления работой линии задержки 3 импульсы переключения распределителя 6.Одновременно с этим сигналыЯ,И)и ((1)после усиления по амплитуде до заданных значений и преобразования средних частот их спектров поступают на входы соответственноо блоков памяти 10 1 — 10п и ячейки памяти 4 линии задержки 3.

При .наличии сигнала f ® на входах блоков памяти 10 и последователь. ном во времени приходе на их управляющие входы канальных импульсов распределителя 6 импульсов через интервалы времени д1,..., (и - 1) g t и И д г на выходах соответственно блоков памяти 10, ..., 10 я g и 10ц и следовательно, на первых входах соответственно блоков умножения 5, 5п и

5 появляются и существуют в течение всего интервала времени7= -<)zt нап,ряжения, прямо пропорциональные соответственно выборкам 7„(дЦ ...,I .((„,) >Q и Я (qgt) сигнала и)

При наличии сигнала на сигнальном входе ячейки 4 4 линии задержки 3 и выработке импульсов управления генератором 2 через интервалы времени hf ,(q i)Atц и д появляются и существуют в течение интервала времени дЕна выходе ячейки памяти 4 и, следовательно, втором входе блоКа умножения 5 напряжения, прямо пропорциональные соотв етс твенно выборкам $ (д Е), . ° °, j< t (n-1) д ),I („д )которые через интервал времени д, с момента их появления на выходе упомянутой ячейки, появляются и существуют в течение интервала времени д1 на выходе ячейки памяти 4 р и, следовательно, втором входе блока умножения 5 < а еще через интервал времени дt, с момента их появления на выходе ячейки памяти 4,они появляются и существуют в течение интервала времениИ на выходе ячейки памяти 4,и,следовательно,втором входе блока умножения 5g.Через интервал времени nat указанные выборки появляются в той же последовательности и существуют в течение интервала времени At на выходе ячейки памяти 4п, и следовательно, втором входе блока умножения 5 .

Таким образом, при наличии сигнала f< (Е)на входе ячейки памяти 41 и выработке импульсов управления генератором 2 на выходе ячеек памяти 44, ...,4„ и 4П и, следовательно, на вторых выходах соответственно блоков 5у, 68б038

Б < -, и 5 < образовываются напряжения, прямо пропорциональные соответственно таким ступенчатым функциям: ((Û), ",f ((k-< М«j„((k- +1) 3, где k = 1- Qtt-ЮВ результате перемножения этих ступенчатых функций в блоках умножения 5 g, ..., 5« < и

5п соответственно на выборки ) (ф, ...

° °, f<,B -1) а 3>,(net). на выходах этих блоков будут образованы соответственно значения, прямо пропорциональные следующим величинам: f(zy)f (д ) 15

° ° < f, f(

У®=Е g { é) 3, ((k- ()л(1, (<=1-п), совпадающую с точностью до постоянного множителя с результатом, полученным после вычисления интеграла свертки, 25 ((< = (<<,(.<@ с)п, (04t.- „O. .D ), по формуле прямоугольни:ков или трапеций.

После восс тановления прежнего (или ЗО заданного) значения средней частоты спектра сигнала 1 ® в блоке преобразования частоты 8 на ныходе устройства будет образовано следующее окончательное значение 35 { ) =, (s t) f, I(«-)+1) Я

Г являющееся приближенным вычислением интеграла свертки

УЙ) = f, (e) f, P - t) дт.

Приведенное описание работы устройства будет справедливо и тогда, когда

f,((:) =f ®=1(О.

В этом случае можно соединить между собой входы масштабного блока 9, а также 45 первый и второй выходы этого блока.

Таким образом, введение новых элементов и установление новых связей позволяет повысить точность и увеличить быстродействие работы устройства.

В результате расширяется сфера применения устройства и круг решае<жх с его помощью задач, и улучшаются технико-экономические показатели при его изготовлении,и эксплуатации.

Формула изобретения

Устройство для вычисления снертки функций, содержащее блок упранления, первый выход которого соединен со входом генератора импульсов и линию задержки, состоящую иэ последовательно соединенных ячеек памяти, выход каждой из которых соединен со входом последующей ячейки памяти и первым входом соответствующего блока умножения, о т л и ч а ю щ е е с я тем, что, с целью повышения точности и быстродействия, оно содержит распределитель, сумматор, блок преоб— раэонания частоты, масштабный блок и блоки памяти по числу блоков умноже— ния, входы всех блоков памяти соединены с первым выходом масштабного блока, второй выход которого соединен со входом первой ячейки памяти линии задержки, третий выход — с первым входом блока преобразования частоты, а его вход является входом устройства, управляющий вход каждого блока памяти соединен с выходом распределителя, управляющий вход каждой ячейки памяти линии задержки соединен с ныходом генератора импульсов, дополнительный выход которого соединен со входом распределителя, выход каждого блока памяти соединен со вторьм нходом соотнетстнующего блока умножения, выход которого подключен ко входу сумматора, дополнительный вход масштабного блока соединен со вторым выходом блока управления, второй вход блока преобразования частоты соединен с выходом сумматора, а его выход является выходом устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9301008, кл. G 06 G 7/00, 1971.

2. Авторское свидетельство СССР

9306471, кл. G Об G 7/16, 1971 °

5В8ОЗВ ;РиГ. 2

Составитель O. Сахаров

Редактор Н, Каменская Техред И.Бабурка КОРР - ктоР d. Решетник

Заказ 5461/48 Тираж 780 Подписное

ЦЧИИПИ Государственного комитета СССР по делам иэобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП Патент, r. ужгород, ул. Проектная, 4.