Блок выборки для интегральных запоминающих устройств с переменной длиной слова

Иллюстрации

Показать всеРеферат

М. А. Носков, Ю, Б. Садомов, И. И. Седова, B. Я. Синдаловский, Л. М. Хохлов и Г. И. Черницкий (72) Авторы изобретения (7!) Заявитель Государственное Союзное конструкторско-технологическое бюро по проектированию счетных машин (54) БЛОК ВЫБОРКИ ИНТЕГРАЛЬНЪ|Х ЗАПОМИНАЮЩИХ

УСТРОЙСТВ С ПЕРЕМЕННОЙ ДЛИНОЙ СЛОВА

Изобретение относится к области автоматики и вычислительной техники н пред,( назначено для применения в оперативных

ЗУ в интегральном исполнении.

Известно. оперативное запоминающее устройство (ОЗУ) в интегральном испол

; некии, содержащее матрицу из однобитных ячеек памяти..Наличие такой матрицы позволяет производить запись (нли считывание) одного бита информации в ячейку (или из ячейки) с произвольно-заданным адресом (1 f.

Для увеличения разрядности запоминаеMblx информационных слов используют параллельное включение однобитных ОЗУ, адресные и уцравляюшие шины которых параллельно объединяют. В етом случае, разрядность слова равняется числу запоминающих устройств, и следовательно, постоянна. Использование такого блока запоминающих устройств для хранения информации с переменной разрядностью, яли с разрядностью не равной числу ЗУ, при» водит к нерациональному использованию

2 памяти. Например, если информационное слово больше ячейки ОЗУ, го его нужно разбить на части и записывать IIo разным адресным ОЗУ, если меньше - го запись

В ОЗУ п уоизводигся с помошью логических операций. Это усложняег работу программиста при наннсании программ.

Наиболее близким техническим решеныем к данному изобретению является устройство, содержащее эапоминаюшую мат» рипу, дешифратор столбпов, дешифратор строк, регистр адреса и счетчик адреса, в котором несколько младших разрядов

{в данном случае — три) регистра адреса выполнены в виде счетчика aapecaj2).

Такая схема адресации позволяет разбить всю зону памяти на ячейки одинаковой разрядности. Однако его устройство не позволяет разбивать память ОЗУ на ячейки произвольной длины, чго является недостатком такой схемы адресации.

IIenb изобретения является повышение информационной емкости устройства.

3 686084 4 достигается тем, начинается с адреса стопбца, не совпа-— я интегральных за- дающего ни с одним из последних адрес переменной дли- сов данной строки, При записи нли считысчетчик адреса, ванин информации модифицируется содерен к адреснымши-. g жимое счетчика 3 адреса и при совпадеены соответственно нии номера адресуемого столбце с любым ов строк и столбцов, из адресов стопбцов, записанных на реуправляюшую шины, гистре 6 адреса, в блоке 5 совпадения иЯ адРеса, РегистР адресов вырабатывается управпяющий сит емаЯ логическаЯ мат О нап, подается на управпяюшую шину 8 и оединены с выхода- процесс записи (ипи считывания} заканчивается, так как этот сигнал останавли ходы котоРого по - вает счетчик Э. Таким образом, адреса дам бпока совпадениЯ строк в матрице 7 могут преобразовыватькоторого соединены 1 ся в одинаковые ипи различные наборы а выход блока сов- номеров стопбцов. Изменение границ ннючен к управпяюшей формационных ячеек в программируемой чика адреса. логической матрице осушествпяется наитавпена бпок схема более цросто - изменением одного фотоства. 20 шабпона в технологическом цикле создаит дешифратор 1 ния матрицы памяти.

Поставленная цель что в блок выборки дл поминающих устройств ной слова, содержащий вход которого подключ нам, а выходы соедин с входами дешифратор входные, выходные и введены биок совпаден адреса и программиру рице, входы которой с ми счетчика адреса, а ми регистра адреса, вь кпючены к одним вхо адреса, другие входы с выходными шинами, падения адреса подкл шине и к входу счет

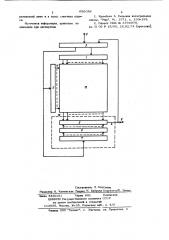

На чертеже предс предлагаемого устрой

Устройство содерж столбцов, дешифратор 2 строк, счетчик

3 адреса, блок 4 переменной адресации, состоящий из блока 5 совпадения адресов, регистра 6 адреса и программируемой погической матрицы 7, управляющую шину S, шины адреса 9, выходные шины 10 и выходные шины 11, ьетрицу памяти 12.

Устройство работает спедуюшим обраФ зом.

Начапьный адрес информационного спова записывается по адресным шинам 9 в счетчик 3 адреса. Установпенный адрес через блок 2 дешифратора строк задаег адрес одной строки as N -строк матрицы памяти 12, а через блок 1 дешифратора стопбцов - aapec одного стопбца из

A -стопбцов матрицы. Обращение к спе» дующим битам информационного спова 4О осуществляется поспедовательным увепиче-( нивм номера стопбца при постоянном номере строки. Паспе считывания информа ции с поспеднего столбца, устанавпивается адрес первого стопбца, а номер стро <> ки увепнчивае гся на единицу. Увеличение номеров строк и стопбцов осуществляется увепичением на единицу содержимого счетчика 3 адреса. При обращении к матрице памяти с записью ипи считыванием адрес строки поступает-на вход блока 4 переменной адресации с шин магрицы 12. Каждый адрес строки преобразуется в программируемой погической матрице 7 в произвольный, но фиксированный для каждой строки, набор адресов стопбцов. Набор адресов столбцов с матрипы 7 поступает на регистр 6 адреса и запоминается на нем. Обращение к матрице цамяти всегда

Предпоженное устройство позволяет: разбить всю зону запоминающей матрицы иа ячейки постоянной длины, равной раэ рядности информационных caos, принятой в системе разбить эоны памяти н& ячейки разной ццины, дая хранения в каждой информационного слова соответствующей раэряднос ти.

Кроме того йрименеиие бпока 4 переменной адресации позволит значитепьно повысить еффективность испопьэования

ОЗУ и рационапьно организовать в ОЗУ зоны спужебных ячеек.

Формупа изобретения

Бпок выборки интегральных запоминающих устройств с переменной щтиной спова, содержаший счетчик адреса, вход которого подкпючен к адресным шинам, а выходы соединены соответственно с входами дешифраторов строк и столбцов, входные, вы» ходные и управпяюшие шины, о т и ич а ю m и и с я тем, что; с целью повышения информационной емкости устройessa, он содержит блок совпадения адреса регистр адреса и программируемую логическую матрицу, входы которой соединены с выходами счетчика адреса, а выходьi с входами регистра адреса, выходы которого подключены к одним входам блока совпадения адреса, другие входы когорого соединены с выходными шинами, а выход блока совпадения адреса подключен к уп686084 равляюшей шине и к входу счетчика адреса.

Источники информации, принятые во внимание при экспертизе

1. Кхамбата А. Большие интегральные схемы, Мир, М., 1971, с. 190 195.

2. Патент США ¹ 3794970, кл. 6- 06 Е 1 5/00, 26.02.74 (прототип).

Составитель Л. Амусьева г

Редактор Н. Каменская Тех д H. Бабурка Ко екго О. Билак

Заказ 5469/51 Тираж 681 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4