Запоминающее устройство с исправлением ошибок

Иллюстрации

Показать всеРеферат

ОП " Е

ИЗОБРЕТЕН ИЯ

Союз Советских

Социапистииесюа

Республик

<»> 686О85 (61) Дополнительное к авт. саид-ву (22) Заявлено 13.04.78 (23) 2605169у1824 с присоединением заявки М(23) Приоритет

Опубликовано 15.09.79. Бюллетень ¹ 34

Дата опубликования описания .20.09,79 (5a)M. Кл.

С ll С 29/00

Гесударствеевй кеиетет

СССР ее делам кзееретеиел к открытей (5З) MK 681.327 (088, 8) (72) Авторы изобретения

A. К. Култьтгин, Б. Е. Гласко, H. И. Вариес и Г. Х. Власова (7l) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ИСПРАВЛЕНИЕМ ОШИБОК

Изобретение относится к области зал оминаюших ус гровс тв.

Известно запоминаюшее устройство с исправлением ошибок, содержашее регистр числа, блок контроля, основной блок намя% ти, дополнительный блок памяти н дешифратор jl). В этом устройстве осушествпяется исправление одиночных ошибок при считывании путем сравнения контрольной информации по Хеммингу, считанной из дополнительного блока памяти одновремен но со считыванием числа из основного блока памяти, с контрольной ннформапией по Хеммингу, сформированной блоком кон»

rpona, дальнейшей дешифрацией результата сравнения и корректированием числа в регистре числа йо результату .дешифрации.

Недостатком етого устройства являетсм сильное увеличение количества оборудования за счет блока кронгроля, а также увеличение времени обрашения за счет формирования контрольной информации по

Х ем ми игу.

Наиболее близким техническим решением к данному изобретению является запоминаюшее устройство с исправлением ошн бок, содержашее основной и дополнительный накопители, блок выборки адресов, де- . шифратор, блок контроля н регистр числе, выполненный на трнт герах со счетнымн входами, причем выход блока выборки адресов соединен со входами накопителей, входы блока контроля и одни из информационных входов регистра числа подключены к выходам основного накопителя, первый выход блока контроля:соединен с уп» равляюшим входом регистра числа(2).

Недостатком этого запомннаюшего уср ройства является сильное увеличение количества оборудования за счет сложного блока контроля, за счет организации резерва запоминаюших элементов для замены имн дефектных запомннаюших элементоь, à также при организаттин полноразряд» ного запоминаюшего устройства нз одно- . разрядных накопителей. QpyraM недостатком является невозможность использования 4 ший вход регистра числа 5 поступает сигнал разрешения выдачи числа. Одновременно с другого выхода блока контроля 4 поступает сигнал, закрывающий все вторые входы элементов И 7. В.случае если блок контроля 4 фиксирует наличие ошибки, с первого выхода блока контроля

4 на упрввляюший вход регистра числа

5 цоступает сигнал, запрещающий выдачу

О числа. Одновременно со второго выхода блока контроля 4 поступает сигнал, огкрываюшнй вторые входы элементов И 7.

Параллельно считыванию числа из основного накопителя 2 по этому же адресу происходит считывание числа из дополнительного накопителя 3, в котором хранится код номера дефектного разряда.

Код номера дефектного разряда и ступает на дешифратор 6, возбуждая один нз его выходов, связанный с первым входом со» ответствуюшего элемента И 7. Сигнал с выбранного элемента И поступает на счет ный вход того триггера регистра числа

5, в котором зафиксировано наличие де5 фектного зацоминаюшего элемента основ ного накопителя 2; при этом происходит инвертирование состояния триггера в регистре числа 5.в неисправном разряде.

ЗО

После коррекции информации в регистре числа с первого выхода блока контроля

4 нв упрввляюший вход регистра числа 5 поступает сигнал, разрешающий выдачу . скорректированного числа.

Предлагаемое запоминающее ycrpoIc т

3S во с исправлением ошибок,. вызванных, дефектами накопителя, -выгодно отличвег ся or прототипа тем, что имеет энвчитель но более простую структуру, так как не имеет резерва-запоминвюших элементов для замены дефектных запоминающих эле ментов, в также зв счет того, что «схемы коррекции организованы не поразрядно, в для всего полноразрядного блока пвмд и.

Оно имеет значительно меньшую глубину схем коррекции, что повышает быстродей ствие устройства.

686085

Запоминающее устройство с исправлением ошибок, содержащее основной и дополнительный накопители, блок выборки.

55 адресОВ, дешифратор, блОк кОнгроля и ре гистр числа, причем выход блока Выбор» ки адресов соединен со входами иакоците лей, входы блока контроля и орин as uu формационных входов регистра числа под накопителей, выполн нных совместно со схемами записи и воспроизведения.

Целью изобретения является повышение быстродействия и упрошение запоминающего устройства с использованием возникаюших в процессе изготовления накопителей дефектных запоминающих элементов.

Это достигается тем, что предлагае мое устройство содержит элементы И по числу разрядов основного накопителя, пер-1 вые входы которых подключены к выходам дешифратора, входы которого соединены с выходами дополнительного накопителя, вторые входы элементов И соединены со вторым выходом блока контроля, а выходы с 1 другими Йнформ&диОнными Входами реги стра числа.

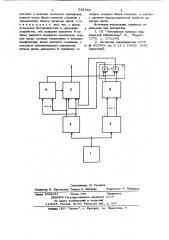

На чертеже представлена блок-схема предложенного запоминающего устройства.

Звпоминаюшее устройство содержит блок выборки адресов 1, основной нвког питель 2, дополнительный накопитель 3, блок контроля 4, регистр числа 5, выполненный на триггерах со счетным вхо2 дом, дешифратор 6, элементы И 7.

Первые входы элементов И 7 подключены к выходам дешифрвтора 6, входы которого соединены с выходами накопителя 3, вторые входы элементов И 7 сое динены с одним из входов блока контро ля 4, а выходы - с одним иэ информа ционных входов, регистра числа 5.

При этом основной накопитель 2 со» держит некоторое количество дефектных запоминающих элементов, но.не более одного по каждому адресу. Адреса дефеки ных. запоминающих элементов заранее иэ» вестны и по этим же адресам в дополнительном накопителе 3 хранятся коды номеров дефектных разрядов. Йополнитель»ный накопитель 3 дефектов не имеет.

Запоминающее устройство .работает следукяиим образом.

Блок выборки адресов 1 формирует код адреса, который одновременно посту» пает на адресные входы основного 2 и дополнительного 3 накопителей. В режиме считывания число as основного накопите» ля 2, который содержит дефектные sàïî» минаюшие элементы, совместно с разрядом контроля по четности параллельно поступает на блок контроля 4 и счетные

Входы регистра числа 5. Блок контроля

4 производит проверку правильности числа, считанного из основного накопителя

2 и в случае отсутствия ошибок с одноГО из ВыхОдОВ контроля 4 н& упраВляю»

4 ормулв изобретения

5 686083 о ключены к выходам основного накопителя, вторым выходом блока контроля, а выходыпервый выход блока контроля соединен с с другими информацноннымн входами реуправляюшим входом регистра числа, о т- гистра числа. личающееся тем, что,с целью Источники информации, принятые во повышения быстродействия и упрощения внимание цри экспертизе устройства, оно содержит элементы И по 1. Сб. "Актуальные вопросы гехчислу разрядов основного накопителя, пер- нической кибернетики, М., Наука, вые входы которых подключены к выходам 1972, с. 235-240. дешифратора, входы которого соединены с 2. Авторское свидетельство СССР выходами дополнительного накопителя, . 10 М 402058, кл. Cj 11 С 29/00, 1972 вторые входы элементов И соединены со .(прототип).

Составитель В. Рудаков

Редактор Н. Каменская Техред Н. Бабурка Корректор 4. Гриценко

Заказ 5469/51 Тираж 681 Подписное

БНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4