Умножитель частоты следования импульсов

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик 687578 (61) Дополнительное к ает. свид-ву (22) Заявлено 11.0777 (21) 2508466/18-21 с присоединением заявки М— (23) Приоритет

Опубликовано 250979, Бюллетень Но 35

Дата опубликования описания 28.09.79 (51) М. Кл.2

Н 03 К 5/156

Государственный комитет

СССР по делам изобретений и открытий (53) УДК 621 . 374 . 33 (088.8) (72) Авторы

ИЗОбрЕтЕНИя В.М. Брусницын, В,Н. Глухов н Г.А. Захарова (71) заявитель

{ 54 ) умнОжитель чА стОте1 следОВА ни я

КМПУЛЬСОВ

Изобретение относится к импульсной технике °

Известен умножитель частоты следования импульсов, содержащий формирователь, пересчетное устройство, ключ, элементы И, ИЛИ, управляемую линию задержки, реверсивный счетчик, генераторы стробов (1).

Недостатком этого умножителя является недостаточный коэффициент умножения.

Наиболее близким по технической сущности к предлагаемому является умножитель частоты, содержащий логический элемент ИЛИ, один вход которого соединен с входом первого генератора стробимпульсов, входной шиной и первым входом трехвходового логического элемента И, второй вход которого соединен с выходом второго генератора стробимпульсов, а выход подключен к первому входу реверсив-, ного счетчика, второй вход которого соединен с выходом второго трехвходового логического элемента И, первый вход которого подключен к выходу первого генератора стробимпульсов, второй вход соединен с входом второго генератора стробимпульсов и выходом двухпозиционного ключа, входы управления которого соединены с выходами пересчетного блока, информационный вход соединен с выходом формирователя импульсов и выходной шиной, а второй выход подключен к входу пересчетного блока и второму входу логического элемента ИЛИ, выход которого подключен к входу управляемой линии задержки, входы управления которой подключены к выходам реверсивного счетчика (2).

Однако такой умножитель недостаточно точен.

Целью изобретения является повышение точности.

Это достигается тем, что в умножитель частоты следования импульсов, содержащий логический элемент ИЛИ, один вход которого соединен с входом первого генератора стробимпульсов, входной шиной и первым входом трехвходового логического элемента

И, второй вход которого соединен с выходом второго генератора стробимпульсов, а выход подключен к первому входу реверсивного счетчика, второй вхоц которого соединен с выходом второго трехвходового логического элемента И, первый вход кото3() рого подключен к выходу первого re687578 нератора стробимпульсов, второй вход соединен с входом второго. генератора стробимпульсов и выходом двухпозиционного ключа, входы управления которого соединены с выходами пересчетного блока, информационный вход соединен с выходом формирователя импульсов и выходной шиной, а второй выход подключен к входу пересчетного блока и второму входу логического элемента ИЛИ, выход которого *одключен. к входу управляемой линии задержки, входы управления которой подключены к выходам реверсивного счетчика, введены два триггера, два двухвходовых логических элемента И, дополнительный управляемый элемент задержки, два диода, кондейсатор и два дополнительных генератора стробимпульсов, выходы которых подключены к третьим входам трехвходовых логических элементов И, вход каждого соединен с входом соответствующего основного генератора стробимпульсов и одним из входов одного триггера, вторые входы которых соединены с выходом первого из упомянутых генераторов стробимпульсов, причем входы триггеров первые — соответственно, а вторые — перекрестно соединены с входами двухвходовых логических элементов И, выход одного из которых через диод, а выход второго через последовательно включенные инвертор и второй диод соединены с конденсатором и входом управления дополнительного элемента задержки, включенного между выходом управляемой линии задержки и входом Формирователя импульсов.

t.

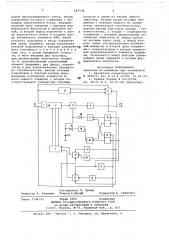

На чертеже приведена структурная электрическая схема предлагаемого умножителя, Умножитель содержит логический элемент ИЛИ 1„ управляемую линию 2 задержки, дополнительный управляемый элемент З.задержки, формирователь 4 импульсов, двухпозиционный ключ 5, пересчетный блок б, реверсивный счетчик 7, трехвходовый логический элемент И 8, генераторы 9 и 10 стробимпульсов, трехвходовый логический элемент И 11, дополнительные генераторы 12 и 13 стробимпульсов, триггеры 14 и 15, двухвходовые логические элементы И 16, 17, инвертор 18, диоды 19, 20 и конденсатор 21.

Входной сигнал подан на входную шину 22. Выходной сигнал снимается с выхода 23.

Принцип работы умножителя частоты следования импульсов заключается в следующем, На вход подается первый подлежащий умножению импульс и через логический элемент ИЛИ 1, предназначенный для логического суммирования

5О

6О

65 входных импульсов умножаемой часто. ты и импульсов обратной связи, поступающих с формирователя 4 импульсов через двухпозиционный ключ 5, он поступает на вход управляемой линии 2 задержки. Одновременно этот импульс поступает на вход логического элемента И 11, первый вход триггера 15 и запускает основной и дополнительный генераторы 9 и 12 стробов, которые выдают: основной — разрешение, а дополнительный — запрет на логический элемент И 8, причем сигнал запрета значительно короче сигнала разрешения и равен произведению величины дискрета управляемой линии 2 задержки на коэффициент умножения.

Через промежуток времени, соответствующий периоду выходных импульсов, импульс с выхода формирователя

4 импульсов поступает на импульсный вход двухпозиционного ключа 5 °

При нулевом положении пересчетного блока б, предназначенного для подсчета импульсов на выходе Формирователя 4 импульсов и коммутации этих импульсов с помощью двухпозиционного ключа 5, двухпозиционный ключ находится в таком положении, при котором импульсы с выхода формирователя

4 импульсов поступают на вход пересчетного блока б и один из входов логического элемента ИЛИ 1, а с его выхода — на вход управляемой линии

2 задержки и т.д. 11икл работы умножителя частоты следования импульсов будет повторяться до тех пор, пока на вход пересчетного блока б не поступит число импульсов, численно равное коэффициенту умножения. В этот момент пересчетный блок б устанавливает двухпозиционный ключ 5 в положение, при котором импульс с выхода пересчетного блока через ключ поступит на цепи сброса пересчетного блока б (для обнуления последнего), первый вход триггера 14, на вход логического элемента И 8 и на запуск основного и дополнительного генераторов 10 и 13 стробимпульсов при этом основной генератор 10 стробимпульсов выдает разрешение, а дополнительный генератор

13 запрет, причем сигнал запрета значительно короче сигнала разрешения °

Если сумма периодов выходных импульсов меньше периода умножаемых импульсов, то выходной умножаеьжй импульс поступает на логический элемент И 11 во время действия строба разрешения, вырабатываемого основным генератором 10 стробимпульсов и, если в это время закончилось действие дополнительного строба, вырабатываемого дополнительным генератором 13 стробимпульсов, импульс сле5

687578 дует на вход сложения реверсивного счетчика 7 и увеличивает записанный в нем код на единицу.

Реверсивный счетчик 7 предназначен для хранения кода, определяющего

15

45 управляемой линии 2 задержки на коэффициент умножения, в последнем периоце.

Грубо Процесс установления требуемого периода следования импульсов умноженной частоты осуществляется дискретно с точностью дискрета управляемой линии 2 задержки. Точное значение периода следования импульсов умноженной частоты осуществляется следующим образом.

Если сумма периодов выходных импульсов меньше периода умножаемых импульсов, то импульс с выхода двухпозиционного ключа 5 перебрасывает

Формула изобретения

Умножитель частоты следования импульсов, содержащий логический элемент ИЛИ, один вход которого соединен с входом первого генератора стробимпульсов, входной шиной и .первым входом трехвходового логического элемента И, второй вход которого соединен с выходом второго генератора стробимпульсов, а выход подключен к первому входу реверсивного счетчика, второй вход которого соединен с выходом второго трехвходового логического элемента И, первый вход которого подключен к выходу первого генератора стробимпульсов, второй вход соединен с входом вто50

60 триггер 14 в положение, при котором на выходе элемента И 17 образуется отрицательный потенциал, так как триггер 15 находится в положении, при котором на второй вход логического элемента И 17 подается также отрицательный потенциал. Отрицательный потенциал существует в течение интервала времени между импульсом, поступающим на триггер 14, и импульсом, поступающим на триггер 15. 3а это время происходит заряд конденса- 65 рого генератора стробимпульсов и высочетания последовательного включения отводов управляемой линии 2 задержки. Увеличение кода, хранящегося в реверсивном счетчике 7, на единицу приводит к увеличению времени задержки и периода следования выходных импульсов.

Если сумма периодов следования выходных импульсов больше периода умножаемых импульсов, то очередной входной умножаемый импульс поступит на запуск основного и дополнительного генераторов 9 и 12 стробимпульсов раньше, чем импульс с выхода двухпозиционного ключа 5 ча один из входов логического элемента И 8.

Также как и в предыдущем случае, на ьыхбде логического элемента И 8 появится импульс при условии наличия на его входах разрешающего потенциала и отсутствия запрещающего. С выхода логического элемента И 8 импульс поступает на вход вычитания реверсивного счетчика 7 и уменьшает значение кода на единицу, что приводит к уменьшению времени задержки и уменьшению периода следования входных импульсов.

При отсутствии импульсов на выходах логических элементов И 8, 11 код в реверсивном счетчике 7 не обновляется. Это свидетельствует о том, что умножение осуществляется в соответствии с заданным коэффициентом умножения, но с ошибкой, не более произведения величины дискрета тора 21 через диод 20, напряжение на конденсаторе 21 увеличивается и увеличивает время задержки элемента 3 задержки, что приводит к увеличению периода следования. Умножаемых импульсов до тех пор, пока сумма периодов умноженных импульсов не сравнивается с периодом умноженных импульсов.

Если же сумма периодов выходных импульсов больше периода умножаемых импульсов, то входной импульс. перебросит триггер 15 в положение, при котором на логический элемент И 16 будет подан отрицательный потенциал, и так как триггер 14 находится еще в положении, при котором на второй вход логического элемента И 16 также подается отрицательный потенциал, на его выходе будет иметь место отрицательный потенциал в течение интервала времени между импульсом, поступившим на триггер 15, и импульсом поступившим на триггер 14. Отрицательный потенциал с выхода логического элемента И 16 преобразуется в положительный посредством инвертора 18 и конденсатор 21 начинает разряжаться через диод 19.

Уменьшение напряжения на конденсаторе 21 приводит к уменьшению величины задержки элемента 3 задержки до тех пор, пока сумма периодов умноженных импульсов не сравнивается с периодом умноженных импульсов °

В установившемся режиме напряжение на конденсаторе 21 поддерживается на необходимом уровне за счет частичных зарядов и разрядов в области появления импульсов с выходов логических элементов И 6, 17.

В промежутках между импульсами конденсатор 21 практически изолирован и сохраняет неизменным напряжение, что создает условия формирования одинаковых периодов выходных импульсов.

687578

Составитель Т. Артюх

Редактор H. Хлудова Техред С.Мигай Корректор А, Гриценко

Тираж 1060 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д. 4/5

Заказ 5744/52

Филиал ППП Патент, г.. Ужгород, ул. Проектная, 4 ходом двухпозиционного ключа, входы управления которого соединены с выходами пересчетного блока, информационный вход соединен с выходом формирователя импульсов и выходной шиной, а второй выход подключен к входу пересчетного блока и второму входу логического элемента ИЛИ, выход которого подключен к входу управляемой линии задержки, входы управления которой подключены к выходам реверсив р ного счетчика,отличающийся тем, что, с целью повышения точнос ти, в него введены два триггера, два двухвходовых логических элемента И, дополнительный управляемый элемент задержки, два диода, конденсатор и два дополнительных генератора. стробимпульсов, выходы которых подключены к третьим входам трехвходовых логических элементов И, вход каждого соединен с входом соответствующего генератора стробимпульсов и одним из входов одного триггера, вторые входы которых соединены с выходом первого из упомянутых reHepaTopoB стробимпульсов, причем выходы триггеров первые — соответственно, а вторые — перекрестно соединены с входами двухвходовых логических элементов И, выход одного из которых через диод, а выход второго через последовательно включенный инвертор и второй диод соединены с конденсатором и входом управления дополнительного элемента задержки, включенного между выходом управляемой линии задержки и входом формирователя импульсов.

Источники инФормации, принятые во внимание при экспертизе

1. Авторское свидетельство

В 499673, кл. Н 03 К 23/00, 10.02.72.

2, Заявка Японии М 43-52538, кл. 98(5) В 5, 26.07.68 (прототип),