Устройство для исправления и обнаружения ошибок

Иллюстрации

Показать всеРеферат

Союз Советскнк

Соцналнстнческыи

Республнк

Оп ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (! i i 687.6 1 2 (6 l ) Дополнительное к авт. свнд-ву (22)За влено 03.04.78 (21) 2598831/18 09 с прнсоеднненнеит заявки РЙ (23) Приоритет

Опубликовано 25 09.79. Бюллетень М 35

Дата опубликования описания 27.09.79 (5т)M. Кл.

Н 04 Q 1/10 //

G 06 F 11/00

Гесударставииьй ианитат

СССР аа делам изобратвиий в аткрмтий (53 ) УД,К 62 1. 394. .14 (088.8 ) (72) Авторы изобретения

Е, Б. Бродская, В. С. Блейхман и A. В. ттвигун (7т) Заявитель (54) УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ И ОБНАРУЖЕНИЯ

ОШИБОК

Изобретение относится к передаче данных и может использоваться в устройствах зашиты от ошибок аппаратуры передачи дискретной информации.

Известно устройство для исправления и обнаружения ошибок, содержашее на входе накопитель, последовательно соединенные да.тчик ошибок и сумматор по модулю два, а также ключ Ы .

Однако это устройство имеет невысокое быстродействие.

Цель изобретения - повышение быстродействия.

Для этого в устройство для исправленття и обнаружения ошибок, содержашее на входе накопитель, последовательно соединенные датчик ошибок и сумматор по модулю два, а также ключ, введены два селектора, формирователь кодового слова и блок сравнения, при этом первый выход накопителя через первый селектор подключы к другому входу сумматора по модулю два, выход которого через формирователь кодового слова подключен к входу второго селектора и к одному иэ входов блока сравнения, к другому входу которого подключен второй выход накопителя, а выход блока сравнения подключен к входу датчика ошибок и к разрешаюшему входу ключа, к информационному входу которого подключен выход второго селектора.

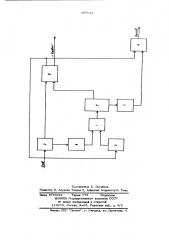

На чертеже изображена структурная электрическая схема предлагаемого устройства.

Оно содержит сумматор 1 по модулю два, накопитель 2, датчик 3 ошибок, ключ

4, формирователь 5 кодового слова, селекторы б и 7 и блок 8 сравнения.

Устройство работает следуюшим образом.

Принятая комбинация записывается в накопитель 2, выполненный и -разрядным, где т1 - число элементов передаваемой комбинации, затем в датчике.3 оши бок формируется одна иэ ошибок в информационной части, которые исправляются декодируюшим устройством, датчик 3 поочередно до сигнала ошибка исправ687612

10

40 лена" формирует хомбинации ошибок, нулевую, все возможные одиночные, двойные, т.д. вплоть до 1 -кратных ошибок в блоках длиной k - число информационных символов в двоичном (n, k ) коде.

В сумматоре 1 по модулю два комбинация ошибки складывается с комбинацией, состоящей из символов принимаемого слова, стоящих на информационных позициях, пропускаемой в соотзетствуюшие моменты времени через селектор.

В формирователе 5 кодового слова по информационной части формируется предполагаемое кодовое слово, которое одновременно посимвольно в блоке 8 сравнивается с принятым словом. Если принятое слово от сформированного отличается менее чем в t позициях или ровно в позициях, то блок 8 сравнения выдаст сигнал разрешения на ключ 4 и на выход устройства через селектор 7 поступает информационная часть сформированного кодового слова.

Если принятое слово отличается от сформированного более чем в 1 позициях, то блок 8 сравнения выдае-. -.игнац на датчик 3 ошибок, после чего на сумматор 1 по модулю два поступает очередная k - разрядная комбинация ошибки.

Если в процессе перебора нулевой, всех одиночных, двойных т.д. вплоть до кратных ошибок, надклвдываемых на ин- формационную часть принятого слова, не найдется ни одного кодового слова, которое бы отличалось от принятого не более чем в позициях, то блок 8 сравнения выдает сигнал обнаружена ошибка .

Таким образом, предлагаемое устройство осуществляет исправление t -кратных ошибок и обнаружение ошибок большей кратности при использовании разде20

35 лимых блоковых ходов по алгоритму декодирования по минимуму расстояния.

Предлагаемое устройство может работать в реальном масштабе времени с большими скоростями передачи данных, чем известное. Кроме того, появляется возможность расширить число кодов, с которыми можно работать в реальном масштабе времени, т.е. возможна работа с кодами большей длины, и при этом время обработки комбинации будет сравнимо с временем приема комбинации.

Формула изобретения

Устройство для исправления и обнаружения ошибок, содержащее на входе накопитель, последовательно соединенные датчик ошибок и сумматор по модулю два, а также ключ, о т л и ч а ю ш е е с я тем, что, с целью повышения быстродействия введены два селектора, формирователь кодового слова и блок сравнения, при этом . первый выход накопителя через первый селектор подключен к другому входу сумматора по модулю два, выход которого через формирователь кодового слова подключен к входу второго селектора и к одному. иэ входов блока сравнения, к другому входу которого подключен второй выход накопителя, а выход блока сравнения подключен к входу датчика ошибок и к разрешающему входу ключа, к информационному входу которого подключен выход . второго селектора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

¹ 515295, кл. Н 04 „1/10, 1976 (прототип).

Составитель E. Погиблов

Редактор Н. Хлудова Техред Л. Алферова Корректор Н. Степ

Эаказ 5760/54 Тираж 775 Подписное

ЫНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж35, Раушская наб., д. 4/5

Филиал ППГ1 Патент, г. Ужгород, ул. Проектная, 4