Приемник дискретных сигналов

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик (» 687620 (61 ) Дополнительное к авт. сяид-ву (22)Заявлено 14.06.78 (2l) 2628801/18-0,. (Sl)M. Кд .

Н 04 li 25/40// с лрисосдинениеи заявки Ж

H 04 В 1/10 тзсфРфстееккьй хОихтет ссср ю делеи нзебретенхк в еткрытхй (23) Лриоритет—

Опубликовано 25.0 9. 79. Бюллетень И 35

Дата опубликования описания 28.00.79 (53) УДК, G 2 1. 3 34, 6 2(088. 8) B. И. Васильев, А. П. Буркин, С. Ж. Кишенский и А..А. Пичугин (72) Авторы изобретения (7l ) Заявитель Московский институт инженеров гражданской авиации (54) ПРИЕМНИК ДИСКРЕТНЫХ СИГНАЛОВ

Изобретение относится к электросвязи и может использоваться в системах передачи дискретной информации и теле— графин.

Известен приемник дискретных сигналов, содержаший не менее трех под5 каналов, каждый из которых состоит из последовательно соединенных фильтра и амплитудного детектора, выход каждого амплитудного детектора первого и вто30 рого подканалов подкшочен через последовательно соединенные блок сравнения и пороговый элемент. ко входам решаюшего блока t1).

Однако известный приемник дискретl5 ных сигналов требует затраты значительного времени настройки и недостаточно помехоустойчив.

Цель изобретения — повышение помехоустойчивости и сокрашение времени настройки.

Для этого в приЕмник дискретных сигналов, содержаший не менее трех подканалов, каждый из которых состоит из последовательно соединенных фильтра и и амплитудного детектора, выход каждого амплитудного детектора первого и второго подкапалов подключен через последовательно соединенные блок сравнения и пороговый элемент ко входам решаюшего блока, введен инвертор, при этом выход амплитудного детектора третьего подканала подключен через инвертор к другим входам блоков сравнения первого и второго подканалов.

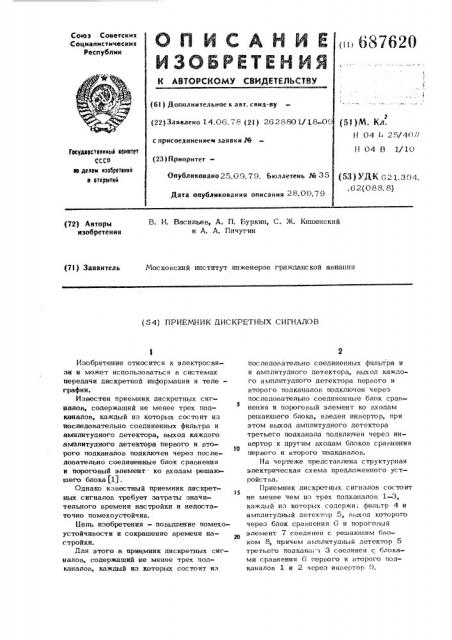

На чертеже представлена структурная электрическая схема предложенного устройства.

Приемник дискретных сигналов состоит не менее чем из трех подканалов 1-3, каждый пз которых содержи; фильтр 4 и амплитудный детектор 5, вьиод которого через блок сравнения 6 и пороговый элемент 7 соединен с решаюцшм блоком 8, причем амплитудный детектор 5 третьего полкана "з 3 соединен с блоками сравнения 6 первого и второго нолканалов 1 и 2 через инвертор 9.

6 876 20

Решаюший блок 8 выдает соответствующий символ выходного алфавита.

Ко входу инвертора 9 можно подключать выход амплитудного детектора 5 любого полквнапв 1-3. Такой выбор позволяет при неидентичности характеристик подканалов 1 — 3 свести к минимуму влияние неравномерности характеристик линий связи нв помехоустойчивость прием1О ника.

11П11ИПИ Заказ 5760/54 Тираж 775

Подписное

Филиал ППП Патент", г, Ужгород, ул. Проектная, 4

Устройство работает слепуюшим обр««зом.

Поскольку спектр импульсной помехи

;значительно шире полосы пропускания фильтров 4 ее воздействие на приемник вызывает реакцию фипьт1юв, которая определяется частотной хврвктеэистикой прием ника и спектральной характеристикой помехи.

При отсутствии полезного сигнала воздействие помехи вызывает появление на выходах блоков сравнения 6 сигналов: Х «(С))Ои Х P) =О.

Гсли частотные характеристики фильтров 4 идентичны, то огибаюшая на выхо15 дах амплитудных детекторов 5 имеет опинаковый вид.

При этом при выборе определенных коэффициентов передачи амплитудных де20 текторов 5 при нулевых. уровнях напряжений срабатывания пороговых элементов 7 ни один из них не срабатывает независимо от характеристик импульсной помехи. Решвюший блок 8 при воздействии помехи не выдает ни одного из разрешенных значений символа.

При передаче полезного сигнала Ис баланс напряжений на выходах блоков сравнения 6 нарушается и сигналы нв йх выходах нринимают Вид

X,()>О и Х, ®=О.

Причем последнее равенство аналогично воздействию только импульсной помехи;

Следовательно, срабатывает пороговый элемент 7 первого подканапа 1.

Фо рмула изобретения

Приемник дискретных сигналов, содержаший не менее трех подканалов, каждый из которых состоит из последовательно соединенных фильтра и амплитудного детектора, выход каждого амплитудного детектора ° первого и второго подканалов подключен через последовательно соединенные блок сравнения и пороговый элемент ко входам решаюшего блока. о т .л и ч а ю ш и и с я тем, что, с целью повышения помехоустойчивости и сокраше-. ния времени настройки, введен инвертор, при этом выход амплитудного детектора третьего подканала подключен через инвертор к другим входам блоков сравнения первого и второго подканалов.

Источники информации, приняже во внимание при экспертизе

1. Авторское свидетельство СССР

М«5фЗ 16 1, кп. Н 04 В 11 l0 l975 (прототип) .