Устройство для сопряжения оперативной памяти с процессором и каналами ввода-вывода

Иллюстрации

Показать всеРеферат

О П И С А Н И E(»)689439

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Соеетскик

Социалистических

Республик (б1) Дополнительное к авт. свид-ву— (22) Заявлено 06.09.77 (21) 2520779/18-24 (51). М.Кл. 6 06 F 13/06 с присоединением заявки №вЂ” (23) Приоритет— (43) Опубликовано 07.01.82. Бюллетень № 1 (45) Дата опубликования описания 07.01.82

Хосударственнык комитет

СССР ио делан изобретений и открытий (53) УДК 681.325 (088.8) (72) Авторы изобретения

Н. Н. Бельский, Ю. А. Коханов, Ю. В. Цаплин, В. В. Климов и Ю. С. Ломов (71) Заявитель

Ч

-:а*а »

В

irk Гс Г ?:. о в (54) УСТРОЙСТВО ДЛЯ СОПРЯ)КЕНИЯ

ОП ЕРАТИ В НОЙ ПАМЯТИ С ПРОЦЕССОРОМ,:.:.- ..::f"" i;, ".,:.ь ." г

И КАНАЛАМИ ВВОДА-ВЫВОДА

1 2

Изобретение относится к области вычислительной техники, в частности к устройствам, обеспечивающим сопряжение оперативной памяти с процессором и каналами ввода-вывода, и может быть использовано в системах обработки данных.

Известно устройство для сопряжения оперативной памяти с внешними устройствами (1), содержащее блок памяти, регистр чтения, регистр записи, дешифраторы и узлы модификации. Недостаток устройства состоит в том, что оно имеет незначительную надежность ввиду отсутствия схем контроля процесса обмена. 15

Известно устройство для сопряжения оперативной памяти с процессором и устройствами ввода-вывода (2), содержащее схему логических операций, блок обработ- 20 ки инструкций, регистр связи с процессором, первый и второй регистры команд, регистры запросов, маски запросов, данных, дешифраторы кода операции, номера индикатора, адреса устройства ввода-вывода, 25 первую и вторую схемы формирования адреса, первую и вторую схемы модификации, схему приоритета, шифратор адреса, выходные схемы адреса, информации, схему селекции, 30

Недостаток устройства состоит в том, что оно требует значительных затрат оборудования.

Наиболее близким к изобретению по технической сущности и достигаемому результату является устройство для сопряжения основной памяти с процессором и каналами ввода-вывода (3), содержащее буферную память, подключенную по адресному входу к первому выходу буферного регистра адреса процессора, вход которого связан с группой входов блока сравнения адресов и с выходом коммутатора адреса ряда; последовательно соединенные с буферной памятью регистры записываемой и считанной информации, причем входы регистра записываемой информации подсоединены к информационным шинам каналов и процессора, а вход регистра считанной информации — к информационной шине основной памяти; последовательно соединенные адресную шину основной памяти, коммутатор адреса колонки, матрицу адресов и блок сравнения адресов, причем адресная шина соединена со входом коммутатора адреса ряда; блок приоритета запросов к матрице адресов, соединенный по выходам с управляющими входами коммутаторов адреса колонки и ряда, и к линии приоритета каналов в матрицу адресов, а

689439

65 по входам — к линиям запросов процессора и к запросам матрицы адресов от каналов.

Недостатком известного устройства является наличие конфликта по обращению в буферную память между запросами процессора и каналов ввода-вывода, что значительно снижает быстродействие устройства.

Цель изобретения — повышение быстродействия.

Поставленная цель достигается тем, что в устройство для сопряжения оперативной памяти с процессором и каналами вводавывода, содержащее блок буферной памяти, адресный вход которого соединен с первым выходом первого регистра адреса процессора, регистр записываемой информации, первый, второй входы и выход которого соединены соответственно с первым, вторым входами устройства и с информационным входом блока буферной памяти, ре.гистр считанной информации, первый, второй входы и первый, второй выходы которого соединены соответственно с третьим входом устройства, с выходом блока буферной памяти, с первым выходом устройства и с третьим входом регистра записываемой информации, коммутатор адреса колонки, выход которого соединен с адресным входом блока хранения адресов, коммутатор адреса ряда, выход которого соединен со входом первого регистра адреса процессора и с первым входом схемы сравнения, первый блок приоритета, первый, второй входы и первый выход которого соединены соответственно с четвертым, пятым входами и со вторым выходом устройства, причем второй выход первого блока приоритета соединен с управляющими входами коммутаторов адресов ряда и колонки, первые кодовые входы которых соединены с третьим выходом устройства, а выход блока хранения адресов соединен со вторым входом схемы сравнения, введены коммутатор адреса процессора, коммутатор адреса канала, регистр адреса оперативной памяти, второй регистр адреса процессора, второй блок приоритета, триггер и элемент

ИЛИ, причем шестой вход устройства является входом второго регистра адреса процессора, выход которого соединен со вторыми кодовыми входами коммутаторов адресов ряда и колонки, первый, второй входы и первый, второй выходы регистра адреса оперативной памяти соединены соответственно с выходом коммутатора адреса процессора, с выходом коммутатора адреса канала, с третьим выходом устройства и с информационным входом блока хранения адресов, кодовые входы коммутаторов адресов процессора и канала соединены соответственно со вторым выходом первого регистра адреса процессора и с седьмым входом устройства, пятый и восьмой входы

l5

Зо

45 устройства через элемент ИЛИ соединены с управляющим входом коммутатора адреса канала и с первым входом второго блока приоритета, первый выход которого является четвертым выходом устройства, второй выход второго блока приоритета соединен с управляющим входом коммутатора адреса процессора и с одним из входов триггера, другой вход и выход которого соединены соответственно с выходом схемы сравнения и со вторым входом второго блока приоритета.

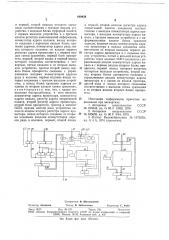

Структурная схема устройства представлена на чертеже.

Устройство для сопряжения оперативной памяти с процессором и каналами ввода-вывода содержит блок 1 буферной памяти, блок 2 хранения адресов, второй регистр 3 адреса процессора, регистр 4 адреса оперативной памяти, первый блок 5 приоритета, коммутатор 6 адреса колонки, коммутатор 7 адреса ряда, схему сравнения 8, первый регистр 9 адреса процессора, регистр 10 считанной информации, триггер 11, второй блок 12 приоритета, коммутатор 13 адреса процессора, регистр

14 записываемой информации, элемент

ИЛИ 15, коммутатор 16 адреса канала, четвертый вход 17, шестой вход 18, пятый вход

19, восьмой вход 20, седьмой вход 21, второй выход 22 первого блока приоритета, выход 23 блока буферной памяти, первый выход 24 устройства, второй выход 25 первого регистра адреса процессора, третий вход 26 устройства, третий вход 27 регистра записываемой информации, информационный вход 28 блока буферной памяти, второй выход 29 второго блока приоритета, второй выход 30 устройства, четвертый выход 31 устройства, второй вход 32 устройства, первый вход ЗЗ устройства, третий выход 34 устройства, адресный вход 35 блока буферной памяти, информационный вход 36 блока хранения адресов.

Устройство работает следующим образом.

При обращения процессора в память он выставляет запрос по входу 17 и адрес по входу 18. При обращении каналов вводавывода в память они выставляют запрос к блоку 2 по входу 19, запрос в основную память по входу 20 и адрес по входу 21.

Блок 5 приоритета выбирает старший по приоритету из одновременно поступивших запросов и открывает соответствующие приоритету вентили на коммутаторе 6 адреса колонки и коммутаторе 7 адреса ряда.

Старший приоритет в блоке 5 имеет запрос от процессора. Коммутатор 6 адреса колонки подключает адресный вход блока 2 либо к регистру 3 адреса процессора, либо к регистру 4 адреса оперативной памяти в зависимости от сигнала по выходу 22. Ком,мутатор 7 адреса ряда подключает адрес

689439 ряда основной памяти к схеме сравнения 8 и к регистру 9 адреса процессора.

Если при обращении процессора по входу 26 на чтение информации адрес ряда ос:новной памяти сравнивается с одним из адресов, записанных в ячейке блока 2, однозначно определенной адресом колонки с выхода коммутатора 6, это означает, что требуемая информация находится в блоке

1. При этом адрес соответствующей ячейки блока 1 заносится на регистр 9. По этому адресу из блока 1 на регистр 10 считанной информации выбирается с выхода 23 требуемая информация и передается в процессор по выходу 24.

Если при обращении от процессора на чтение информации адрес ряда основной памяти не сравнивается ни с одним из адресов, записанных в блоке 2, это означает, 15 что требуемой информации нет в блоке 1. 20

При этом на выходе схемы сравнения (адресов) 8 формируется сигнал несравнения, который устанавливает в единичное состоя ние триггер 11. С выхода триггера 11 повторный запрос процессора поступает на 25 младший по приоритету вход блока 12 приоритета. Старший приоритет в блоке 12 имеет запрос, поступающий на вход 20. При отсутствии в данный момент времени запросов на входе 20 приоритет в оперативную з0 память получает повторный запрос процессора. Сигнал приоритета повторного запроса процессора с выхода 29 блока 12 открывает коммутатор 13 и разрешает прием адреса с выхода 25 регистра 9 адреса процес- 35 сора на регистр 4 адреса оперативной памяти. По этому адресу производится обращение в оперативную память и считывание блока информации. Считанная информация поступает по входу 26 из оперативной па- 40 мяти на регистр 10 считанной информации и затем последовательно через вход 27 регистра 14 и вход 28 блока 1 переписывается в блок 1 буферной памяти. Адрес, по которому будет записан блок информации в 45 блок 1, хранится на регистре 9. Требуемое для процессора слово выделяется из блока информации и с выхода регистра 10 считанной информации выход 24 устройства передается в процессор. При этом адрес ряда оперативной памяти, из которого производится чтение блока информации, записывается по входу 36 в ячейку блока 2, определяемую адресом колонки. При наличии приоритета повторного запроса и свободности 55 блока памяти, соответствующего принятому на регистр 4 адреса основной памяти адресу процессора, на выходе 29 блока 12 приоритета вырабатывается сигнал приоритета, который сбрасывает триггер 11.

Следует отметить, что каналы ввода-вывода читают информацию только из основной памяти и пишут информацию только в основную память. Однако информация в блоке 1 буферной памяти должна быть точной копией информации в соответствующих блоках основной памяти. Поэтому, если канал изменяет информацию в основной памяти, необходимо либо изменить (записать) информацию в блоке 1 буферной памяти, либо аннулировать ее в блоке 1 буферной памяти, т. е. сбросить разряд присутствия соответствующего данному адресу блока информации в блоке 2. В данном устройстве производится аннулирование информации путем сброса разряда присутствия соответствующего блока информации в блоке 2.

При обращении на запись информации в память от каналов ввода-вывода в устройство поступают два запроса, которые устанавливаются в единичное состояние одновременно. Запрос по входу 19 к блоку 2 сбрасывается сигналом по выходу 30 с выхода блока 5. Запрос по входу 20 в основную память сбрасывается сигналом с выхода 31 приоритета запроса канала в основную память при свободности соответствующего данному запросу блока памяти.

При наличии хотя бы одного из запросов по входу 19 или 20 на выходе элемента ИЛИ

15 формируется сигнал, открывающий коммутатор 16 и разрешающий прием адреса от каналов ввода-вывода на регистр 4. Адрес от каналов ввода-вывода сохраняется на регистре 4 до тех пор, пока не будет запущен соответствующий этому адресу блок памяти и пока в блоке 2 не будет сброшен разряд присутствия соответствующего этому адресу блока информации в блоке 1 буферной памяти. Таким образом, наличие блоков приоритета 5 и 12 и двух регистров адреса 3 и 4 дает возможность параллельно (одновременно) обрабатывать запросы от каналов ввода-вывода и центрального процессора. Конфликт между этими запросами может возникнуть только при обращении процессора в основную память, т. е. только при установке в единичное состояние триггера 11. Поскольку большинство обращений (до 95О/о) от процессора выбирают данные из блока 1 буферной памяти, то конфликт между каналами и процессором к основной памяти не сказывается существенно на производительности вычислительной машины, Устройство дает возможность увеличить быстродействие приблизительно на 25 /о.

Формула изобретения

Устройство для сопряжения оперативной памяти с процессором и каналами вводавывода, содержащее блок буферной памяти, адресный вход которого соединен с первым выходом первого регистра адреса процессора, регистр записываемой информации, первый, второй входы и выход которого соединены соответственно с первым, вторым входами устройства и информационным входом блока буферной памяти, регистр считанной информации, первый, второй входы

689439

1

11

il ! I

L Ь

Составитель Ф. Шагиахметов

Техред И. Заболотнова

Корректор С. Файн

Редактор Ахмедова

Заказ 19/27 Изд. № 107 Тираж 730 Подппс ое

НПО «Поиск» Государственного комитета СССР по делам изобретений и открытий113035, Москва, 7К-35, Раушская наб., д. 4/5

Тип. Харьк. фил. пред. «Патент» и первый, второй выходы которого соединены соответственно с третьим входом устройства, с выходом блока буферной памяти, с первым выходом устройства и с третьим входом регистра записываемой информации, 5 коммутатор адреса колонки, выход которого соединен с адресным входом блока хранения адресов, коммутатор адреса ряда, выход которого соединен со входом первого регистра адреса процессора и с первым вхо- 10 дом схемы сравнения, первый блок приоритета, первый, второй входы и первый выход которого соединены соответственно с четвертым, пятым входами и со вторым выходом устройства, причем второй выход пер- 15 ваго блока приоритета соединен с управляющими входами коммутаторов адресов ряда и колонки, первые кодовые входы которых соединены с третьим выходом устройства, а выход блока хранения адресов со- 20 единен со вторым входом схемы сравнения, отличающееся тем, что, с целью повышения быстродействия, в него введены коммутатор адреса процессора, коммутатор адреса канала, регистр адреса оперативной 25 памяти, второй регистр адреса процессора, второй блок приоритета, триггер и элемент

ИЛИ, причем шестой вход устройства является входом второго регистра адреса процессора, выход которого соединен со вторы- 30 ми кодовыми входами коммутаторов адресов ряда и колонки, первый, второй входы и первый, второй выходы регистра адресаоперативной памяти соединены соответственно с выходом коммутатора адреса процессора, с выходом коммутатора адреса канала, с третьим выходом устройства и с информационным входом блока храненияадресов, кодовые входы коммутаторов адресов процессора и канала соединены соответственно со вторым выходом первого регистра адреса процессора и с седьмым входом устройства, пятый и восьмой входы устройства через элемент ИЛИ соединены с управляющим входом коммутатора адреса канала и с первым входом второго блока приоритета, первый выход которого является, четвертым выходом устройства, второй выход второго блока приоритета соединен с управляющим входом коммутатора адреса процессора и с одним из входов триггера, другой вход и выход которого соединены соответственно с выходом схемы сравнения. и со вторым входом второго блока приоритета.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР № 455345, кл. G 06 F 13/00, 1974.

2. Авторское свидетельство СССР № 495659, кл. G 06 F 3/04, 1975.

3. Патент Великобритании ¹ 1370219,, кл. G 4 А, 1974 (прототип).