Регулятор частоты

Иллюстрации

Показать всеРеферат

Q A-@ -"4" N K 690457

Союз Советских

Социалистииеских

Республик

ИЗОбРЕТЕН ИЯ (61) Дополнительное к авт. свид-ву— (22) Заявлено 06.06.77 (21) 2493579/18-24 с присоединением заявки ¹â€” (23) Приоритет— (51) М Ki

G 05 D 1/00

G 05 D 13/62

Государственный ноинтет

СССР оо делам нзооретеннй н отнритнй

Опубликовано 05.10.79. Бюллетень ¹ 37

Дата опубликования описания 15.10.79 (53) УДК 546.614 (088.8) (72) Ав гор изобретения

Д. А. Пластун (?1) Заявитель (54) РЕГУЛЯТОР ЧАСТОТЫ

Изобретение относится к области автоматического регулирования и может быть применено в системах регулирования с частотно-импульсной формой входного сигнала.

Известны регуляторы частоты вращения газотурбинных двигателей (1), (21, построенные на базе струйных элементов и содержащие датчик и задатчик частоты, вычитатель частот и реверсивное исполнительное устройство.

Ближайшим по технической сущности к изобретению является регулятор частоты (3), содержащий датчик и задатчик частоты, подключенные к входам вычитателя частот, первый выход которого соединен с управляющим входом исполнительного блока, выход которого соединен с входом датчика частоты.

Недостатком таких регуляторов является снижение их быстродействия при уменьшении отклонения входных частот от заданных значений.

Это связано с тем, что при изменении отклонения частоты на входе регулятора изменяется разностная частота управляющего воздействия. Диапазон изменения разностной частоты управляющего воздействия простирается от частоты задатчика при HBчальных больших отклонениях входных сигналов до «нулевых» частот при малых отклонениях установившегося состояния. Наиболее сложными для отработки являются крайние участки частотного диапазона. Так при отработке «нулевых» или близких к ним частот диапазона снижается быстродействие регулятора, зависимое от частоты управляющего воздействия. При отработке высоких частот имеют место пропуски импульсов вотработке интегрирующего привода исполнительного устройства.

Целью изобретения является расширение диапазона регулирования регулятора.

Эта цель достигается тем, что предложенный регулятор содержит умножитель частоты и ограничитель частот, выход которого соединен с первым входом умножителя частоты, второй вход которого подключен к второму выходу вычитателя частот, первый выход — к входу исполнительного блока, а

20 вторые выходы — к входам ограничителя частот. Кроме того, умножитель частоты, содержит блок управления, элемент И, счетчик. блок памяти, первый и второй делители частоты и генератор опорной частоты, вы690457

Формула изобретения ход которого подключен к входу перво о делителя частоты и входу второго делителя частоты, выход которого подключен к входу счетчика, первый выход которого подкл1счен к входу блока памяти, а вторые выходы — к соответствующим вторым выходам умножителя частоты, выход которого соединен с выходом первого дел>1тсля частоты, управляющий вход которого соединен с выходом блока памяти. Управляющий вход блока памяти соединен с выходом элемента И, первый вход которого соединен с первым входом умножителя частоты, а второй вход — с первым выходом блока управления, второй выход которого подключен к управляющему входу счетчика и соответствующему BTop;)му выходу умножителя частоты, а вход — к второму входу умножителя частоты.

Эта цель достигается также тем. что ограничитель частот со(ержит первый элемент И и последовательно соединенные зторой элемент- И, элемент ИЛИ и триггер, ВЫХОД КотОРОГО IIO (K.t Ê) ЧС и K БЫ ХОЛУ ОГРЫничителя. частот. а второй вход — к выходу первого элс мента И. Входы э toit(IIToB И и второй(вхо;1 э,:емснт» И,,1И (ocдинены с (:оответствующими вход»ми Ограничителя -1асто).

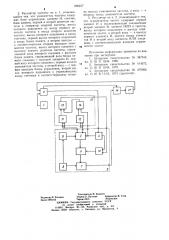

113 tepT(. >K(. изображены структурная схе !3 P(I м,чятОР(1.

1 . улятор содер.кпт .г»д»тчик 1 гстотьt 1, в,;1иты гель час(от 2, ), illto>KIITeль I3(TOTbt 3, BK.1к)ч31Ощии Олок х пр(1 влепи я 4 Гче "чик 5. блок памяти 6, делитель частоты 7, генератор oпорной частоты 8, делитель чclcToòы 9 и .).I(. tetIT И 10. Рсгулятор содержtti также эдеме)ггы И 11 и 12, триггер 1.3 с раздели гельными вхо.ными и элемент ИЛИ 14, образующие ограничитель частот 15. и испол н и тел 1.н ы и бл О к 16.

Рсгулятс)р работает следующим образом.

И.")пу,1ьсы с зы t»TЧпка it»CTOThl 1 II 13T31к» 1астоты 17 Объекта регулирования пост> пы)от на в>3>д вычитателя частот 2. на выходе которого выделяются импульсы разностной частоты. Вычитатель частот 2 формирует знак рыз)юс пюй частоты, который подается Н» реверсивный вход исполнительного блок» 16.

Импульсы рызностной частоты поступают на блок управле(п1я 4, умножитель 3, на Bblходе которого с 1)риходом квждoio импульса формирук>тся два разнесенных по времени коротких импульса.

Первый из этих импульсов поступает на вход блока памяти 6 через элемент И 10 для записи кода, накопленного счетчиком 5.

Второй импульс поступает непосредственно на шину «сброс» счетчика 5 и возвращает его в нулевое состояние.

На счетный вход счетчика 5 начинают поступать импульсы с выхода делителя частоты 9, а на входуправляемого делителя 7 —— импульсы с генератора опорной частоты 8.

Код, записанный в блок памяти 6, управляет коэффициентом деления делителя 7. Но l $

1$

$0

$$

4S

$$ поскольку на управляющем входе делителя

7 записан код числа, пропорционального периоду разностной частоты, на его выходе формируются импульсы разностной частоты, умноженной на коэффициент, равный коэффициенту деления делителя 9.

Для ограничения разностной частоты использу)отся tB3 мно(овходовых элемента И !

1 и 12, соединенные вхо сами с разрядами счетчика 5 и отвечающие верхнему и нижнему llopol частот соответствешю. Выходы .>земо(пов 11, 12 соединены с триггером 13 непосредственно через .элемент ИЛИ 14.

При ныко1(пении на счетчике 5 числа, п ревы ш )tot tlåão нижний пороговый период, на 1)11хо;1 элемента 11 поступает импульс, который переводит триггер 13 в положение, ()TKphli3c1loIll(с элемент И !О тля прохода имн) льсы с блок;I управления 4 на запись в 0;IOK 113 itH1 H 6.

При накоплении 113 счетчике 5 за период разностнои IcToTht числа, меньше чем нижний порог,или большего, чем верхний. триггер 13 не с>гкрывает элемент И 10 к моменту прихода ны него импульса с блока управления 4. В результате делитель 7 формирует частоту по периоду, зафиксированному блоком 6 в предыдущем периоде.

Если на счетчике 5 накоплено число, отвечающее рабочему диапазону умножителя 3, триггер 13 через элемент 14 возвращается в исходное состояние импульсом с блока управления 4, который подается на шину «сброс» счетчика 5.

Таким образом, умножение разностной частоты и ограничение ее диапазона позволяет )ювысить качество регулирования, оптимальным ооразом выбрать диапазон отклонения частот.

Кроме того, схема ограничения частот может быть использована для надежного контроля отклонения регулируемого параметра путем использования импульсных выходов многовходовых элементов И 11 и 12, что позволяет организовать в регуляторе встроенный контроль.

1. Регулятор частоты, содержащий датчик и задатчик частоты, подключенные к входа M вычитателя частот, первый выход которого соединен с управляющим входом исполнительного блока, выход которого соединен с входом датчика частоты, отличаю(г(ийся тем, что, с целью расширения диапазона регулирования, он содержит умножитель частоты и ограничитель частот, выход которого соединен с первым входом умножителя частоты, второй вход, которого подключен к второму выходу вычитателя, первый выход — к входу исполнительного блока, а вторые выходы — — к входам ограничителя частот.

690457

Составитель И. Буневич

Редактор Л, Утехина Техред О. Луговая Корректор Н. Стец

Заказ 5965/45 Тираж 1015 Подписное

ЦН И И П И Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал П ПП в Патента, г. Ужгород, ул. Проектная, 4

2. Регулятор частоты по п. 1, отличающийся тем, что умножитель частоты содержит блок управления, элемент И, счетчик, блок памяти, первый и второй делители частоты и генератор опорной частоты, выход которого подключен ко входу первого делителя частоты и входу второго делителя частоты, выход которого подключен к входу счетчика, первый выход которого подключен к входу блока памяти, а вторые выходы— к соответствующим вторым выходам умножителя частоты, выход которого соединен с выходом первого делителя частоты, управляющий вход которого соединен с выходом блока памяти, управляющий вход блока памяти соединен с выходом элемента И, первый вход которого соединен с первым входом умножителя частоты, а второй вход — с первым выходом блока управления, второй выход которого подключен к управляющему входу счетчика и соответствующему второму выходу умножителя частоты, а вход — к второму входу умножителя частоты.

3. Регулятор по п. 2, отличающийся тем, что ограничитель частот содержит первый элемент И и последовательно соединенные второй элемент И, элемент ИЛИ и триггер, выход которого подключен к выходу ограничителя частот, а второй вход — к выходу первого элемента И, причем входы элементов И и второй вход элемента ИЛИ соединены с соответствующими входами ограничителя частот.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство № 387342, кл. G 05 D 13/44, 1969.

2. Авторское свидетельство М 414572, кл. G 05 D 13/44, 1970.

3. Авторское свидетельство № 479082, кл. G 05 В 11/16, 1973 (прототип).