Преобразователь двоичного кода в двоично-десятичный

Иллюстрации

Показать всеРеферат

Союз Советских

С х

«ii 690474 оци алис тически

Республик

О Л И 6-А k: И Е

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВМДЕТЕЛЬСТВУ (61) Дополнительное к авт. саид-ву-(22) Заявлено 20.06.77 (21) 2497582(18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл .

G 06 F 5/02

Гесудерстееннмй еемвтет

СССР ее дехем нзе5ретеннй в етнрвтнй

Опубликовано 05.10.79. Бюллетень № 37

Дата опубликования описания 15.10.79 (53) УДК 681.325 (088.8) (72) Автор изобретения

М. Г. Дубров (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА

В ДВОИЧНО-ДЕСЯТИЧНЫЙ

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в устройствах для преобразования кодов.

Известно устройство для преобразования двоичного кода в двоично-десятичный, содержашее последовательный сумматор, регистр, формирователь эквивалентов и распределитель 11) . Однако эти преобразователи имеют невысокое быстродействие, так как в них осуществляется последовательный анализ и обработка разрядов двоичного числа.

Наиболее близким к изобретению является преобразователь двоичного кода в двокчно-десятичный, содержащий первый счетчик, комбинационный сумматор, регистр, информационные входы которого соединены с выходами комбинационного сумматора, и блок управления вычитанием, входы которого соединены с выходами регистра и входами «сложение» комбикационного сумматора, первый выход блока управления вы. читанием соединен с первым входом «вычитание» комбинационного сумматора, второй выход соединен со вторым входом «вы. читание» (21. Кроме того, известный пре

2 образователь содержит анализатор знака результата, вход сложения в сумматоре, регистр результата и коммутатор.

Недостатком этого устройства является относительно невысокое быстродействие, поскольку в нем производится вычитание двоичного эквивалента только одного десятичного разряда и возможны ошибочные шаги в алгоритме преобразования.

Целью изобретения является повышение быстродействия преобразовател я за счет совмещения обработки разных разрядов и устранения ошибочных шагов в алгоритме преобразования.

Это достигается тем, что йреобраэователь содержит второй счетчик, управляюшие входы первого и второго счетчиков соединены с первым и вторым выходами блока управления вычитанием соответственно, счетные входы обоих счетчиков соединены с шиной тактовых импульсов и входом записи регистра, третий выход блока управления вычитанием соединен с шиной монца преобразования.

Кроме того, в предлагаемом преобразователе блок управления вычитанием содержит первую и вторую схемы сравнения, входы

6с)! „174 когорых соединены со вхо Ями блока у((ран лсния вычитяни M, элемент !(, входы ко!Орого соединены с (iepBbfMH выходами первой и второй схем сравнения соответственно, вторые выходы первой и второй схем сравнсНИЯ СОЕДИ(1<Н(Ь! С ПЕ!)BblM И BTOPhfM ВЫХОЛЯМИ блока управления вычитанием соответств=нно, выход элемента !.(Соединен с третьим выхолом блока управления вычитание>".

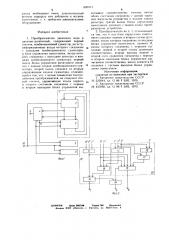

На фиг. 1 приведена блок-схема ripen(аразователя; Н3 фИГ. 2 — - B3pH311T pe3JIH33ции блока управления вычитанием лля и:.)еобразования трехзаряднh х лесятичных чис<. л.

Преобразователь содержит накаплива(ощий сумматор 1, состоящий из )eãHñòэа 2 и комбинационного сучматоря 3>, бл< к 4 управления вычитанием, счетч<: ч ";, 6, "".ыходь(7, 8 б, lок(1 4, (инну 9 и );, -,-. преобразования и шину 10 raf

Блок 4 построен из логических элемснтоь

И, !И 1--- 5 элементов И 6 -18 и содер)к!(т

< х< м(>1 срЯBнеll!tя 9 и 0.

Вь!ход регH<:Tpf(2 <.ocÄtftficн с входом слыга.-мого комбинационного сум мыто!;3 3 и с входом блика 4. Выходы 7, 8 блока 4

<. Ol>;tHfieHh! Со ВХО. 13MH ВЫЧИТЯНИЯ ПСРI>OH второй константы комбинационного ((яторя 3 и с управляющими входами счетчиков 5, 6. Счетные входы с !етчиков 5, 6 и чправля!Ощий вход регистры 2 соединены с ыиной 10 тактовых импульсов.

Г!ри((циц работы преобразователя осноВя l! н3 Бlяч (!та ни и из дВОичнОГО числя дБОи ч1!ЫХ ЭКВИВЯЛЕНТОВ СТЕ(1ЕН<.И ДЕСЯТИЧНОГО 1 (Сля. ()ля рассматриваемого примера преобразование трехразрядных десятичных ч I<:e» нз исходного двоичного числа вычитаются двоичные коды чисел сТо и десять. В ч: ырехразрядных двоичных счетчиках осуществляется полсчет количества вычтенных сэтен и десятков. Как только результат операции вычитания станет меньше десяти, преобразование заканчивается.

П реобразов ате чь работает следую(ци м образом.

В исходном состоянии в регистре 2 записа: но преобразуемое двоичное число, двоичкые счетчики 5, 6 установлены в «О». Код, запи; санный в регистре 2, анализируется в блоке 4.

Если анализируемый код содержит «сотки», появится потенциальный сигнал ка выходе 7 блока 4, если содержит «десятки» вЂ” появится сигнал на выходе 8. Сигналы на выхсдах

7, 8 могут присутствовать одновременно.

Сигнал с выхода 7 блока 4 разрешает счет в счетчике 6 и поступает в виде двоич((ого кода числа сто (1100!00) на вторые вхэды комбинационного сумматора 3, а сигнал с

1;ых<эля 8 разрешает счет в счетчике,5 и

no(TQI13eT н3 вторые входы суMMBTop 1 3 в виде коля числа десять (1010). На выходе сумматора 3 имеется код разности содержимого регистра 2 и кодов ня вторых его входах. С приходом тактового импульса в

O If. T-I HKH ). !) tO<)fI BHT< . и (« С! ((((РИСVT<. TB) ют разрещякпцис поте!щиалы), а результат опс рации Bf f IHт яни(! за ниц!етс H в регисгр 2.

Операции вычитания будут повторяться до тех пор, пока солержимое регистра 2 не будет мещ н!с десяти. при этом в счетчиках 5, 6 осуществляется подсчет вычтенных сотен и десятков: в счетчике 6 фиксируется число сотен, в счетчике 5 -- число десятков. Как только содержимое регистра 2 станет меньше десяти, появится сигнал «конец преобразования» на выхо;(е 8 блока 4, а в регистре 2 будет зафиксировано число единиц двоичнодесятичного числа. Операция вычитания сотен и десятков осуществляется одновременно: в зависимости от содержимого регистра 2 в каждом такте из него булет вычтен и двоичный кол числа сто, десять, или числа сто десять, нри этом добавится единица или только в счетчик 6 или в оба счетчика 5, 6 одновременно. Так, напри((ер, <испо 683 будет пр< Обр(IЗОВЯ!10 за вос:. Мь т;.>1:.T<)B, npH этОм в каждом из первых ц ести тактов будет вы;итяться !И<= (о cTo Чесять, я в последних

itBó.«число десять. В блоке 4 осуществляетс,i анализ всех разрядов преобразуемого числа.

Наличие на входах единичного значения одного из разрядов (— - 9) (веса 28, 256.

5! 2) свидетельствует о том, что анализируемое число содержит <сотни», об этом жс свидетельствует одновременное наличие едиf(HafioIo значения разрядов 5 — 6 и одного из разрядив 2 — -4. В этих случаях появится сигнал на выход< 7.

О наличии в 3!(3.(HçHðóeìîM числе десятков свидетельст(<>foT разряды 4 — 9 или одновременное присутствие елиничного значения разряды 3 (вес 8) и одного из разрядов 1--9 или одновременное присутствие единичного значения разряда 3 (вес 8) и одного из разрядов — 2 (веса 4,2) . В этих случаях появляется сигнал на,выходе 8.

Анализ всех разрядов осуществляеTcB одновременно, и сигналы ка вь<ходах 7, 8 могут присутствовать одновременно. Если анализируемое число меньше десяти, отсутствуют сигналы на выходах 7, 8, появляется сигнал па выходе элемента И 18 и сигнал

«конец преобразования» на выходе блока 4.

Реализация блока 4 на комбинационных схемах позволяет повысить тактовую частоту, т. е. повысить быстродействие преобразователя в пределах частотных возможностей элементов.

Время преобразования в предлагаемом преобразователе меньше, чем в известных тяк как вычитание всех степеней десятичного числа осуществляется одновременно. Кроме того, предлагаемое устройство проще в реализации, так как в нем отпадает необходи- . мость анализа знака остатка после каждой операции вычита ния и нет необходимости в восстановлении операнЛа при отрицательном знаке остатка. Для восстановления опе690474

Формула изобретения

ЦНИИПИ Заказ 5967/44 Тираж 786 Подоисиое

Филиал ППП ° Патента, г. Ужгород, ул. Проектная. 4

3 ранда необходимо иметь дополнительный регистр операнда или добавлять к остатку вычитаемое, т. е. требуется дополнительное оборудование.

I. Преобразователь двоичного кода в двоично-десятичный, содержащий первый счетчик, комбинационный сумматор, регис р, информ ационные входы которого соеди иены с выходами комбинационного сумматора, и блок управления вычитанием, входы которого соединень1 с выходами регистра и входами комбинационного сумматора, первый выход блока управления вычитанием соедине и с первым входом комби национного с умматора, второй выход соединен со вторым управляющим входом сумматора, отличающийся тем, что. с целью повышения быстродействия преобразователя, он содержит второй счетчик, управляющие входы первого и второго счетчиков соединены с первым и вторым выходами блока управления выЬ читанием соответственно, счетные входы обоих счетчиков соединены с шиной тактовых импульсов устройства и входом записи регистра, третий выход блока управления вычитанием соединен с шиной конца преобразования устройства.

2. Преобразователь Ilo и. 1, отличакниийся тем, что в неM блок управления вычитанием содержит первую и вторую схемы ср;;внения, входы которых соединены со входами блока управления вычитанием, элемент И, входы которого соединены с первыми выходами первой и второй схемы сравнения соответственно, вторые выходы первой и второй схем сравнения соединены с первым и вторым выходами блока управления вычитанием соответственно, выход элемента И соединен с третьим выходом блока управления вычитанием.

Источники информации. принятые во внимание при экспертизе

i. Авторское свидетельство СССР

% 525944, кл. G 06 F 55//0022, I975.

2. Авторское свидетельство СССР № 437069, кл. G 06 F 5/02, I973.