Устройство для умножения п-разрядных двоичных кодов

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву-(22) Заявлено 29.09.76 (21) 2409122/18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл .

G06F 7/39

Гасударственный квмнтет

СССР вв делам нзвбрвтвннк н открытей (53) УДК 681.325 (088.8) Опублчковано 05.10.79: Бюллетень № 37

Дата опубликования описания 15.10.79 (72) Авторы изобретения

В. Г. Чачанидзе, Г. Г. Асатиани, T. О, Кублашвили, A. Н. Вепхвадзе, Л. В. Скобелева, О. Г. Смородинова и Р. 3. Мирианашвили

Ордена Ленина институт проблем управления (71) Заявитель (54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ

ПОСЛЕДОВАТЕЛЬНЫХ tt.-РАЗРЯДНЫХ

ДВОИЧНЫХ КОДОВ

Изобретение относится к области вычислительной техники и предназначено для умножения двух синхронно поступающих в последовательном дополнительном коде чисел, в которых знак содержится вп -ом разряде и сначала поступают младшие разряды.

Известно устройство для умножения двух синхронно поступающих в последовательном прямом коде чисел, в которых знак содержится sn-оя разряде и сначала поступают младшие разряды (11. I0

Известное устройство, которое осуществляет умножение за два такта, содержит сдвиговые регистры множимого и множителя, распределитель, статический регистр, сдвиговый регистр, а также элементы И и последовательные одноразрядные сумматоры.

Наиболее близким техническим решением к изобретению. является устройство для умножения двух синхронно поступающих последовательным прямым кодом чисел, в которых знак содержится в и -ом разряде и сначала поступают младшие разряды )2I, содержащее регистр сдвига множимого, регистр сдвига множителя, выход которого соединен со входами (q — 1) элементов И первой группы, (2)-разрядный распределитель, каждый т.-й разряд которого соединен через (1 + )-й элемент И первой группы со входом (I + ) -разряда (n — I ) -разрядного регистра, первый разряд которого через первый элемент И первой группы подключен к шине управления, которая соединена со входом (n — — 2) -разрядного распределителя,, (n — 2) -разрядный сдвиговый регистр, выход -го разряда (a — 1) -разрядного регистра и выход (1 — 1) -го разряда (n — 2)-разрядного сдвигового регистра соединены со входами

1-ro элемента И, (n -- E ) элементов И второй группы, а выход первого разряда (п — l)разрядного регистра и вход (n — 2)-разрядного сдвигового регистра подключены ко входам первого элемента И второй группы.

Выходы (2n — 1) -ro и 2к-го элементов И второй группы (1(= 1,2..., - - — l) соединены со входами K -ro одноразрядною сумматора первои группы. Выходы (2т — 1)-го и 2а-го одноразрядных сумматоров первой группы ((= !, 2,..., g — I) соединены со входами

)-го одноразрядного сумматора второй группы. Выходы последнего одноразрядного сумматора первой группы и последнего поразрядного элемента И второй группы соединеHbl со входами последнего одноразрядного сумматора второй группы. Выходы одноразрядных сумматоров (j - — 1) -й группы (== l, 2,..., log и ) соединены со входами последовательного одноразрядного суммато.ра j -й группы.

Низкое быстродействие таких устройств обусловлено тем, что при умножении поступающих в последовательном допол кительном коде чисел требуется их преобразо зание в прямой код. т. е. требуется дополнительно

И тактов.

Целью изобретения является повышение быстродействия.

Эта цель достигается тем, что п предложенное устройство введены доно.нчтельные элементы ИЛИ, И, НЕ, задер>.:; и дополнительные одноразрядные сумматоры. Выход регистра сдвига множимого соединен с одним из Входов первого дополнительного элемента И, другой вход которого через первый элемент задержки подключен к выходу (a--- 2) щ разрядного распрсдечителя, а выход — I(одHoMv нз входов первого элемента ИЛИ, другой вход которого соединен с выходом второго элемента ИЛИ, вход которого соединен с выходом первого элемента ИЛИ, а выход— с одним из входов третьего элемента ИЛИ, другой вход которого подключен к выходурегистра сдвига множимогo, а выход ,ко входу (n -- 2)-разрядного сдвигового регистра. В ыход регистра сдвига множителя соединен с одним из входов второго элемента

И, другой вход которого подключен к выходу .первого элемента задержки, а выход -- к одному из входов четвертого элемента ИЛИ, другой вход которого соединен с выходом пятого элемента ИЛИ, вход которого соединен с выходом четвертого элемента ИЛИ, М а ВыхОд — с Одним из входов третьего элемен а И, другой вход которого подключен к выходу первого элемента задержки, а выХОД вЂ” К ОДНОМ j ИЗ ВХОДОВ ПЕРВОГО ДОПОЛнительного, одноразрядного сумматора, другой вход которого соединен с выходом :етвертого дополнительного элемента И, один из входов которого соединен с выходом пятого элемента ИЛИ, а другой вход †- с выходом элемента НЕ, вход которого через второй элемент задержки подключен к вы- 4з ходу (n-- 2) -разрядного сдвигового регистра, Выход первого дополнительного одноразрядного сумматора соединен с одним из входов второго дополнительного одноразрядного сумматора, другой вход которого соединен с выходом третьего последовательного одноразрядного сумматора, а выход подклю"еп к выходной шине устройства. Один из входоп третьего дополнительного одноразряднс го сумматора соединен с выходом одноразрядного сумматора 1.-й группы, другой вход — — л с выходом пятого элемента И, один из входов которого подключен к выходу последнего разряда (n — 2) -разрядного распреде,лителя, 4 а другой вход — - к выходу одноразрядного сумматора j. -й группы.

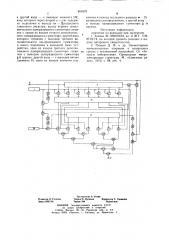

Функционал ьная схема устроиства для умножения последовательных и -разрядных кодов для случая n = 8 представлена на чертеже.

Устройство содержит регистр сдвига множителя 1, элементы И 2 — -8 первой группы; (e.— 2) -разрядный распределитель 9, (n — 1)разрядный статический регистр 10, шину управления 11, (n — 2) -разрядный сдвиговый регистр 12, элементы И 13 — 18 второй группы, последовательные одноразрядные сумматоры первой группы 19 — 22, последовательнь е одноразрядные сумматоры второй группы 23, 24, последовательный одноразрядный сумматор третьей группы

25, регистр сдвига множимого 26, дополнительные элементы И 27, элементы задержки 28, элементы ИЛИ 29 — 3!; дополнительный одноразрядный сумматор 36, дополнительные элемент ы НЕ 38, элементы задержки 39, дополнительные одноразрядные сумматоры 40 — 41, входную шину 42 и дополнительный элемент округления 43.

Устройство работает следующим образом.

В исходном состоянии дополнительные коды множителя и множимого размещены соответственно в регистрах сдвига множителя 1 и множимого 26, Из регистров 1 и 26 эти коды подаются младшими разрядами вперед и содержатся вп-ых разрядах кодов.

На первом такте из регистров сдвига множимого подаются младшие разряды множимого и множителя. В этом же такте на шину управления l! подается единичный сигнал, который на первом такте открывает элемент

И 2, на втором такте — элемент И 3, и т. д., а на седьмом такте — элемент И 8, так как на шину управления ll начиная со второго такта, подается нулевой сигнал. В результате за семь таКтов дробная часть кода множителя записывается в статический регистр 10.

Пусть множимое равняется -0,1011019 з((- -)Я вЂ” ), а множитель -0,1100101 (— Я вЂ” ), Тогда из регистра сдвига, множимого 26 подается дополнительный код 1,0100101, а из регистра сдвига множителя 1 — дополнительный код 0,110010l.

На первом такте на выходе элемента

И 2 будет единичный сигнал, который запишется в первый триггер (п —.l)-разрядного регистра 10. На выходе элемента ИЛИ 30 будет нулевой сигнал из-за наличия нулевого сигнала на выходе элемента задержки 28.

В результате на выходе элемента И !9 будет единичный сигнал, который через цепочку одноразрядных сумматоров -20, 23, 25, 41 и 40 проходит на выходную шину 42 устройства, так как на выходах элементов И 13

18, 35, 37 и 43 будут нулевые сигналы.

1Ia ВтОрОм такте на выходе элемента И 3 будет нулевой сигнал, который записывается во второй триггер (п — 1)-разрядного ре690478

Устройство для умножения последовательныхп-разрядных двоичных кодов, содержащее регистр сдвига множимого, регистр сдвига множителя, выход которого соединен со входами (n — 1) элементов И первой группы, (n — 2) -разрядный распределитель, 1$ гистра 10. В первом разряде регистра 12 записывается единица. В результате на выходе элемента И 19 получаем произведения первого разряда множителя на второй разряд множимого (нулевой сигнал}, а на выходе элемента И 13 произведение второго

$ разряда множителя на первый разряд множимого (нулевой сигнал). Далее на выходе сумматора 20 имеем единичный сигнал, который через цепочку сумматоров 23, 25, 41 и 40 проходит на выход 42 устройства.

Далее устройство работает аналогично. IO

На седьмом такте от выхода последнего разряда (v — 2) -разрядного распределителя 9 включается элемент И 43 округления.

При этом на выходе сумматора 36 имеем нулевой сигнал, так как на выходах элементов И 35, И 37 имеем нулевые сигналы

1$ из-за наличия нулевого сигнала на выходе элемента задержки 28, и в сумматорах 40 и 42 перенос равняется нулю. В результате если на седьмом такте на выходе сумматора 25 имеем единичный сигнал, то он запо- зв минается в сумматоре 41 в виде единичного переноса. Начиная с восьмого такта, элемент И 43 округления выдает const 0, и с выхода 42 устройства снимаем значащие разряды умножения.

На восьмом такте на выходе элемента

И задержки 28 будет единичный сигнал. В результате из-за наличия единицы в знаковом разряде множимого элемент ИЛИ 3! вы-. дает const 1:

На пятнадцатом такте устройство выдает зв знак умножения, и на этом работа устройства заканчивается.

Для рассмотречного примера устройство с восьмого по пятнадцатый такт выдает результат умножения в дополнительном коде

1,0111000 (—,®--). При наличии в знаковом

9 3$ разряде множителя единицы, начиная с восьмого такта, элемент ИЛИ 34 выдает 1. В .результате на этом такте от элемента И 35 на вход сумматора 36 подается единица, на другой вход которого из регистра 12 зв через элемент задержки 39 и элементы HE

38 и И 37 подается обратный код множимого.

Таким, образом, устройство осуществляет умножение последовательных доп олн ител ьных и-разрядных двоичных кодов íà 2n — 1

4$ тактов.

Изобретение позволяет повысить быстродействие устройства для умножения последовательных tl -разрядных двоичных ко.дов на и тактов.

$6

Формула изобретения каждый; и разряд которого соединен через (1 + 1)-й элемент И первой группы сс входом (i:+ 1) -го разряда (и — 1) -разрядного регистра, первый разряд которого через первый элемент И первой группы подключен к шине управления. которая соединена со входом (n — 2) -разрядного распределителя, (и — 2) -разрядный сдвиговый регистр, выход

1 -ro разряда (n — 1) -разрядного регистра и выход (i — 1) -ro разряда (n — 2) -разряд--ного сдвигового регистра соединены со входами i -го элемента Vi, (и — } элементов

И второ"группы,,а выход первого разряда (n — 1)-разрядного регистра и вход (и — 2)разрядного сдвигового регистра подключены ко входам первого элемента И второй группы, причем выходы (2к — 1) -го и 2к-ro элементов, И второй группы (к = 1, 2, ..., — — 1) соединены с о входами к - го одноразрядного сумматора первой группы, выходы (2 — !)го и 2q-го одноразрядных сумматоров первой грчппы (с! = 1, 2, ..., — — 1) соединены с0 входами Q-го одноразрядного сумматора второй группы, выходы последнего одноразрядного сумматора первой группы и последнего элемента И второй группы соединены со входами последнего одноразрядного сумматора второй группы, выходы одноразрядных сумматоров (j.— 1)-й группы (> = 1, 2, !

ogden) соединены со входами однораз. рядного сумматора !.-й группы, отличающееся тем, что, с целью повышения быстродействия, ь него введены дополнительные элементы ИЛИ, И, НЕ, задержки н дополнительные одноразрядные сумматоры, выход регистра сдвига множнмого соединен с одним из входов перво,о элемента И, другой вход которого через первый элемент задержки подключен к выходу (n — 2) -разрядного распределителя, а выход — к одному из входов первого элемента ИЛИ, другой вход которого соединен с выходом второго элемента

ИЛИ, вход которого соединен с выходом первого элемента ИЛИ, а выход — с одним из входов третьего элемента ИЛИ, другой вход которого подключен к выходу регистра сдвига множимого, а выход — к входу (и — 2) -разрядного сдвигового регистра, вы..-.од регистра сдвига множителя соединен с одним из входов второго элемента И, другой вход которого подключен к выходу первого элемента задержки, а выход — к одно- . му из входов четвертого элемента ИЛИ, другой вход кот . ого соединен с выходом пятого элемента ИЛИ, вход которого соединен = выходо,м четвертого элемента ИЛИ, а выход — c одним из входов третьего элемента И, другой вход которого подключен к выходу первого элемента задержки, а выход — к одному из входов первого дополнительного одноразрядного сумматора, другой вход которого соединен с выходом четвертого элемента И, один из входов которого. соединен с выходом пятого элемента ИЛИ, 690478

8 ключен к выходу последнего разряда 1и--2) разрядного распределителя, а другой вход— к выходу одноразрядного сумматора j -й группы.

7 а другой вход — с выходом элемента НЕ вход которого через второй э;:::ент задерж ки подключен к выходу (n — 2 разрядного сдвигового регистра, выход первого допол нительного одноразрядного сумматора соединен с одним из входов второго дополнительного одноразрядного сумматора, другой вход которого соединен с выходом третьего дополнительного одьоразрядного сумматора, а выход подключен к выходной шине устройства, один из входов третьего дополнительного одноразрядного сумматора =оединен с вь|ходом одноразрядного сумм aòîðà -й группы, другой вход — с выходом пятого элемента И, один из входов которого подИсточники информации, принятые во внимание при экспертизе

1. Заявка № !994659/24, кл. G 06 F 7/39, 07.02.74, по которой принято решение о выдаче авторского свидетельства.

2. Певцов Д. В. и др. Элементарные вычислительные операции в однородных средах с независимой настройкой. Сб. «Вопросы кибернетики». Однородные микроэлектронные структуры. М., кСоветское радио». 1973; с. 88, рис. 4.

Редактор Л. Утекнна

Заказ 5й67 48

Составитель А. Уткин

Текред О. Луговая Корректор A. Грищенко

Тираж 780 Подннсное

ЦН И И ПИ Государственного комитета СССР по делам изобретений и открытий

3 t3035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал П П П а Патенте, г. Ужгород, ул. Проектная, 4