Одноразрядный десятичный сумматор

Иллюстрации

Показать всеРеферат

щс те . ° - ° описАн и-е

ИЗЬВРЕТЕ Н ИЯ

Союз Советских

Социалистических

Республик

N АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 23.07.75 (21) 2159947)18-24 с присоединением заявки №вЂ” (51) М. Кле.

G 06 F 7/50 (23) Приоритет—

Гэсудэфстееп@Ф

СССР в деми имбретеаФ в етхрепев (53) УДК 681.325..5 (088.8) Опубликовано 05.10.79. Бюллетень № 37

Дата опубликования описания 15.10.79 (72) Авторы изобретения

А. А. Чудов н В. B. Блатов (71) Заявитель

,(54) ОДНОРАЗРЯДНЫЙ ДЕСЯТИЧНЫЙ СУММАТОР

Изобретение относится к области цифровой вычислительной техники.

Известны сумматоры двончно-десятичных чисел, которые, однако, не могут быть непосредственно применены для вычитания двончно-десятичных чисел (11.

Известны устройства для сложения, и вычитания двоично-десятичных чисел (2) и

131, содержащие входные и выходные сумматоры, блоки инвертирования кодов и блоки коррекции и формирования межтетрадиых переносов. Недостатками этих устройств является сложность их выполнения.

В качестве прототипа выбран однбразрядный десятичный сумматор, содержащий корректирующий двоичный сумматор, два элемента И и элемент ИЛИ, первый и второй входы которого подключены к выходам первого и второго элементов И, а выход соединен с выходом переноса десятичного сумматора и первым входом первого разряда кор ректирующего двоичного сумматора, выходы которого соединены со вторым, третьим и четвертым разрядами выхода суммы десятичного сумматора 14).

Недостатком такого сумматора является невозможность прямого вычитания десятичных чисел.

Целью изобретения является расширение функциональных возможностей десятичного сумматора, заключающееся в возможности вычитания десятичных чисел.

Для достижения этой цели десятичный сумматор содержит двоичный сумматор-вычитатель н третий н четвертый элементы И, щ выходы которых подкаючены к первым входам соответственно второго и третьего разрядов корректирующего двоичного сумматора, первые входы соединены с выходом элемента ИЛИ, а вторые входы — соответст-. венно с управляющими шинами сложения н вычитания, которые подключены также к управляющим входам двоичного сумматора-вычнтателя, информационные входы которого соединены с входами первого и второго операндов и входом переноса десятичного сумматора, выход первого разряда двоичного сумматора-вычитателя подключен к первому разряду выхода суммы десятично го сумматора, а выходы второго, третьего и

690479 четвертого разрядов подклк>ч-ны ко вторым входам соответственно первого, второго и третьего разрядов корректиру3О3цего э;,воичного сумматора, входы первого элемента И подключе33ьэ к выходам ВторОГО и четвертОГО разрядов, а входы второго элемента 11 к выходам третьего и четвертого разрядов двоичного сумматора-вычитателя, выход переноса которого подключен к третьему входу элемента ИЛИ.

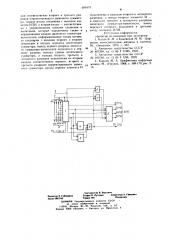

На черте>ке представлена функциональíая схема олноразрядного десятичного сумматора.

Сумматор содержит двоичный Гуммагор;

| вычитатель 1 (четырехразрядныи;:, ) правляющие шины сложения 2 и вьшитания 3, элементы И 4, 5, 6, 7, элеме3Г :„ДИ 8 и корректиру>ощий двоичньэй сумматор 9 (трехразрядный) .

На входы двоичного сумматора-nfl-IHI ателя 1 поступают операнды 3(и В в двои шодесятичном коде и сигнал переноса (заема) из предыдущего разряда.

Управляющие входы сумматора-вьшитаTC lH 1 COCCI» HPHbl C уflpfl BJLHIOI\Lff »»f» III HHBM I i сложения 2 и вычитания 3. Выходы тре-, старших разрядов сумматора-вычитатсля I. соединены со входами элементов И 4 и 5 и входами корректирующего двоичного сумматора 9. Выход переноса (заема) сумматора-вычитателя 1 и выходы элементов И 4 и 5 соединены со входами элемента ИЛИ 8.

Входы элементов И 6,и 7 соедин.-ны с выходом элемента ИЛИ 8 и с yilpaf>.lÿþùèìè шиэ.ами сложения 2 и вычитания 3.

Другие входы корректирующего двоично го сумматора 9 соединены соответственно с выходом элемента ИЛИ 8 и с выходами элементов И 6 и 7.

Младший разряд суммы (разности снимается с выхода сумматора-вычитателя 1, а три старших разряда — с выходов к(>оректирующего сумматора 9.

Десятичный сумматор раб>отает следу(ощим образом.

На вход двоичного сумматора-вычитате ля 1 поступают числа А — — ai, ар, а,, а»

И В вЂ” bi Ь г, (>э, Ь» В дВОИЧНО-дЕСятИЧНОМ коде, сигнал переноеа П1 3 (при сложении чисел А и Б) или сигнал заема 31 3 (при вычиТании чисел А и В). При налички потенциала На управляющей шине сложения 2 происхолит алгебраическое сложение чисел

А + В, а при Has H IHH сигнал а Ha ya pa aif Hioщей шине вычитания 3 — происходит алгебраическое вычитание чисел A --- -В.

При этом с выхода сумматора-вычптателя 1 с3п(Мается соответственно сумма или разность входнь.х чисел в двоичном коде, сигнал переноса, если сумма равна 16-:19, или сигнал заема, если разность отрицательная (В )А). Выхолные сигналы с трех старших разрядов сумматора-вычитателя 1 поступают на элементы И 4 и 5. которые формируют сигналы переноса, если сумма равна 1О --:-15.

Для получения суммы или разности в двоично-десятичном 3(оле 33еобхолимо прибавить к полученному на вь3ходе сумматоравычитателя 1 результату О (0000), если сумма или разность равна Π—:-9, 6(01!0) — если сумма равна 10 —:-19 и 10(1010) — — если разность отрицательна. Для этого используется двоичный трехразрядный сумматор 9, на одни входы которого поступают сигналы 3 (» с трех старших разрядов сумматора-вычитателя 1, а на другие входы — .иола О, 6 или 10.

Младший разряд чисел О, 6 и 10 равен нулю, поэтому он не используется для корректировки двоичнОГО 3(ола. Для формирования трех старп3их разрядов чисел О, 6 и 10 используется сигнал переноса (заема) и сигнал>-.3 управляющих шин 2 и "., 3((эторьгс поступают на входы эл3 ментов И 6 и 7. Число

000 получается, если сип3а 3 переноса П I равен нулю, 01! получается ilpH сложении

Зисел, коглa сигнал 33ереээоса и потенциал на управля>оэцей шине 1 равны единице, и потенциал шины 3 равен нул>о. 10! получается при вычитании чисел, когда сигнал заема 3; и потенциал шины 3 равны единице, а потенциал ц3ины 2 равен нул>о.

Младший разряд SI (rl ) выходного Лвопчно-десятичного числа формируется непосредственно в сумматор(-вь3 Зи" ателе 1, а три старших разряда Sg (I ), S:, (г; ), S» (г») снимаются соответственно с выходов двоичного сумматора 9.

Таким обра-,oì введение дополнительных элементов и связей для корректировки кода с выходя двоичH010 сумматора-вычитателя 1 расширяет эункциональные воэможности десятичного сумматора без существенного его усложнения.

Фор.»(ула изобретения

Одноразрял>»ый десятичный сумматор, содержаш,ий корректирующий двоичный сумматор, два элемента И и элемент ИЛИ, 4 первый и второй входы которого подключены к выходам первого и второго элементов И, а выход соединен с выходом переноса деся пэчного сумматора и первым входом первого разряда корректирующего двоичного сумматора. выходы которого соединены со вторым, третьим и четвертым разрядами выхода суммы десятичного сумматора, отличающийся тем, что, с,целью расширения функциональных возможностей десятичного сумматора, заключак>щемся в возможности вычитания десятичных чисел, десятичнйй сумматор содержит двоичный сумматорвычитатель и третий H четвертый элементы И, выходы которых подключены к первым вхо690479 («p д(.г)

3(rg / S(R j

"Cr (3i) Составнтель В. Ьерезкнн

Редактор Э. Губанакаа Текред О. Лугован Корректор А. Г }яненко

Заказ бво7/46 тара 7iO

Подансвое

ЦН ИИПИ Государственного комнтета СССР по делам нзобретеннй н открытнй

I I3035, Москва, Ж вЂ” 3S, Раушская наб., р. 4/б

Фнлнал ППП ° Патента, г. Ужгород, ул. Проектная, 4 дам соответственно второго и третьего разрядов корректирующего двоичного сумматора, первые входы соединены с выходом элемента ИГПИ, а вторые входы — соответственно с управляющими шинами сложения и вычитания, которые подключены также к управляющим входам- двоичного сумматоравычитателя, информационные входы которого соединены с входами первого и второго операндов и входом переноса десятичного сумматора, выход первого разряда двоичного сумматора-вычитателя подключен к первому разряду выхода суммы десятичного сумматора, а выходы второго, третьего и четвертого разрядов подключены ко вторым входам соответственно первого, второго и третьего разрядов корректирующего двоичного сумматора, входы первого элемента И

-подключены к выходам второго и четвертого разрядов, а входы второго элемента И к выходам третьего и четвертого разрядов двоичного сумматора-вычитателя, выход перенос а которого подключен к третьему входу элемента И,ЧИ.

Источники информации, принятые во внимание при экспертизе

l. Каган Б. М. и Каневский М. М. Цифровые вычислительные машины и системы.

М., «Энергия», 1973. с. 357.

2. Авторское свидетельство СССР № 407309, кл. G 06 F 7/385, 1970.

3. Авторское свидетельство СССР № 393740, кл. G 06 F 7/50, 1970.

4. Карцев M. А. Арифметика цифровых машин. М., «Наука», 1968, с. 168-170, рис. 216.