Запоминающее устройство с выборкой по содержимому

Иллюстрации

Показать всеРеферат

Союз Совет@них

Социалистических

Республик () 690486

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 22.03.77 (21) 2465508/18-24 с присоединением заявки ¹â€” (23) Приоритет— (51) М. Кл .

G 06 F 13/06

Геаударстаанньй номнтат ссср на делам нзабратаннй н аткрытнй

Опубликовано 05.10.79. Бюллетень № 37

Дата опубликования описания 15.10.79 (53) УДК 681.325 (088 8) В. Л. Арлазаров, А. С Варпаховский, А. Ф Волков, А. H. Годунов„

Н. В. Дагурова, Н E. Емельянов, Г. М. Золотухина, В. С. Лихонннский, В. T. Лысиков, В. А. Макаров и Г. К. Сорокин (72) Авторы изобретения (71) Заявитель

Ордена Ленина ттнститут проблем управления (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

С ВЫБОРКОЙ ПО СОДЕРЖИМОМУ

I с

С 3

Изобретение относится к области вычислительной техники.

Известно ЗУ с выборкой по содержимому 11), состоящее из ассоциативных элементов и узла выбора слова. Недостатками такого ЗУ являются повышенная стоимость бита, высокие отношения вывод/схема и мощность рассеяния.

Наиболее близким по технической сущности к изобретению является устройство 12), содержащее матрицу полей памяти с произвольной выборкой, выходы которых соединены с первыми информационными входами соответствующих блоков сравнения, выходы которых соединены со входом сигнала совпадения соответствующих элементов ИЛИ совпадения. Входы маскирования элементов

ИЛИ совпадения каждого столбца матрицы объединены и подключены к соответствующему выходу регистра маски, вход которого подключен ко входу маски устройства, вход признака которого соединен со входом регистра признака, группы выходов которого соединены со вторыми информационными входами блоков сравнения соответствующего столбца матрицы. Выходы элементов

ИЛИ совпадения каждой строки матрицы соединены с соответствующими входами элементов И объединения сигналов совпадения, выходы которых через блок хранения сигналов совпадения соединены со входами блока кодирования приоритета, выходы которого соединены со входами старших разрядов регистра адреса, входы младших разрядов которого подключены к выходам счет- чика адреса, которые соединены с одной группой входов мультиплексора, другая группа входов которого подключена к выхо- дам, младших разрядов регистра адреса.

Выходы старших разрядов последнего соединены со входами дешифратора. Одноименные адресные входы полей памяти с произвольной выборкой объединены и подключены к соответствующему выходу мультиплексора, а управляющие выходы блока управления, режимом соединены с управляющими входами регистра адреса, счетчика адреса, мультиплексора и генератора тактовых импульсов выход которого соединен с импульсным входом элемента И прохождения счетных импульсов, выход которого соединен со счетным входом счетчика адреса.

600486

Формула изобретения

Недостатком т3K0lo ус-,: .йства является низкое быстродействие.

Целью изобретения является повып1ение быстродействия устройства.

Поставленная цель достигается тем, что

Предложенное устройетво содержйт элементы ИЛИ режима поиска по числу полей памяти с произвольной выборкой и элемент

ИЛИ объединения сигналов совпадения, входы которого подключены к выходам элементов И объединения сигналов совпадения, а выход соединен с разрешающим входом элемента И прохождения счетных импульсов и входом блока управления режимом, выход разрешения поиска которого:,. динен со входами разрешения элементо. - :ЛИ режима поиска, выход каждого из которых соединен с разрешающим входом соответствующего поля памяти с произвольной выборкой. Лдресные входы элементов ИЛИ режима поиска каждой строки матрицы обьединсны и подключены к соответствующему выходу дсшифратора.

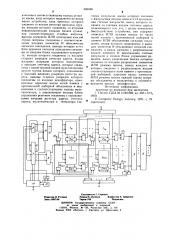

Структурная схема устройства приведена на чертеже.

Устройство содержит полн памяти с произвольной выборкой 1 — Imp, блоки сравнения 2i, — 2>,»>, регистр признака 3, регистр маски 4, блок хранения сигналов совг,адепия 5, блок кодирования приоритета 6, регистр адреса 7, счетчик адреса 8, дешифратор 9, блок управления режимом 10, мультиплексор Il, генератор тактовых импульсов !2, элементы И 13> — 13гп объединения сигналов совпадения, элементы ИЛИ I41i —14 п,совпадения, элементы ИЛИ 15 i — 15пщ режима поиска, элемент ИЛИ 16 объединения сигналов совпадения,- элемент И 17 Ipoхождения счетн > х импульсов.

Устройство работает следующим образом, В режиме поиска по содержимому блок управления режимом 10 устанавливает в нуль счетчик адреса 8 и с помощью мультиплексора 11 подключает выходы счетчика адреса 8 к адресным входам полей JIB Y, ÿòè ! i i -- Im<. Затем блок управления режимом

10 вырабатывает сигнал режима поиска, который через элементы ИЛИ 15| i — 15»щ подается на входы разрешения полей памяти

1 i -- ImtI и запускает генератор 12, импульсы с выхода которого через элемент И 17 подаются на вход счетчика адреса 8. В результате код адреса, лодаваемьш на адресщ> е входы полей памяти I i i — Im», увеличивается на единицу на каждый импульс генератора 12, и на блоки сравнения 2i —

2 >> подаются очередные слова, выбираемые из полей памяти I i t — Imn. На блоки сравнения 2 — 2юд подаются также данные из регистра признака 3 При совпадении данных, хранимых в регистре признака 3 l6

Ф3

26

26

Зь и слова, хранимого в полях памяти I i i — III блоки сравнения 2i i -- 2in вырабатывают сигналы совпадения, которые проходят через элементы ИЛИ 14 i — 14, объединяются элементом И 13, затем проходят элемент

ИЛИ 16 и подаются на вход элемента И 17 прекращая подачу импульсов от генератора !

2 к счетчику адреса 8. В режиме поиска возможно маскирование. Например, можно замаскировать сигналы от блоков сравнения

2i i — - 2e, подав сигналы логической единицы от регистра маски 4 на элементы ИЛИ

14i i — )4щ . После прекращения подачи тактовых импульсов на счетчик адреса 8 на адресных входах полей памяти I i i — Imp фиксируется младшая часть кода адреса.

Может оказаться, что имеет место совпадение нескольких слов, хранимых в ЗУ с данными на регистре признака 3. В результате одновременно вырабатывается несколько сигналов совпадения на выходах элементов

И 13i — - 13m, и в единицу устанавливается несколько индикаторов совпадения, расположенных в блоке хранения сигналов совпадения 5. В этом случае блок кодирования приоритета 6 генерирует код наименьшего значащего двоичного разряда (при этом считается, что входы блока 6 обозначены двоичным кодом). Этот код образует старшую часть кода адреса искомого слова.

Старшая часть кода адреса с выхода блока кодирования приоритета 6 подается для записи в соответствующие разряды регистра адреса 7. По сигналу с выхода элемента

ИЛИ 16 блок управления режимом !0 производит перезапись в регистр адреса 7 младшей части кода адреса из счетчика адреса 8 и старшей части кода адреса с выходов блока кодирования приоритета 6.

ЗУ с.выборкой по содержимому объемом

И слов ло сравнению с ЗУ с произвольной выборкой с единым полем памяти на N слов, но имеющим один блок сравнения, дает в режиме поиска выигрыш в быстродействии в И /n раз, где n — число слов в поле памяти 1 с произвольной выборкой.

Йо сравнению с ассоциативным ЗУ в предложенном ЗУ снижены стоимость бита, отношение вывод/схема и мощность рассеяния.

Запоминающее устройство с выборкой по содержимому. сбдержащее матрицу полей памяти с произвольной выборкой, выходр которых соединены с первыми информационными входами соответствующих блоков сравнения, выходы которых соединены со входом сигнала совпадения соответствующих элементов ИЛИ совпадения, входы маскирования элементов ИЛИ совладения каждого столбца матрицы объединены и под690486

Составнтель Г. Сорокин

Редактор Л. Утекнаа Текред О. Луговая Корректор А. Грнненко

Заказ 6967/46 Тараи 786 Подвнсное

ЦН К КП И Государственного комитета СССР ° по делам изобретений и открытий

I 33036, Москва, ж — 36, Раушская наб., д. 4/6

Филиал П П П к Патента, г. Ужгород, ул. Проектная, 4 ключены к соответствующему выходу регист ра маски, вход которого подключен ко входу маски устройства, вход признака которого соединен со входом регистра признака, группы выходов которого соединены со вторыми информационными входами блоков сравнения соответствующего столбца матрицы, выходы элементов ИЛИ совпадения кам лой строки матрицы соединены с соответствующими входами элементов И объединен нни сигналов совпадения, выходы которых ««;.1ез блок хранения сигналов совпадения соединены со входами блока кодирования приоритета, выходы которого соединены со входами старших разрядов регистра адреса, входы младших разрядов которого подключены к выходам счетчика адреса, которые соединены с одной группой входов мультиплексора лругая группа входов которого полключена к выходам младших разрядов регистра адреса, выходы старших разрядов которого соединены со входами дешифратора, одноименные адресные входы полей памяти с произвольной выборкой объединены и подключены к соответствующему выходу мультиплексора, а управляющие выходы блока управления режимом соединены с управляющими входами регистра адреса, счетчика адреса, мультиплексора и генератора тактовых импульсов, выход которого соединен с импульсным входом элемента И прохождения счетных импульсов, выход которого соединен со счетным входом счетчика адреса, отличающееся тем, что, с целью повышения быстролействия устройства, оно солержит элементы ИЛИ режима поиска по числу полей памяти с произвольной выборкой и элемент ИЛИ объединения сигналов совпадения, входя которого подключены к выходам элементов И объединения сигналов совто падения, а выход соелинен с разрешающим входом элемента И прохождения счетных импульсов и входом блока управления режимом, выхол разрешения поиска которого соелинен со входами разрешения элементов

ИЛИ режима поиска, выход каждого из которых соединен с разрешающим входом соответствующего поля памяти с произвольной выборкой, алресные входы элементов

ИЛИ режима поиска каждой строки матрицы объединены и подключены к соответстзо вующему выходу дешифратора.

Источники информации, принятые во внимание при экспертизе

1. Патент США № 3.540.002, кл. 340-172.5, 1970.

2э

2. Computer 0esign, January, 1971, с. 79 (прототип) .